## **ADVANCE INFORMATION**

September 1995

# NS486™SXF Optimized 32-Bit 486-Class Controller with On-Chip Peripherals for Embedded Systems

## **General Description**

The NS486SXF is a highly integrated embedded system controller incorporating an Intel486TM-class 32-bit processor, all of the necessary System Service Elements, and a set of peripheral I/O controllers tailored for embedded control systems. It is ideally suited for a wide variety of applications running in a segmented protect-mode environment.

## **Key Features**

- 100% compatible with VxWorks®, VRTX®, QNX®, pSOS+TM, and other popular real-time executives and operating system kernels

- Intel486 instruction set compatible (protected mode only) with optimized performance

- Operation at 25 MHz with 5V supply

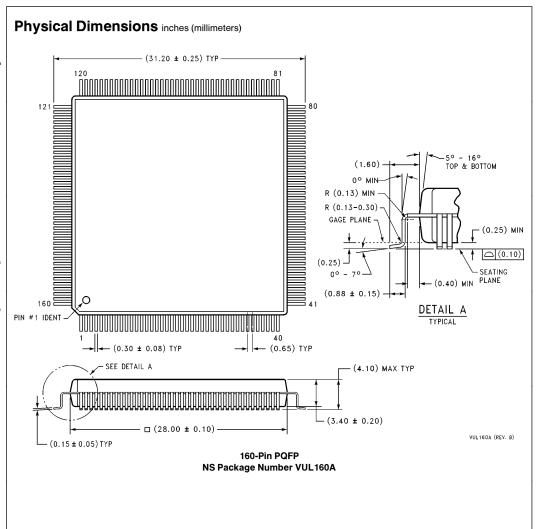

- Low cost 160-pin PQFP package

- Industry standard interrupt controller, timers, real time clock, UART with IrDA v1.0 (Infrared Data Association)

- Intel 82365 compatible PCMCIA interface

- Protected WATCHDOG™ timer

- Optimized DRAM controller (Supports two banks, up to 8 MBytes each)

- Up to nine versatile, programmable chip selects

- Glueless interface ISA-type peripherals

- Arbitration support for auxiliary processor

- Four external DMA channels (max. transfer rate of 25 MByte/sec @ 25 MHz) support many transfer

- High performance IEEE 1284 (ECP) Bidirectional Parallel Port

- MICROWIRETM/MICROWIRE/PLUSTM/Access.bus synchronous serial interfaces

- LCD Controller for monochrome supertwist Liquid Crystal Displays up to 480 x 320

- Reconfigurable I/O: Up to 29 I/O pins can be used as general purpose bidirectional I/O lines

- Flexible, programmable, multilevel power saving modes maximize power savings

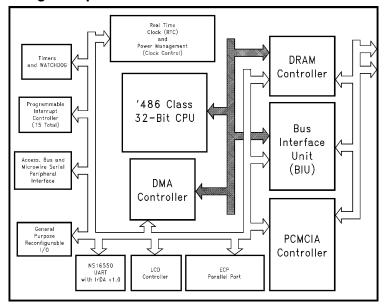

## **NS486SXF Single-Chip Embedded Controller**

TL/EE/12514-1

TRI-STATE® is a registered trademark of National Semiconductor Corporation NS486™, WATCHDOG™, MICROWIRE™ and MICROWIRE/PLUS™ are trademarks of National Semiconductor Corporation

Intel486™ is a trademark of Intel Corporation.

QNX® is a registered trademark of QNX Software Systems, Inc. VRTX® is a registered trademark of Microtec Research, Inc.

VxWorks® is a registered trademark of Wind River systems, Inc. pSOS+™ is a trademark of Integrated Systems Inc. PowerPack is a registered trademark of Microtek International.

## **Table of Contents**

### 1.0 SYSTEM OVERVIEW

- 1.1 NS486SXF System Overview

- 1.2 32-Bit Processor Core

- 1.3 System Service Elements

- 1.3.1 DRAM Controller

- 1.3.2 DMA Controller

- 1.3.3 Programmable Interval Timer

- 1.3.4 WATCHDOG Timer

- 1.3.5 Interrupt Controller

- 1.3.6 Real Time Clock/Calendar

- 1.3.7 Power Management Features

- 1.4 NS486SXF System Bus

- 1.5 Other On-Board Peripherals

- 1.5.1 Reconfigurable I/O Lines

- 1.5.2 IEEE 1284 Bidirectional Port

- 1.5.3 PCMCIA Interface

- 1.5.4 MICROWIRE/Access.bus Interface

- 1.5.5 UART Serial Port

- 1.5.6 LCD Controller

- 1.6 ICE Support

- 1.1 Other Issues

### 2.0 PIN DESCRIPTION TABLES

- TABLE 2-1. Bus Interface Unit Pins

- TABLE 2-2. DMA Control Pins

- TABLE 2-3. DRAM Control Pins

- TABLE 2-4. Power Pins

- TABLE 2-5. Reset Logic Pins

- TABLE 2-6. Auxiliary Processor Interface Pins

- TABLE 2-7. Test Pins

- TABLE 2-8. Interrupt Control Pins

- TABLE 2-9. Real Time Clock Pins

- TABLE 2-10. LCD Interface Pins

- TABLE 2-11. Oscillator Pins

- TABLE 2-12. IrDA/UART Pins

- TABLE 2-13. PCMCIA Pins

- TABLE 2-14. IEEE-1284 Port (ECP Mode)

- TABLE 2-15. Timer Pins

- TABLE 2-16. 3-Wire Serial I/O Pins

- TABLE 2-17. General Purpose Chip Select Pins

- TABLE 2-18. Summary of Reconfigurable I/O Pins

## 1.0 System Overview

### 1.1 NS486SXF SYSTEM OVERVIEW

The NS486SXF is a highly integrated embedded system controller. It includes an Intel486-class 32-bit processor, all resources required for the System Service Elements of a Real-Time Executive, and a generous set of peripherals. This "system-on-a-chip" is ideal for implementing a wide variety of embedded applications. These include (but are not limited to) fax machines, multifunction peripherals (fax, scanners, printers) mobile companions (both organizer and communicator), television set-top boxes, and telephones (mobile and desktop).

The 32-bit processor core executes all of the Intel486 instructions with a similar number of clocks per instruction. An on-board 1 kbyte instruction cache provides for efficient execution from ROM. Intel486 debug features are supported. The processor has been optimized for operating system kernels such as VRTX, VxWorks, pSOS + and QNX. These environments only need the '486 protected mode operation (no real mode or virtual 8086 support), flat or linear memory addressing (no virtual memory paging), and floating point execution in software only (no co-processor interface).

In fact, the **NS486SXF** includes all of the System Service Elements required by a typical kernel, including an efficient DRAM controller that supports page-mode DRAMs for data

cache-like performance; a six channel DMA controller with two channels supporting data transfers from on-chip peripherals (the IEEE 1284 ECP or Extended Capabilities Port, and the LCD controller), and four channels supporting external devices such as scanners, and print engines; three timer channels (including one configured as a protected WATCH-DOG Timer); two programmable 8259 interrupt controllers for 15 on-chip interrupt sources; an industry standard real time clock and calendar (RTC) with battery backup; and support for comprehensive power management schemes.

In addition, the **NS486SXF** also incorporates the key I/O peripherals required for implementing a wide variety of embedded applications: an IEEE 1284 Bidirectional Parallel Port that includes both Host and Slave modes, an Intel 82365-compatible PCMCIA controller for one card slot, an industry standard high-performance NS16550-compatible UART with HP-SIR and IrDA v1.0 infrared option, an LCD panel interface with DMA supported refresh for many of the standard resolutions, an 8254 timer, and a general purpose 2- or 3-wire synchronous serial interface for easy interface to low-cost EEPROMs and other serial peripherals. System expansion is supported with nine programmable Chip Select (CS) signals and a generic ISA-type bus interface for external devices and memory.

### 1.0 System Overview (Continued)

Certain I/O lines not being used by disabled peripherals can be reconfigured for use as general purpose bidirectional I/O lines (up to 29 pins). This gives the designer maximum flexibility in designing various systems using the NS486SXF device. It is expected that an NS486SXF system will minimally include the NS486SXF system controller with on-board processor and I/O devices, boot ROM, and working RAM memory. Many applications will not require any additional I/O support.

Finally, the **NS486SXF** implements a very flexible power management scheme that permits selective control of individual I/O subsystems, with varying levels of power consumption.

**NS486SXF** provides a cost-effective hardware platform for the design and implementation of a wide range of office automation and communication systems. With its powerful embedded '486-class processor, comprehensive set of on-chip peripheral controllers, flexible power management structure and reconfigurable I/O lines, **NS486SXF** makes possible a variety of end-user systems based on the same hardware. Because of its optimized design and on-board resources, a very cost effective system can be achieved.

#### 1.2 32-BIT PROCESSOR CORE

The **NS486SXF** processor core is an implementation of the protected mode '486 instruction set architecture, optimized using a RISC-like design philosophy for embedded applications. Using this approach, the most frequently used instructions are optimized, and on an average execute in a lower number of clock cycles than a '486.

The NS486SXF features a three stage pipeline, efficient instruction prefetching mechanism, and single cycle instruction decoding for most instructions. Additionally, a 1 kbyte instruction cache and single cycle DRAM access provide higher memory performance than a larger unified cache implementation while requiring much less die area.

The NS486XF processor provides the same programming model and register set as the standard '486 except that real mode, virtual memory, and floating point support have been eliminated. These features have little or no impact in embedded applications and save significant silicon real estate. At reset, unlike the standard '486, the NS486XF starts up in protected mode instead of real mode. All '486 instructions appropriate to protected mode and our hardware configuration are supported, including debug instructions.

The NS486SXF is initially available to run 25 MHz at 5V. The processor clock is obtained by dividing the crystal frequency by two. For example, a 25 MHz NS486SXF runs with a 50 MHz crystal oscillator as the master clock.

As a result of our innovative design, the NS486SXF achieves performance equivalent to a standard '486 with a much smaller die area. This translates into reduced power consumption and a lower overall system cost. It also makes the NS486SXF ideal for "green" systems and battery operated systems.

### 1.3 SYSTEM SERVICE ELEMENTS

The NS486SXF controller provides the basic hardware resources required for the O/S-defined System Service Elements. These include a DRAM controller, a DMA controller, programmable interval timer, a protected WATCHDOG timer, a programmable interrupt controller, a real-time clock and calendar, and comprehensive power management features

#### 1.3.1 DRAM Controller

The NS486SXF DRAM controller supports one or two adjustable-sized banks of dynamic RAM using a 16-bit data path. Support is provided for byte parity (if desired), requiring the DRAM banks to be 18 bits wide when parity is enabled. Banks can be up to 8 Mbytes in size. The DRAM controller supports page mode read and write operations and can also support both byte and word accesses. All access control signals for read, write and parity checking are generated as well as an automatic and programmable CAS-before-RAS refresh. If self-refresh DRAMs are used, refresh can be disabled, saving power.

NS486SXF provides flexible support for use of a number of different DRAM configurations, using popular DRAM devices. Access is optimized for fast page mode DRAMs, and they will provide the highest performance with contiguous data. When accessing data bytes or words in the same DRAM page, the data access is in one cycle. This performance provides fast data access times without the overhead of a separate data cache. Page sizes can be 256, 512, 1024 or 2048 bytes. Flexibility for DRAM timing is provided through programming of the DRAM controller registers: 3 or 4 cycle page miss accesses and extended CAS cycles can be selected.

Memory bank 0 starts at address 0h; memory bank 1 can start at any address in the 128 Mbyte address map that is a multiple of its size.

#### 1.3.2 DMA Controller

The **NS486SXF** Direct Memory Access (DMA) controller is a high speed 16-bit controller that improves system performance by off-loading from the processor the task of managing data transfers to and from memory and external devices. Data transfers are done independently from the processor at a maximum data rate of 2 bytes per 2 clock cycles. (A 25 MHz clock yields a 25 Mbyte per second transfer rate.)

There are six independent DMA channels. Requestor and target addresses have a maximum addressable memory range of 64 Mbytes. Three standard transfer modes, single, block and demand, are provided giving the designer a wide range of DMA options. A special transfer type, cascademaster, allows an external master to access the NS486SXF ISA-like bus. Normal transfers can be from memory to memory, memory to I/O and I/O to memory. DMA transfers are controlled by DMA control registers in the NS486SXF control register I/O map.

### 1.3.3 Programmable Interval Timer

The NS486SXF programmable interval timer is compatible with the Intel 8254 programmable interval timer and contains three identical timers (CH0–CH2). CH0 and CH1 can be used to generate accurate timing delays under software control. CH2 may be configured to provide a WATCHDOG timer function.

#### 1.3.4 WATCHDOG Timer

The NS486SXF WATCHDOG timer, CH2, is a protected 16-bit timer that can be used to prevent system "lockups or hangups." It uses a 1 kHz clock generated by the on-chip real-time clock circuit. If the WATCHDOG timer is enabled and times out, a reset or interrupt will be generated allowing graceful recovery from an unexpected system lockup.

## 1.0 System Overview (Continued)

#### 1.3.5 Interrupt Controller

The NS486SXF interrupt controller consists of two cascaded programmable interrupt controllers that are compatible with the Intel 8259A Programmable Interrupt Controller. They provide a total of 15 (out of 16) programmable interrupts. Three interrupts are reserved for a real time clock-tick interrupt, a real time clock interrupt request, and a cascade interrupt channel. The remaining 13 interrupts can be used by internal or external sources. Additional external interrupt controllers can be cascaded as well.

#### 1.3.6 Real Time Clock/Calendar

The NS486SXF Real Time Clock/Calendar is a low power clock that provides a time-of-day clock and 100-year calendar with alarm features and battery operation. Time is kept in BCD or binary format. It includes 50 bytes of general purpose CMOS RAM and 3 maskable interrupt sources. It is compatible with the DS1287 and MC146818 RTC/Calendar devices, except for the general purpose memory size.

#### 1.3.7 Power Management Features

The NS486SXF power management structure includes a number of power saving mechanisms that can be combined to achieve comprehensive power savings under a variety of system conditions. First of all, the core processor power consumption can be controlled by varying the processor/system clock frequency. The internal CPU clock can be divided by 4, 8, 16, 32 or 64. In addition, in idle mode, the internal processor clock will be disabled. Finally, if an external crystal oscillator circuit is being used, it can be disabled. For maximum power savings, all internal clocks can be disabled (except for the real-time clock oscillator).

Some peripherals, notably the timer and the PCMCIA interface, can be switched between a fixed frequency (external oscillator/2) and the CPU clock. If the CPU clock is being divided down, running these peripherals from the CPU clock will reduce their power consumption as well. The clocks of

other on-board peripherals can be individually or globally controlled. By setting bits in the power management control registers, the internal clocks to the DMA controller, the ECP port, the three-wire interface, the timer, the LCD controller, the DRAM controller, the PCMCIA controller and the UART can be disabled.

In addition to these internal clocks, the external SYSCLK can be disabled via a bit in the power management control registers.

Using various combinations of these power saving controls with the **NS486SXF** controller will result in excellent programmable power management for any application.

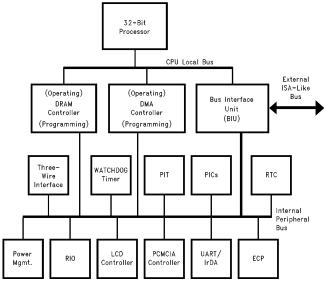

#### 1.4 NS486SXF SYSTEM BUS

The NS486SXF system bus provides the interface to offchip peripherals and memory. It offers an ISA-compatible interface and is therefore capable of directly interfacing to many ISA peripheral control devices. The interface is accomplished through the Bus Interface Unit or BIU. The BIU generates all of the access signals for both internal and external peripherals and memory. Depending upon whether the access is to internal peripherals, external peripherals or external memory, the BIU generates the timing and control signals to access those resources. The BIU is designed to support a glueless interface to many ISA-type peripherals.

For debug purposes, the **NS486SXF** can be set to generate external bus cycles at the same time as an internal peripheral access takes place. This gives logic analyzers or other debug tools the ability to track and capture internal peripheral accesses

Access to internal peripherals is accomplished in three CPU T-states (clock cycles). The fastest access to off-chip I/O is also three T-states. When accessing off-chip memory and I/O, wait state generation is accomplished through a combination of **NS486SXF** chip select logic and off-chip peripheral control signals.

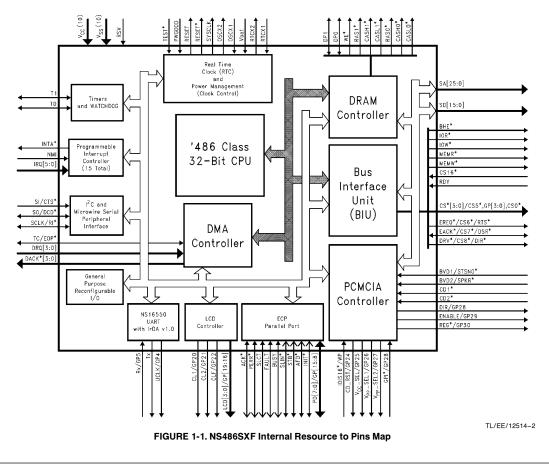

FIGURE 1-1. NS486SXF Internal Busses

TL/EE/12514-3

## 1.0 System Overview (Continued)

When the CPU is in idle mode, the BIU is designed to mimic the CPU during DMA interchanges between memory and peripherals. By responding to DRQs and generating DACKs, HOLDs and HOLDAs signals as required, the BIU eliminates the need to reactivate the CPU during such transfers as screen updates from memory to the LCD controller. This gives the designer added flexibility in conserving power while maintaining basic system functions.

#### 1.5 OTHER ON-BOARD PERIPHERALS

In addition to those peripherals and system control elements needed for System Service Elements, the NS486SXF also includes a number of I/O controllers and resources that make implementing a complete embedded system possible with just a single-chip NS486SXF controller. These include an IEEE 1284 Extended Capabilities Port, a serial UART port, a LCD controller, a PCMCIA interface and a MICROWIRE or Access.bus synchronous serial bus interface. In addition, unused I/O controllers free up their I/O pins for general purpose use.

#### 1.5.1 Reconfigurable I/O Lines

The NS486SXF supports reconfigurable I/O. For example, if the UART, ECP Parallel Port, LCD or PCMCIA functions are not being used, the I/O pins associated with them can be reconfigured as general purpose bidirectional I/O pins. Up to 29 pins, on a pin-by-pin basis can be reconfigured for this purpose. This capability makes the NS486SXF extremely versatile and ideal for supporting different end product configurations with a single NS486SXF device.

#### 1.5.2 IEEE 1284 Bidirectional Port

The NS486SXF parallel port is a multifunction 8-bit parallel port that is compatible with the IEEE 1284 bidirectional parallel port standard. The operation of the parallel port is set by the content of the NS486SXF parallel port I/O control registers. The port can operate in one of two modes: a standard parallel port mode ( PC compatible), or a full Extended Capabilities Port (ECP) mode. The NS486SXF ECP port can support both Host and Slave ECP mode. In slave mode, the NS486SXF becomes a versatile microprocessor for parallel I/O peripheral devices.

#### 1.5.3 PCMCIA Interface

The **NS486SXF** PCMCIA interface supports the direct connection of a single PCMCIA 2.0 IC card. Exchange Card Architecture (ExCA release 1.50) compatibility and eXecute In Place (XIP) capability is also provided.

Accessing the PCMCIA interface switches the external bus automatically into the PCMCIA mode and permits Memory Window Mapping and Address Offset to be handled inside the NS486SXF device. Power management and "hot" card insertion/removal options can be implemented using external buffering, if required.

### 1.5.4 MICROWIRE/Access.bus Interface

The NS486SXF MICROWIRE/Access.bus interface provides for full support of either the three-wire MICROWIRE/MICROWIRE/PLUS or the two-wire Access.bus serial interfaces. MICROWIRE/PLUS includes all the capabilities of the MICROWIRE standard and adds an alternate clock phasing option that supports the SPI bus protocol as well. These industry standard interfaces permit easy interfacing to a wide range of low-cost specialty memories and I/O devices. These include EEPROMs, SRAMs, timers, clock chips, A/D converters, D/A converters, and peripheral device drivers.

#### 1.5.5 UART Serial Port

The NS486SXF UART provides complete NS16550 (PC standard) serial communications port compatibility including the performance enhancing 16-byte deep FIFO. It performs serial-to-parallel conversion from external devices to the NS486SXF and parallel-to-serial conversion from the NS486SXF to external peripherals. Full modem control can be supported.

A serial IrDA v1.0 and HP-SIR (infrared) mode is also supported, making possible low-cost wireless communications between an **NS486SXF**-based system and other wireless infrared systems.

#### 1.5.6 LCD Controller

The NS486SXF LCD controller is capable of controlling a variety of monochrome supertwist LCD configurations including 320x240, 320x200 and 480x320 B&W or grayscale graphics LCD modules equipped with self-contained screen drivers. It uses a video frame buffer in system DRAM with either a 1-bit or 2-bit per pixel grayscale. A 60 Hz to 90 Hz frame refresh rate is supported. Special controls permit the fine tuning of display characteristics to precisely optimize visual display quality.

#### 1.6 ICE SUPPORT

National Semiconductor has worked closely with Microtek International to provide hardware in-circuit emulator support for the NS486SXF. The Microtek product (PowerPack® EA-NS486) uses a special bondout version of the NS486SXF to deliver a full-featured hardware emulator that is capable of tracing on chip activity, including peripheral interrupt and I/O activity. The emulator runs at full speed, and supports overlay memory and multiple triggers.

#### 1.7 OTHER ISSUES

NS486SXF provides a comprehensive set of on-board peripherals. However, it is designed to easily interface to external peripherals as well. In addition to an ISA-like bus for connecting to ISA-compatible peripherals, it supports an interface to an external master with a shared memory space. The external master or auxiliary processor interface allows low cost interfacing to shared external memory belonging to other external masters (including another NS486SXF controller)

To program the resources of the **NS486SXF**, a set of control registers exists in the external I/O map. These registers provide precise control over all internal resources and the setup of external **NS486SXF** control signals. It is the designer's responsibility to ensure the proper initialization of the registers in this I/O map.

In addition, the **NS486SXF** core processor itself requires several descriptor tables and initialization parameters that must be set by user-written start-up software.

The NS486SXF is designed from the ground up for optimum price/performance in embedded systems. This makes the NS486SXF the logical choice as the base hardware platform for executing an embedded operating system kernel such as those available from Microtec, Wind River, ISI, QNX, and many others. Any Operating System or Real-Time Executive that will operate in a segmented or flat memory model protect mode environment is a suitable complement to the NS486SXF.

Also, there are many third party tool sets that will allow an executable application to be built to run directly on the target hardware without an O/S environment.

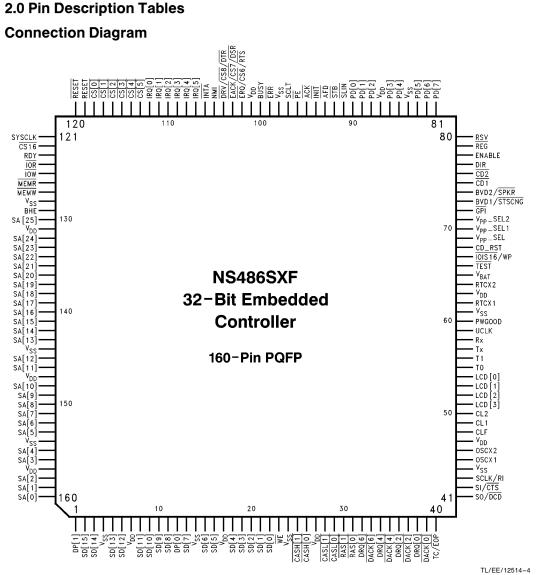

FIGURE 2-1. NS486SXF Package Pinout Diagram

TL/EE/12514-4

The NS486SXF single chip controller is provided in a compact 160-pin, industry standard JEDEC PQFP package. The following tables detail the Symbol, Type, and Description of each pin. The tables divide the pins into functional groups as follows: Bus Interface Unit Pins, DMA Control Pins, DRAM Control Pins, Power Pins, Reset Logic Pins, Auxiliary Processor Interface Pins, Test Pins, Interrupt Control Pins, Real Time Clock Pins, LCD Interface Pins, Oscillator Pins, IrDA/UART Pins, PCMCIA Pins, IEEE-1284 Port (ECP

Mode) Pins, Timer Pins, 3-Wire Serial I/O Pins, General Purpose Chip Select Pins, and Reconfigurable I/O Pins. Twenty-nine I/O pins are multipurpose. In their standard modes, they perform specific I/O controller functions. When those particular I/O functions are not required in the system, however, those pins can be reprogrammed to become general purpose, bidirectional I/O lines.

Note: In the above figure and in the following tables, all active low signals are shown with an overbar.

# TABLE 2-1. Bus Interface Unit Pins

| Symbol   | Pins | Туре | Function                                                                                                                                                                                                                                                                                                                                         |

|----------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SA[25:0] | 26   | 0    | System Address bus: These output-only signals carry the latched address for the current access. DRAM accesses multiplex the row and column addresses for the DRAMs on the SA[12:1] pins. During Interrupt Acknowledge cycles, the internal master interrupt controller's cascade line signals, CAS[2:0], are driven onto SA[25:23] respectively. |

| SD[15:0] | 16   | 1/0  | System Data bus: This bi-directional data bus provides the data path for all memory and I/O accesses. During transfers with 8-bit devices, the upper data byte is not used (SD[15:8]).                                                                                                                                                           |

| BHE      | 1    | 0    | Byte High Enable: This active-low signal indicates that the high byte (odd address byte) is being transferred. External 16-bit devices should use this signal to help them determine that a data byte is to be transferred on the upper byte or the System Data bus (SD[15:8]).                                                                  |

| ĪŌR      | 1    | 0    | IO Read command: This active-low signal instructs an I/O device to place data onto the system data bus.                                                                                                                                                                                                                                          |

| ĪŌW      | 1    | 0    | <b>IO W</b> rite command: This active-low signal indicates to an I/O device that a write operation is in process on the system bus.                                                                                                                                                                                                              |

| MEMR     | 1    | 0    | <b>MEM</b> ory <b>R</b> ead command: This active-low signal instructs a memory mapped device to place data onto the system data bus.                                                                                                                                                                                                             |

| MEMW     | 1    | 0    | <b>MEM</b> ory Write command: This active-low signal indicates to a memory mapped device that a write operation is in process on the system bus.                                                                                                                                                                                                 |

| CS16     | 1    | I    | Chip Select 16-bit: This active-low feedback signal indicates that the device being accessed is a 16-bit device. This signal should be driven by external devices with an open collector or TRI-STATE® driver.                                                                                                                                   |

| RDY      | 1    | Ī    | ReaDY: An external device may drive this signal inactive low to insert wait states and extend the external bus cycle. This signal should be driven with an open collector be TRI-STATE driven.                                                                                                                                                   |

## **TABLE 2-2. DMA Control Pin**

| Symbol                        | Pins | Туре | Function                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRQ6, DRQ4,<br>DRQ2, DRQ0     | 4    | I    | DMA ReQuest: A DRQn signal requests the internal DMA Controller to transfer data between the Requesting Device and memory.                                                                                                                                                                                                                   |

| DACK6, DACK4,<br>DACK2, DACK0 | 4    | 0    | DMA ACKnowledge: When the CPU has relinquished control of the bus to a requesting DMA channel, the appropriate active-low DACKn signal acknowledges the winning DRQn.                                                                                                                                                                        |

| TC/EOP                        | 1    | I/O  | Terminal Count/End Of Process: This signal may operate either as a terminal count output or an active-low End of Process input. As TC, an active-high pulse occurs on this signal when the terminal count for any DMA channel has been reached. As EOP, an external device may terminate the DMA transfer by driving this signal active-low. |

## TABLE 2-3. DRAM Control Pins

| Symbol    | Pins | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAS[1:0]  | 2    | 0    | Row Address Strobe: On the falling edge of these active-low signals, Bank 1 and Bank 0 respectively, should latch in the row address off of SA [12:1]. If only one bank of DRAMs are supported, RAS0 will support that bank and RAS1 will be unused.                                                                                                                                                               |

| CASH[1:0] | 2    | 0    | Column Address Strobe (High Byte): These active-low signals indicate when the column access is being made to the high byte of DRAM Bank 1 and DRAM Bank 0 respectively. If only one bank of DRAMs are supported, CASH0 will support the high byte of that bank and CASH1 will be unused.                                                                                                                           |

| CASL[1:0] | 2    | 0    | Column Address Strobe (Low Byte): These active-low signals indicate when the column access is being made to the low byte of DRAM Bank 1 and DRAM Bank 0, respectively. If only one bank of DRAMs are supported, CASL0 will support the low byte of that bank and CASL1 will be unused.                                                                                                                             |

| WE        | 1    | 0    | Write Enable: Active low signal for writing the data into the DRAM bank.                                                                                                                                                                                                                                                                                                                                           |

| DP[1:0]   | 2    | 1/0  | DRAM Data Parity: DRAM data parity may be enabled or disabled; if disabled these two pins will be unused. Otherwise, for DRAM writes the NSC486SXF's DRAM Controller will generate odd parity and drive the odd parity onto these two pins. For DRAM reads the NS486SXF's DRAM Controller will read the values driven on these two pins and check it for odd parity in association with the appropriate data byte. |

## **TABLE 2-4. Power Pins**

| Symbol          | Pins | Туре | Function                            |

|-----------------|------|------|-------------------------------------|

| V <sub>CC</sub> | 10   | I    | +3.3V or +5V power to core and I/O. |

| V <sub>SS</sub> | 10   | I    | Ground to core and I/O.             |

## TABLE 2-5. Reset Logic Pins

| Symbol | Pins | Туре | Function                                                                                                                                                                                                                                                                                                  |

|--------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET  | 1    | 0    | <b>RESET</b> system output driver: This active high signal resets or initializes system peripheral logic during power up or during a low line voltage outage.                                                                                                                                             |

| RESET  | 1    | 0    | Inverse of RESET for peripherals requiring active low reset.                                                                                                                                                                                                                                              |

| PWGOOD | 1    | Ī    | PoWer GOOD: This active-high (Schmitt trigger) input will cause a hardware reset to the NS486SXF whenver this input goes low. This pin will typically be driven by the power supply and PWGOOD will remain low until the power supply determines that stable and valid voltage levels have been achieved. |

# TABLE 2-6. Auxiliary Processor Interface Pins

| Symbol       | Pins | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EREQ/CS6/RTS | 1    | 0    | This pin has three programmable options controlled by the Modem Signal Control Register (refer to the UART section):  1. External bus REQuest (active-low) to an auxiliary process.  2. Chip Select 6 (active-low) pin.  3. Request To Send. When low, this signal informs the MODEM or data set that the UART is ready to exchange data. The RTS output signal can be set to an active low by programming bit 2 (RTS) of the MODEM Control Register. A Master Reset operation sets this signal to its inactive (high) state. Loop mode operation holds this signal in its inactive state.                                                                                                                                                                                                                                                 |

| EACK/CS7/DSR | 1    | 1/0  | This pin has three possible programmable options controlled by the Modem Signal Control Register (refer to the UART section):  1. External bus ACKnowledge (active-low) from an auxiliary processor.  2. Chip Select 7 (active-low) pin.  3. Data Set Ready. When low, it indicates that the MODEM or data set is ready to link with the UART. The DSR signal is a MODEM status input whose condition can be tested by the CPU reading bit 5 (DSR) of the MODEM Status Register. Bit 5 is the complement of the DSR signal. Bit 1 (DDSR) of the MODEM Status Register indicates whether the DSR input has changed state since the previous reading of the MODEM Status Register.  Note: Whenever the DSR bit of the MODEM Status Register changes state, an interrupt is generated if the MODEM Status Interrupt is generated if the MODEM |

| DRV/CS8/DTR  | 1    | 0    | This pin has three possible programmable options controlled by the Modem Signal Control Register (refer to the UART section):  1. DSP shared memory <b>DRiVe</b> control signal.  2. <b>Chip Select 8</b> (active-low) pin.  3. <b>Data Terminal Ready:</b> When low, this signal informs the MODEM or data set that the UART is ready to establish a communications link. The DTR output signal can be set to an active low by programming bit 0 (DTR) of the MODEM Control Register to a high level. A Master Reset operation sets this signal to its inactive (high) state. Loop mode operation holds this signal in its inactive state.                                                                                                                                                                                                |

## TABLE 2-7. Test Pins

| Symbol | Pins | Туре | Function                                             |

|--------|------|------|------------------------------------------------------|

| TEST   | 1    | 1/0  | Reserved for testing and development system support. |

# TABLE 2-8. Interrupt Control Pins

| Symbol   | Pins | Туре | Function                                                                                                                                                                                                                                                                         |

|----------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMI      | 1    | I    | Non-Maskable Interrupt: This active-high signal will generate a non-maskable interrupt to the CPU when it is active high. Normally this signal is used to indicate a serious system error.                                                                                       |

| ĪNTA     | 1    | 0    | INTerrupt Acknowledge: During each interrupt acknowledge cycle this signal will strobe low; it should be used by external cascaded interrupt controllers.                                                                                                                        |

| IRQ[5:0] | 6    | I    | Interrupt ReQuests: These inputs are either rising edge or low-level sensitive interrupt requests, depending on the configuration of the internal interrupt controllers. These interrupt requests may also be programmed to support externally cascaded interrupt controller(s). |

## TABLE 2-9. Real Time Clock Pins

| Symbol | Pins | Туре | Function                                                   |

|--------|------|------|------------------------------------------------------------|

| RTCX1  | 1    | I    | Real Time Clock Crystal oscillator input: 32 kHz crystal.  |

| RTCX2  | 1    | 0    | Real Time Clock Crystal oscillator output: 32 kHz crystal. |

| Vbat   | 1    | ı    | External + battery input for real time clock.              |

## **TABLE 2-10. LCD Interface Pins**

| Symbol   | Pins | Туре | Function                                            |

|----------|------|------|-----------------------------------------------------|

| LCD[3:0] | 4    | 0    | Data Output Word to LCD, 1 = White, 0 = Blue/black. |

| CL2      | 1    | 0    | Word <b>CL</b> ock to LCD.                          |

| CL1      | 1    | 0    | Row <b>CL</b> ock to LCD.                           |

| CLF      | 1    | 0    | Frame CLock to LCD.                                 |

## **TABLE 2-11. Oscillator Pins**

| Symbol | Pins | Туре | Function                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|--------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SYSCLK | 1    | 0    | SYStem CLocK: This clock output pin will either be driven with a signal half the frequency of the OSCX1 input clock frequency or the CPU's clock frequency, which is determined in the Power Management Control Register 1. The source selection for this signal is determined by bit 1 of the Power Management Control Register 3. |  |  |  |  |

| OSCX1  | 1    | I    | OSCillator Crystal 1 input: This pin should either be driven by a TTL oscillator or be connected to an external crystal circuit. This signal is the fundamental clock source for all clocked elements in the NS486SXF, except the Real-Time Clock, which has its own crystal pins.                                                  |  |  |  |  |

| OSCX2  | 1    | 0    | OSCillator Crystal 2 output: This is the output side of the NS486SXF on-chip circuitry provided to support an external crystal circuit. If a TTL oscillator drives OSCX1, this pin should be a no connect.                                                                                                                          |  |  |  |  |

## TABLE 2-12. IrDA/UART Pins

| Symbol | Pins | Туре | Function                                                                                                                                                 |

|--------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Тх     | 1    | 0    | UART Transmit data: In IrDA mode this pin is the UART output encoded or the serial infrared link. Otherwise it is the transmit output of the 16550 UART. |

| Rx     | 1    | I    | UART Receive data: In IrDA mode this pin is routed through the serial infrared decoder. Otherwise, it is the receive input to the 16550.                 |

| UCLK   | 1    | I/O  | Uart CLock: Output of programmable rate UART/MODEM clock. Typically used for the Infrared Modulator.                                                     |

# TABLE 2-13. PCMCIA Pins

| Symbol                                          | Pins | Туре | e Function                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-------------------------------------------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CD_RST                                          | 1    | 0    | CarD ReSeT: This active high signal resets the PCMCIA card during a soft-reset.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| ĪOIS16/WP                                       | 1    | I    | IO port IS 16 bits/Write Protect: When a PCMCIA card is configured as an IO card, this signal is asserted to indicate the currently addressed IO port is 16 bits wide. When a PCMCIA card is configured as a memory card, an active high signal indicates the card is currently write protected.                                                                                      |  |  |  |  |  |

| BVD2/SPKR                                       | 1    | - 1  | Battery Voltage Detect bit 2/SPeaKeR output: When a PCMCIA card is configured as a memory card, this input along with BVD[1] will provide status information about the card's on-board battery condition. When a PCMCIA card is configured as an IO card, this pin will act as the audio output of the card to the system.                                                            |  |  |  |  |  |

| BVD1/STSCNG                                     | 1    | I    | Battery Voltage Detect bit 1/STatuS ChaNGe output: When a PCMCIA card is configured as a memory card, this input along with BVD[2] will provide status information about the card's on-board battery state. When a PCMCIA card is configured as an I/O card, the status change signal indicates one or more of the memory satus signal (BVD[2:1], WP, RDY or BSY) has changed states. |  |  |  |  |  |

| V <sub>CC</sub> _SEL                            | 1    | 0    | PCMCIA $\mathbf{V_{CC}}$ SELect: When this signal is high, the $\mathbf{V_{CC}}$ power to the PCMCIA card should be enabled.                                                                                                                                                                                                                                                          |  |  |  |  |  |

| V <sub>PP</sub> _SEL1,<br>V <sub>PP</sub> _SEL2 | 2    | 0    | PCMCIA <b>V<sub>PP</sub> SEL</b> ect 1 and 2: These signals indicate the voltage with which the V <sub>PP</sub> power to the PCMCIA card should be driven.                                                                                                                                                                                                                            |  |  |  |  |  |

| GPI                                             | 1    | I    | General Purpose Input: This signal is a general purpose input signal used with a PCMCIA card to indicate a valid V <sub>PP</sub> state, a pending card eject/insertion, or as an interrupt source.                                                                                                                                                                                    |  |  |  |  |  |

| CD2, CD1                                        | 2    | ı    | Card Detect: Both signals are low when the PCMCIA card is correctly inserted.                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| DIR                                             | 1    | 0    | DIRection: Used to control the direction of the data line buffers to the PCMCIA interface.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| ENABLE                                          | 1    | 0    | ENABLE PCMCIA: Enables the buffer drivers to the PCMCIA interface.                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| REG                                             | 1    | 0    | REG: PCMCIA card support.                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

# TABLE 2-14. IEEE-1284 Port (ECP Mode)

| Symbol  | Pins | Туре | Function                                                                                                                                                                                                                   |  |  |

|---------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PD[7:0] | 8    | 1/0  | Parallel Data: Bi-directional data pins transfer data and address information to and from the parallel port.                                                                                                               |  |  |

| SLIN    | 1    | 0/I  | <b>SeL</b> ect <b>IN</b> put: Used in a closed-loop handshake with BUSY to transfer data or address information from the host to the peripheral. Host driven.                                                              |  |  |

| STB     | 1    | 0/I  | data <b>ST</b> ro <b>B</b> e: Driven high by the host while in ECP Mode. Asserted low by host to terminate ECP Mode and return link to Compatibility Mode. Host driven.                                                    |  |  |

| ĀFD     | 1    | O/I  | Automatic FeeD: The host asserts this line low for flow control in the reverse direction. It is used in an interlocked handshake with ACK. Provides command information in the forward direction. Host driven. Active low. |  |  |

| ĪNIT    | 1    | 0/I  | <b>INIT</b> ialize: When this signal is asserted low to place the data channel in the reverse direction, the peripheral is allowed to drive the data bus. Host driven. Active low.                                         |  |  |

| ACK     | 1    | 1/0  | <b>ACK</b> nowledge: Used in closed-loop handshake with $\overline{\text{AFD}}$ to transfer data to the host. Peripheral device drive. Active low.                                                                         |  |  |

| PE      | 1    | 1/0  | Peripheral Error: Asserted low to acknowledge INIT, reverse request. Peripheral device drive.                                                                                                                              |  |  |

| SLCT    | 1    | 1/0  | SeLeCT: Asserted high when selected or indicating an affirmative response for each respective extensibility byte. Peripheral device drive. Active high.                                                                    |  |  |

| ERR     | 1    | I/O  | <b>ERROR</b> : This input is asserted low by the peripheral to request host communications. Valid only in the forward direction. Peripheral device drive. Active low.                                                      |  |  |

| BUSY    | 1    | 1/0  | BUSY: This is asserted low by the peripheral for flow control in the forward direction, de-asserted to acknowledge transfer or data or address completion. Peripheral device drive. Active low.                            |  |  |

# TABLE 2-15. Timer Pins

| Symbol | Pins | Туре | Function                                                                                                                                                                                                                                                                                           |  |  |

|--------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ТО     | 1    | 1/0  | Programmer Timer pin 0: This Bidirectional pin may be selected to control one of the following four functions via bits 1–0 of the Timer I/O Control Register:  1. The GATE input into Timer 0.  2. The GATE input into Timer 1.  3. The OUT output from Timer 0.  4. The CLK input into Timer 1.   |  |  |

| T1     | 1    | 1/0  | Programmable Timer pin 1: This Bidirectional pin may be selected to control one of the following four functions via bits 3–2 of the Timer I/O Control Register:  1. The GATE input into Timer 0.  2. The GATE input into Timer 1.  3. The OUT output from Timer 1.  4. The CLK input into Timer 0. |  |  |

## TABLE 2-16. 3-Wire Serial I/O Pins

| Symbol  | Pins | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|---------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SO/DCD  | 1    | 1/0  | This pin has two possible programmable options controlled by the Modern Signal Control Register (refer to the UART section):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|         |      | 1/0  | 1. The serial data <b>O</b> utput signal for MICROWIRE or the serial data I/O for Access.bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|         |      | l    | 2. Data Carrier Detect: When low, this input signal indicates that the data carrier has been detected by the MODEM or data set. The DCD signal is a MODEM status input whose condition can be tested by the CPU reading bit 7 (DCD) of the MODEM Status Register. Bit 7 is the complement of the DCD signal. Bit 3 (DDCD) of the MODEM Status Register indicates whether the DCD input has changed state since the previous reading of the MODEM Status Register. DCD has no effect on the receiver.                                                                                                                |  |  |  |

|         |      |      | Note: Whenever the DCD bit of the MODEM Status Register changes state, an interrupt is generated if the MODEM Status Interrupt is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| SI/CTS  | 1    | I    | This pin has two possible programmable options controlled by the Modem Signal Control Register (refer to the UART section):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|         |      |      | 1. The <b>S</b> erial data Input signal for MICROWIRE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|         |      |      | Clear To Send: When low, this input signal indicates that the MODEM or data set is ready to exchange data. The CTS signal is a MODEM status input whose conditions can be tested by the CPU reading bit 4 (CTS) of the MODEM Status Register. Bit 4 is the complement of the CTS signal. Bit 0 (DCTS) of the MODEM Status Register indicates whether the CTS input has changed state since the previous reading of the MODEM Status Register. CTS has no effect on the Transmitter.                                                                                                                                 |  |  |  |

|         |      |      | Note: Whenever the CTS bit of the MODEM Status Register changes state, an interrupt is generated if the MODEM Status Interrupt is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| SCLK/RI | 1    | 1/0  | This pin has two possible programmable options controlled by the Modem Signal Control Register (refer to the UART section):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|         |      | 0    | 1. The Serial CLocK signal for MICROWIRE and Access.bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|         |      | I    | 2. Ring Indicator. When low, this input signal indicates that a telephone ringing signal has been received by the MODEM or data set. The RI signal is a MODEM status input whose condition can be tested by the CPU reading bit 6 (RI) of the MODEM Status Register. Bit 6 is the complement of the RI signal. Bit 2 (TERI) of the MODEM Status Register indicates whether the RI input signal has changed from a low to high state since the previous reading of the MODEM Status Register.  Note: Whenever the CTS bit of the MODEM Status Register changes state, an interrupt is generated if the MODEM Status. |  |  |  |

|         |      |      | Interrupt is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|         |      |      | Note: Whenever the RI bit of the MODEM Status Register changes from a high to a low state, an interrupt is generated if the MODEM Status Interrupt is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

## TABLE 2-17. General Purpose Chip Select Pins

| Symbol  | Pins | Туре | Function                                                                                                                                                                                                                                                                               |  |  |

|---------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CS0     | 1    | 0    | Chip Select 0: This output is used as the chip select for the system boot ROM. If defaults to the upper 64 kBytes of memory.                                                                                                                                                           |  |  |

| CS[5:1] | 5    | 1/0  | Chip Select 1–5: These pins can be programmed to be either memory or I/O mapped chip selects, which are used for glue-less connection to external peripherals. When the PCMCIA Controller is enabled CS1 and CS2 become PCMCIA Card Enable inputs 1 and 2 (CET and CE2, respectively). |  |  |

# TABLE 2-18. Summary of Reconfigurable I/O Pins

| Symbol                | Pins | Туре | Pin #                          | Original Function |

|-----------------------|------|------|--------------------------------|-------------------|

| REG                   | 1    | 1/0  | 79                             | PCMCIA            |

| ENABLE                | 1    | 1/0  | 78                             | PCMCIA            |

| DIR                   | 1    | 1/0  | 77                             | PCMCIA            |

| GPI                   | 1    | 1/0  | 72                             | PCMCIA            |

| V <sub>PP</sub> _SEL2 | 1    | 1/0  | 71                             | PCMCIA            |

| V <sub>PP</sub> _SEL1 | 1    | 1/0  | 70                             | PCMCIA            |

| V <sub>CC</sub> _SEL  | 1    | 1/0  | 69                             | PCMCIA            |

| CD_RST                | 1    | 1/0  | 68                             | PCMCIA            |

| CLF                   | 1    | 1/0  | 48                             | LCD               |

| CL2                   | 1    | 1/0  | 50                             | LCD               |

| CL1                   | 1    | 1/0  | 49                             | LCD               |

| LCD [3:0]             | 4    | 1/0  | 51, 52, 53, 54                 | LCD               |

| PD [7:0]              | 8    | 1/0  | 81, 82, 83, 85, 86, 88, 89, 90 | ECP               |

| Rx                    | 1    | 1/0  | 58                             | UART              |

| UCLK                  | 1    | 1/0  | 59                             | UART              |

| CS [4]                | 1    | 1/0  | 114                            | CS4               |

| CS [3]                | 1    | 1/0  | 115                            | CS3               |

| CS [2]                | 1    | 1/0  | 116                            | CS2               |

| CS [1]                | 1    | 1/0  | 117                            | CS1               |

These 29 pins, typically used for various I/O peripheral purposes, as defined in the above tables, can be reconfigured for use as general purpose I/O pins if the normally defined I/O function is not required.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor**

National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-35U oo oo Email: onjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

National Semiconductor National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor

Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408