NCR Product Design Series

# VS1500 ViGen Cell Data Sheets

Release 3.0 February 1990

# ViGen is a trademark of NCR Corporation

Copyright © 1988, 1989, 1990 by NCR Corporation

Dayton, Ohio

All Rights Reserved Printed in U.S.A.

CONFIDENTIAL UNPUBLISHED PROPERTY OF NCR CORPORATION

# NCR 1.5 $\mu$ ViGen LIBRARY DATA SHEETS ALPHABETICAL CONTENTS

| PAGE | CELL NAME  | CELL DESCRIPTION                |

|------|------------|---------------------------------|

| 1    | ALUGEN     | ALU Generator                   |

| 7    | CNTRGEN    | Binary Counter Generator        |

| 16   | DPRGEN     | Dual Port RAM Generator         |

| 28   | FIFOGEN    | FIFO Generator                  |

| 38   | MACCGEN    | MAC Generator                   |

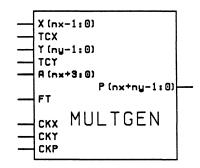

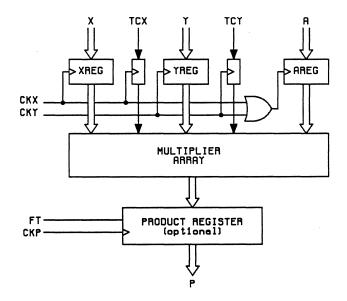

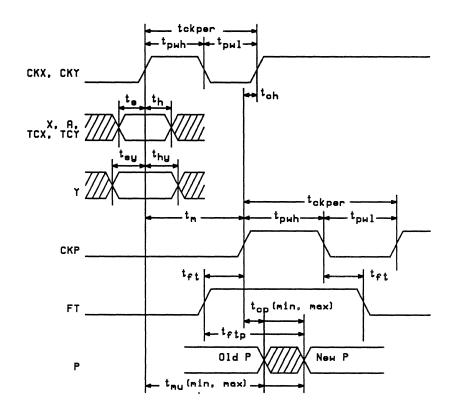

| 49   | MULTGEN    | Multiplier Generator            |

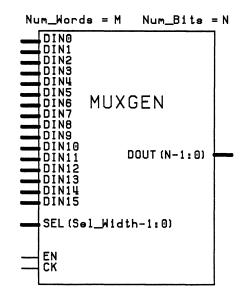

| 59   | MUXGEN     | Data Multiplexer Generator      |

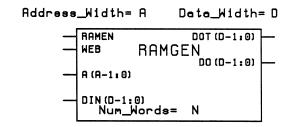

| 65   | RAMGEN     | RAM Generator                   |

| 74   | ROM m x n  | ROM Generator                   |

| 78   | SHFTGEN    | Shift Register Generator        |

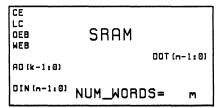

| 85   | SRAM m x n | High Speed Static RAM Generator |

# **VS1500 ALU**

#### **GENERAL DESCRIPTION**

- Performs the same 16 logical and 16 arithmetic operations as the TTL '181 ALU

- Static operation (no clocks)

- Carry look-ahead is internally generated

- Post-shift option allows a logical or arithmetic function plus a one-bit left or right shift in a single operation

- Selectable 2- through 32-bit input and output data buses

This generator builds a fast, static ALU that is based on the TTL '181 ALU. The sixteen arithmetic and sixteen logical functions provided are the same as those of the '181. The functions are selected by four function selector lines (S3, S2, S1, and S0), the MODE input (low = arithmetic, high = logical) and the active—low carry in (CINB).

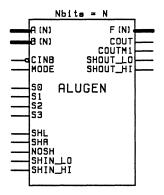

#### SYMBOL

The symbol for ALUGEN will be unique for each configuration. An example is given here only for reference.

#### INPUT PARAMETER RANGES

| INPUT<br>PARAMETER | ALLOWED<br>RANGE    | EXPLANATION                                        |

|--------------------|---------------------|----------------------------------------------------|

| Nbits              | 2 - 32<br>even only | Number of bits in the input and output data buses. |

| Shift              | 0 or 1              | Post-shift option (1=yes, 0=no).                   |

### **ALUGEN**

ViGen CONFIGURABLE FUNCTION

#### DIFFERENCES BETWEEN ALUGEN AND THE TTL '181 ALU

- Carry out is provided from the two most significant bits in ALUGEN, making overflow detection easy.

The '181 provides carry out only from the most significant bit. These active high carry outs will remain high for all logical mode operations.

- A post shift option is provided in ALUGEN. When enabled, extra control lines allow selection of NOSH (no shift), SHL (shift left by one bit), or SHR (shift right by one bit). This shift is done on the result of whatever function is selected in normal operation, making it possible to do an arithmetic or logical operation followed by a one-bit shift in one cycle. Deselecting all of the shift control inputs will tristate the output bus. Serial inputs and outputs are provided for both the least and most significant bits.

- The P/ and G/ outputs of the '181, used for carry look-ahead, are not provided and are not needed, since carry look-ahead is handled internally to ALUGEN. Standard '181s are extended to larger data words by cascading devices, and if carry look-ahead is desired, it must be done externally using '182s. ALUGEN accepts any data word size (even only) as input and builds its own internal custom carry look-ahead.

- The A=B output of the '181 is not provided in ALUGEN.

#### INPUTS/OUTPUTS

Definitions of the ALUGEN inputs and outputs are given in the following table. Input and output pin names are listed in pin-number sequence.

| PIN NAME | DEFINITION                                               | REQ/<br>OPT | CAP (pF) |

|----------|----------------------------------------------------------|-------------|----------|

| INPUTS:  |                                                          |             |          |

| A (N)    | A input bus                                              | REQ         | 0.326    |

| B (N)    | B input bus                                              | REQ         | 0.290    |

| CINB     | Carry input (active low)                                 | REQ         | 0.058    |

| MODE     | Mode control (High = logical, Low = arithmetic)          | REQ         | 0.054    |

| S0       | Function select input 0                                  | REQ         | 0.055    |

| S1       | Function select input 1                                  | REQ         | 0.055    |

| S2       | Function select input 2                                  | REQ         | 0.055    |

| S3       | Function select input 3                                  | REQ         | 0.055    |

| SHL      | Shift left by one bit control (Notes 1, 2)               | OPT         | 0.255    |

| SHR      | Shift right by one bit control (Notes 1, 2)              | OPT         | 0.255    |

| NOSH     | No shift (Note 1)                                        | OPT         | 0.255    |

| SHIN_LO  | Shift in to least significant bit                        | OPT         | 0.118    |

| SHIN_HI  | Shift in to most significant bit                         | OPT         | 0.118    |

| OUTPUTS: |                                                          |             |          |

| F (N)    | Output data bus                                          | REQ         | 0.230    |

| COUT     | Carry out (active high)                                  | REQ         |          |

| COUTM1   | Carry out from second most significant bit (active high) | REQ         |          |

| SHOUT_LO | Shift out from least significant bit (=F (0))            | OPT         | 0.118    |

| SHOUT_HI | Shift out from most significant bit (=F (Nbits-1))       | OPT         | 0.118    |

NOTE 1: Only one of SHL, SHR, and NOSH can be active at a time.

NOTE 2: SHL - bit 0 shifts to bit 1 position, etc. SHR - bit 1 shifts to bit 0 position, etc.

#### **SELECTABLE FUNCTIONS**

| SI | ELEC                            | CTIO | N  | MODE = H          | MODE = L (Arithmetic Operations) |                           |  |  |

|----|---------------------------------|------|----|-------------------|----------------------------------|---------------------------|--|--|

| S3 | S2                              | S1   | SO | Logical Functions | CINB = H<br>(no carry)           | CINB = L<br>(carry)       |  |  |

| L  | L                               | L    | L  | F = A/            | F = A                            | F - A plus 1              |  |  |

| L  | L                               | L    | Н  | F = (A+B)/        | F = A + B                        | F = (A+B) plus 1          |  |  |

| L  | L                               | Н    | L  | F = (A/)B         | F = A + B/                       | F = (A+B/) plus 1         |  |  |

| L  | L                               | Н    | Н  | F = 0             | F = all 1's                      | F = 0                     |  |  |

| L  | Н                               | L    | L  | F = (AB)/         | F = A plus AB/                   | F = A plus AB/ plus 1     |  |  |

| L  | Н                               | L    | н  | F = B/            | F = (A+B) plus AB/               | F = (A+B) plus AB/ plus 1 |  |  |

| L  | Н                               | н    | L  | F = A exor B      | F = A minus B minus 1            | F = A minus B             |  |  |

| L  | Н                               | Н    | Н  | F = AB/           | F = AB/ minus 1                  | F = AB/                   |  |  |

| Н  | L                               | L    | L  | F = A/ + B        | F = A plus AB                    | F = A plus AB plus 1      |  |  |

| Н  | L                               | L    | Н  | F = (A exor B)/   | F = A plus B                     | F = A plus B plus 1       |  |  |

| Н  | L                               | Н    | L  | F = B             | F = (A+B/) plus AB               | F = (A+B/) plus AB plus 1 |  |  |

| Н  | L                               | Н    | Н  | F = AB            | F = AB minus 1                   | F = AB                    |  |  |

| Н  | Н                               | L    | L  | F = all 1's       | F = A plus A                     | F = A plus A plus 1       |  |  |

| Н  | Н                               | L    | Н  | F = A + B/        | F = (A+B) plus A                 | F = (A+B) plus A plus 1   |  |  |

| Н  | Н                               | Н    | L  | F = A + B         | F = (A+B/) plus A                | F = (A+B/) plus A plus 1  |  |  |

| Н  | Н                               | Н    | Н  | F = A             | F = A minus 1                    | F = A                     |  |  |

| Н  | H = high L = low + = logical OR |      |    |                   |                                  |                           |  |  |

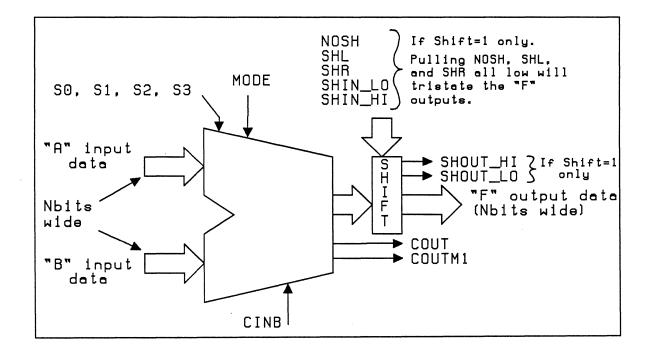

#### **FUNCTIONAL BLOCK DIAGRAM**

# **ALUGEN**

ViGen CONFIGURABLE FUNCTION

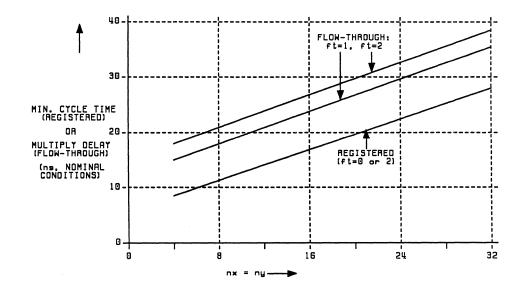

# TIMING PARAMETERS AND CELL SIZE AS FUNCTIONS OF INPUT PARAMETERS

Timing parameters are specified for nominal process, Vdd = 5.0 V, and temperature = 25°C. See the NCR ASIC Data Book for information on derating factors for process, voltage, and temperature. Input parameters are Nbits and Shift. CL is output capacitance in pF.

| PARAM            | DESCRIPTION                                                         | TYPICAL VALUE (ns)                                                         |

|------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------|

| <sup>t</sup> ifa | Any A[i] or B[i] input to any F[i] or SHOUT output, arithmetic mode | <sup>t</sup> ifa = 7.05 + 0.20*Nbits + 0.64*Shift + (0.90 + 0.45*Shift)*CL |

| <sup>t</sup> ica | Any A[i] or B[i] input to COUT or COUTM1, arithmetic mode           | <sup>t</sup> ica = 7.30 + 0.20*Nbits + 1.77*CL                             |

| <sup>t</sup> cfa | CINB to any F[i] or SHOUT output, arithmetic mode                   | <sup>t</sup> cfa = 4.45 + 0.20*Nbits + 0.64*Shift + (0.90 + 0.45*Shift)*CL |

| <sup>t</sup> cca | CINB to COUT or COUTM1, arithmetic mode                             | <sup>t</sup> cca = 4.95 + 0.20*Nbits + 1.77*CL                             |

| tifl             | Any A[i] or B[i] input to any F[i], or SHOUT output, logic mode     | <sup>t</sup> ifI = 3.57 + 0.55*Shift + (0.90 + 0.45*Shift)*CL              |

| <sup>t</sup> sf  | S0,S1,S2,S3 or MODE to any F[i], COUT, COUTM1 or SHOUT output       | <sup>t</sup> sf = 8.45 + 0.068*Nbits + 0.77*Shift + (0.90 + 0.45*Shift)*CL |

| <sup>t</sup> shf | NOSH, SHL, SHR or SHIN to any F[i] or SHOUT output                  | <sup>t</sup> shf = 0.80 + 0.039*Nbits + 1.35*CL                            |

Cell Width (mils) = 21.67 + 3.31\*ShiftCell Height (mils) = 2.94 + 2.07\*Nbits + 0.78\*Shift

#### **TIMING EXAMPLES**

# Timing for a 16-Bit ALU Without Post Shift

|        |                                              | NOMINAL<br>VDD=5V |      | WORST CASE<br>VDD=4.5V |     |       |     |          |     | UNITS |

|--------|----------------------------------------------|-------------------|------|------------------------|-----|-------|-----|----------|-----|-------|

| SYMBOL | PARAMETER                                    | TA=               | :25C | TA=                    | 70C | TA=85 |     | 85C TA=1 |     | 2     |

|        |                                              | MIN               | MAX  | MIN                    | MAX | MIN   | MAX | MIN      | MAX |       |

| tifa   | From A, B to F, SHOUT<br>Arithmetic Mode     |                   | 11   |                        | 22  |       | 23  |          | 26  | ns    |

| tica   | From A, B to COUT, COUTM1<br>Arithmetic Mode |                   | 11   |                        | 23  |       | 24  |          | 27  | ns    |

| tcfa   | From CINB to F, SHOUT<br>Arithmetic Mode     |                   | 8    |                        | 17  |       | 17  |          | 19  | ns    |

| tcca   | From CINB to COUT, COUTM1<br>Arithmetic Mode |                   | 9    |                        | 19  |       | 19  |          | 22  | ns    |

| tifl   | From A, B to F, SHOUT<br>Logic Mode          |                   | ц    |                        | 8   |       | 9   |          | 10  | ns    |

| tsf    | From SO-S3, MODE to F, SHOUT                 |                   | 10   |                        | 20  |       | 21  |          | 24  | ns    |

Switching Characteristics (Input tr, tf=1.4ns, CL=0.5pF)

# Timing for an 8-Bit ALU With Post Shift

|                  |                                              | 1   | NOMINAL<br>VDD=5V |     | WORST CASE<br>VDD=4.5V |     |      |         |     |      |

|------------------|----------------------------------------------|-----|-------------------|-----|------------------------|-----|------|---------|-----|------|

| SYMBOL           | PARAMETER                                    | TA= | :25C              | TA= | :70C                   | TA= | :85C | TA=125C |     | UNIT |

|                  |                                              | MIN | MAX               | MIN | MAX                    | MIN | MAX  | MIN     | MAX |      |

| tifa             | From A, B to F, SHOUT<br>Arithmetic Mode     |     | 10                |     | 20                     |     | 21   |         | 24  | ns   |

| tica             | From A, B to COUT, COUTM1<br>Arithmetic Mode |     | 10                |     | 21                     |     | 22   |         | 25  | ns   |

| tcfa             | From CINB to F, SHOUT<br>Arithmetic Mode     |     | 7                 |     | 15                     |     | 16   |         | 18  | ns   |

| tcca             | From CINB to COUT, COUTM1<br>Arithmetic Mode |     | 8                 |     | 17                     |     | 17   |         | 19  | ns   |

| tifl             | From A, B to F, SHOUT<br>Logic Mode          |     | 5                 |     | 10                     |     | 10   |         | 12  | ns   |

| t <sub>sf</sub>  | From SO-S3, MODE to F, SHOUT                 |     | 10                |     | 21                     |     | 22   |         | 25  | ns   |

| <sup>t</sup> shf | From NOSH, SHL, SHR, SHIN to F, SHOUT        |     | 2                 |     | 4                      |     | đ    |         | 4   | ns   |

Switching Characteristics (Input tr, tf=1.4ns, CL=0.5pF)

#### **APPLICATION NOTES**

#### Use Of The Shift Function

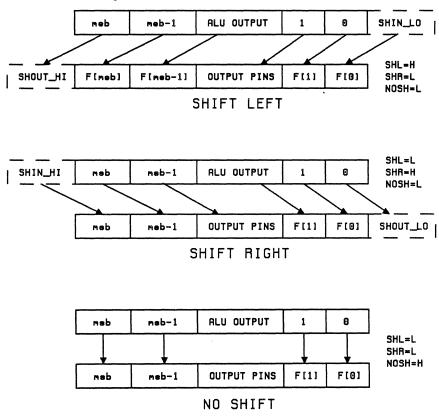

The optional shift function allows more complicated functions than are possible with just the '181 compatible operations.

The three shift control lines (SHL, SHR, and NOSH) control the shift operation. Only one of these lines may be asserted active high at a time. The physical implementation uses three CMOS transmission gates per output. The three control lines select one of the three transmission gates per output. If all three control lines are pulled low, the output bus will be tristated.

The SHIN and SHOUT lines allow shift-in and shift-out at the ends of the output bus. For instance, when shifting left using the SHL control, the signal level on the SHIN\_LO will appear on F[0], and the most significant bit of the ALU operation will appear on SHOUT\_HI. The SHOUT\_LO output will be tristated in this case. Similarly, a shift right operation will take the signal from SHIN\_HI to F[msb], and the least significant ALU bit will appear on SHOUT\_LO.

These operations are shown in Figure A-1.

Figure A-1 Shift operations

#### Limitations

QUICKSIM Save and Restore functions will not currently operate with generated cells.

# **VS1500 Binary Counter**

#### **GENERAL DESCRIPTION**

- The counter is an n-bit synchronous (positive edge triggered) counter

- Allowed functions include count up, count down, load, clear and hold

- Optionally tristatable outputs

- An optional comparison circuit can be included to output a high level when the output bus matches an external compare bus

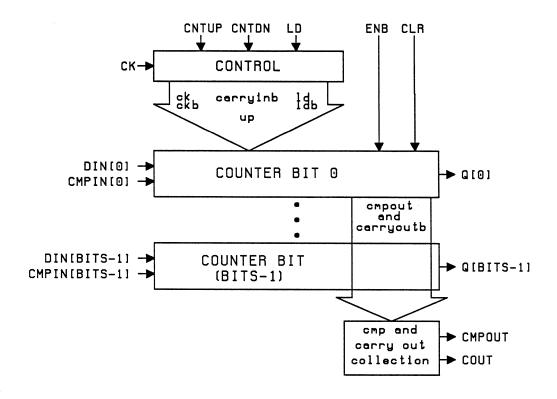

CNTRGEN is a positive edge triggered binary counter. The load, count up and count down operations occur synchronously with the positive clock edge. The clear operation is asynchronous. Carry out and compare out signals are generated from the Q outputs and will have an additional delay from the positive clock edge. The compare and carry out signals can be fed back as load or clear signals, provided the minimum clock period and setup times are satisfied.

#### **SYMBOL**

The symbol for CNTRGEN will be unique for each configuration. An example is given here only for reference.

| BITS                        | = N                     |

|-----------------------------|-------------------------|

| DIN(N)<br>CMPIN(N)<br>CLR   | Q (N)<br>COUT<br>CMPOUT |

| CNTR                        | GEN                     |

| CNTUP<br>CNTDN<br>ENB<br>CK |                         |

#### **INPUT PARAMETER RANGES**

| INPUT<br>PARAMETER | ALLOWED<br>RANGE | EXPLANATION                                                   |

|--------------------|------------------|---------------------------------------------------------------|

| BITS               | 4 - 32           | Number of bits in counter.                                    |

| CNTUP_OPT          | 0 or 1           | 0: No count up option 1: Count up option*                     |

| CNTDN_OPT          | 0 or 1           | 0: No count down option 1: Count down option*                 |

| LOAD_OPT           | 0 or 1           | 0: No parallel data load<br>1: Parallel data load             |

| COMPARE_OPT        | 0 or 1           | No compare function     Compare output to external bus option |

| TRISTATE_OPT       | 0 or 1           | O: Always driving outputs     Tristatable outputs             |

<sup>\*</sup> One or both of CNTUP\_OPT and CNTDN\_OPT must be selected

# **CNTRGEN**

ViGen CONFIGURABLE FUNCTION

#### INPUTS/OUTPUTS

| PIN NAME  | FUNCTION                                         |      | CAP<br>(pF)      |

|-----------|--------------------------------------------------|------|------------------|

| INPUTS:   |                                                  |      |                  |

| DIN (N)   | Parallel load input data bus                     | OPT  | 0.118            |

| CMPIN (N) | Compare input bus                                | OPT  | 0.096            |

| CLR       | Clear - resets all Q outputs to 0                | REQ  | 0.054            |

| LD        | Load from DIN (N) on rising edge of CK           | OPT  | 0.054            |

| CNTUP     | Count up on rising edge of CK                    | OPT* | 0.060#<br>0.138& |

| CNTDN     | Count down on rising edge of CK                  | OPT* | 0.080            |

| ENB       | Output enable, tristates Q when high             | OPT  | 0.054            |

| CK        | Clock                                            | REQ  | 0.054            |

| OUTPUTS:  |                                                  |      |                  |

| Q (IN)    | Output bus                                       | REQ  | 0.271            |

| COUT      | Carry out from most significant bit              | REQ  |                  |

| CMPOUT    | Output compare (high if CMPIN bus matches Q bus) | OPT  |                  |

<sup>\*</sup> One or both of CNTUP\_OPT and CNTDN\_OPT is required

<sup>#</sup> CNTUP\_OPT only

<sup>&</sup>amp; CNTUP\_OPT and CNTDN\_OPT both selected

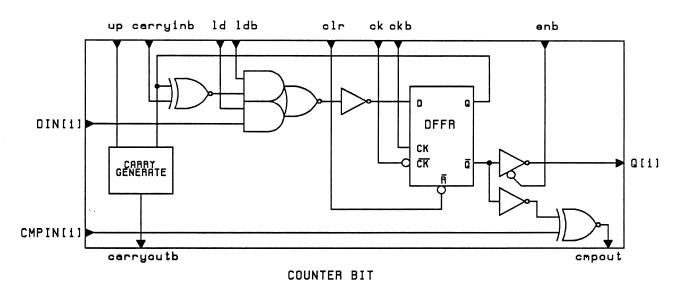

# **FUNCTIONAL BLOCK DIAGRAM**

# **CNTRGEN**

ViGen CONFIGURABLE FUNCTION

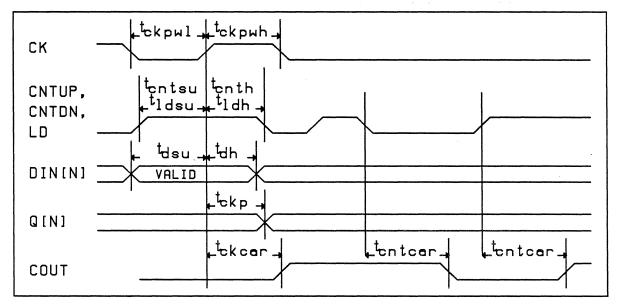

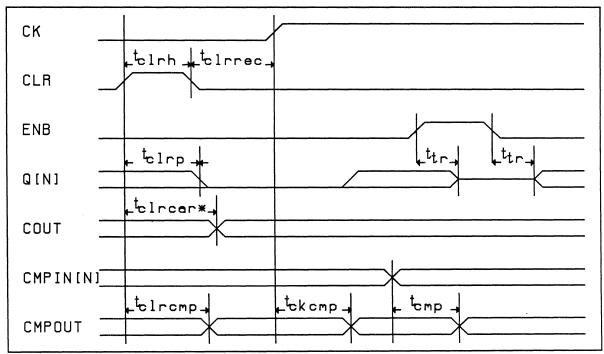

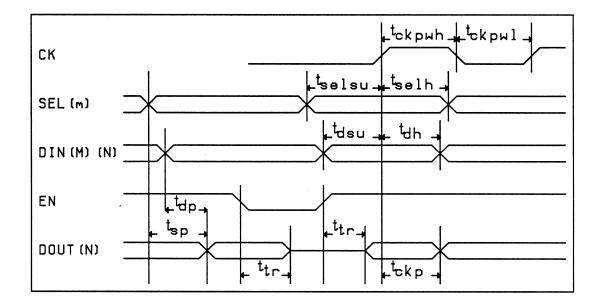

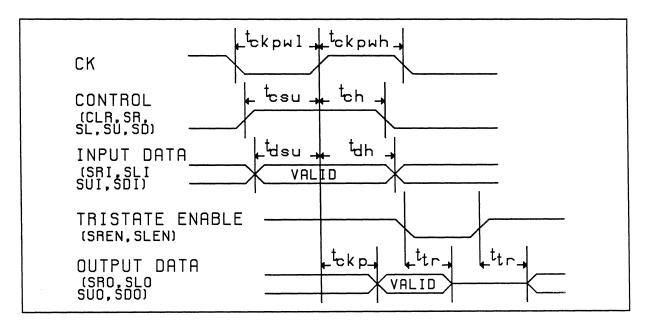

#### **AC WAVEFORMS**

### **Counting and Loading**

# Clear, Compare and Tristate Operations

\* COUT falling applies in count up mode and COUT rising applies in count down mode.

# TIMING PARAMETERS AND CELL SIZE AS FUNCTIONS OF INPUT PARAMETERS

- 1. The input parameters are: BITS, CNTUP\_OPT, CNTDN\_OPT, LOAD\_OPT, COMPARE\_OPT, and TRISTATE\_OPT. CL is output capacitance in pF.

- 2. Timing parameters are specified for nominal process, Vdd=5.0 volts, and temperature = 25°C. See the NCR ASIC Data Book for information on derating factors for process, voltage and temperature. The (tplh) notation refers to the output switching from low to high, and (tphl) from high to low.

| PARAM                                   | DESCRIPTION                                       | TYPICAL VALUE (ns)                                         |

|-----------------------------------------|---------------------------------------------------|------------------------------------------------------------|

| <sup>t</sup> cntsu<br><sup>t</sup> cnth | CNTUP, CNTDN set up time                          | 5.13 + 0.258*BITS + 5.74*CNTDN_OPT                         |

| cntn                                    | CNTUP, CNTDN hold time                            | 0                                                          |

| <sup>t</sup> Idsu                       | LD setup time                                     | 5.34                                                       |

| <sup>t</sup> ldh                        | LD hold time                                      | 0                                                          |

| <sup>t</sup> dsu                        | DIN setup time                                    | 5.12                                                       |

| <sup>t</sup> dh                         | DIN hold time                                     | 0                                                          |

| <sup>t</sup> ckpwl                      | Min CK pulse width (low)                          | 6.66 + 0.137*BITS + 0.65*CNTDN_OPT                         |

| <sup>t</sup> ckpwh                      | Min CK pulse width (high)                         | 6.66 + 0.137*BITS + 0.65*CNTDN_OPT                         |

| <sup>t</sup> cIrh                       | Min CLR pulse width (high)                        | 6.66 + 0.137*BITS + 0.65*CNTDN_OPT                         |

| <sup>t</sup> cIrrec                     | CLR recovery time (CLR release to rising CK edge) | 6.66 + 0.137*BITS + 0.65*CNTDN_OPT                         |

| <sup>t</sup> ckp                        | CK to Q delay                                     | <sup>t</sup> plh = 5.06 + 0.022*BITS + 0.18*COMPARE_OPT +  |

|                                         |                                                   | 0.80*TRISTATE_OPT + (0.80 + 1.22*TRISTATE_OPT)*CL          |

|                                         |                                                   | <sup>t</sup> phI = 5.39 + 0.021*BITS + 0.25*COMPARE_OPT +  |

|                                         |                                                   | 1.01*TRISTATE_OPT + (0.86 + 0.83*TRISTATE_OPT)*CL          |

| <sup>t</sup> tr                         | ENB to tristate on or                             | <sup>t</sup> plh = 2.53 + 0.020*BITS + 2.13*CL             |

|                                         | off delay                                         | <sup>t</sup> phI = 2.86 + 0.020*BITS + 1.51*CL             |

| <sup>t</sup> ckcar                      | CK to carry out delay                             | <sup>t</sup> pIh = 8.90 + 0.308*BITS + 0.32*TRISTATE_OPT + |

|                                         |                                                   | 2.38*CNTDN_OPT + 1.01*CL                                   |

|                                         |                                                   | $^{\rm t}$ phi = 8.90 + 0.042*BITS + 0.54*TRISTATE_OPT +   |

|                                         |                                                   | 1.19*CNTDN_OPT + 0.83*CL                                   |

| <sup>t</sup> cmp                        | CMPIN to CMPOUT delay                             | <sup>t</sup> plh = 2.92 + 0.116*BITS + 3.18*CL             |

|                                         |                                                   | $^{t}$ phl = 3.70 + 0.135*BITS + 0.57*CL                   |

# **CNTRGEN**

ViGen CONFIGURABLE FUNCTION

```

<sup>t</sup>ckcmp

CK to CMPOUT delay

^{t}plh = ^{t}ckp (Low to High) + 3.44 + 0.68*BITS + 3.18*CL

TRISTATE_OPT = 0:

^{t}phI = ^{t}ckp (High to Low) + 1.10 + 0.035*BITS + 0.57*CL

^{t}plh = 8.44 + 0.190*BITS + 3.18*CL

TRISTATE_OPT = 1:

^{t}phi = 6.85 + 0.069*BITS + 0.57*CL

<sup>t</sup>clrp

^{t}phi = 4.31 + 0.083*BITS + 0.67*COMPARE_OPT +

CLR to Q delay

1.44*TRISTATE_OPT + (0.80 + 1.22*TRISTATE_OPT)*CL

tplh = 11.30 + 0.336*BITS + 0.47*TRISTATE_OPT + 1.01*CL

<sup>t</sup> clrcar

CLR to COUT delay

^{t}phI = 10.39 + 0.031*BITS + 0.47*TRISTATE_OPT +

1.37*CNTDN_OPT + 0.83*CL

tclrcmp CLR to CMPOUT delay

^{t}plh = ^{t}clrp + 2.14 + 0.162*BITS + 3.18*CL

^{t}phi = ^{t}cirp + 0.97 + 0.038*BiTS + 0.57*CL

<sup>t</sup> cntcar

tplh = 2.47 + 0.353*BITS + 6.22*CNTDN_OPT + 1.01*CL

CNTUP to COUT delay

^{t}phI = 2.73 + 0.097*BITS + 1.16*CNTDN_OPT + 0.83*CL

<sup>t</sup> cntcar

CNTDN to COUT delay

^{t}plh = 4.55 + 0.360*BITS + 1.01*CL

^{t}phI = 4.29 + 0.093*BITS + 0.83*CL

Cell Width (mils)

for BITS \leq 16:

9.7 + 2.1*LOAD_OPT + 2.6*COMPARE_OPT + 1.0*TRISTATE_OPT + (offset)

offset = (0 CNTUP_OPT only)

(0.5 CNTDN_OPT only)

(1.3 CNTUP_OPT and CNTDN_OPT)

for BITS > 16:

19.2 + 4.1*LOAD_OPT + 5.2*COMPARE_OPT + 2.1*TRISTATE_OPT + (offset)

offset = (0 CNTUP_OPT only)

(1.0 CNTDN_OPT only)

(2.6 CNTUP_OPT + CNTDN_OPT)

for BITS ≤ 16

Cell Height (mils) = 3.6 + 3.13*BITS

= 3.6 + 1.56*BITS

for even BITS > 16

= 3.6 + 1.56*(BITS + 1) for odd BITS > 16

```

# TIMING EXAMPLES:

# 8-Bit Up/Down Counter with Compare and Tristate

| 8 BIT UP/DOWN COUNTER with |                            |                 | NOMINAL WORST CASE |             |      |             | ဟ        |             |      |             |       |

|----------------------------|----------------------------|-----------------|--------------------|-------------|------|-------------|----------|-------------|------|-------------|-------|

| COMP                       | ARE_OPT and TRISTATE_OP    | <u> </u>        |                    | <b>=5</b> V |      |             | VDD=4.5V |             |      |             | UNITS |

| SYMBOL                     | PARAMETER                  |                 |                    | 25C         |      | -70C        |          | 85C         |      | 125C        | S     |

|                            |                            |                 |                    | MAX         | MIN  | MAX         | MIN      |             |      | MAX         |       |

| tckp                       | CK to Q delay              | LH              |                    | 7.1         |      | 14.5        |          | 15.1        |      | 17.0        | ns    |

|                            |                            | HL              |                    | 7.7         |      | 15.7        |          | 16.4        |      | 18.4        |       |

| tckcar                     | CK to COUT delay           | LH              |                    | 14.6        |      | 29.9        |          | 31.2        |      | 35.0        | ns    |

| <u> </u>                   |                            | HL              |                    | 11.4        |      | 23.3        |          | 24.4        |      | 27.3        |       |

| t <sub>ckcmp</sub>         | CK to CMPOUT delay         | LH              |                    | 11.6        |      | 23.7        |          | 24.7        |      | 27.7        | ns    |

|                            |                            | HL              |                    | 7.7         |      | 15.8        |          | 16.5        |      | 18.4        |       |

| temp                       | CMPIN to CMPOUT delay      | LH              |                    | 5.4         |      | 11.1        |          | 11.6        |      | 13.1        | ns    |

|                            | _                          | HL              |                    | 5.1         |      | 10.4        |          | 10.8        |      | 12.2        |       |

| ttr                        | ENB to Q                   | LH              |                    | 3.8         |      | 7.7         |          | 8.0         |      | 9.0         | ns    |

| tclrp                      | (on or off)                | HL<br>HL        |                    | 3.8<br>8.1  |      | 7.7<br>16.6 |          | 8.1<br>17.3 |      | 9.1<br>19.4 |       |

| SCILD                      | CLR to Q delay             | LH              |                    | 15.0        |      | 30.7        |          | 32.0        |      | 35.9        | ns    |

| tolrear                    | CLR to COUT delay          | HL              |                    | 12.9        |      | 26.4        |          | 27.6        |      | 30.9        | ns    |

| <b>.</b>                   |                            | LH              |                    | 13.1        |      | 26.9        |          | 28.1        |      | 31.5        |       |

| tclrcmp                    | CLR to CMPOUT delay        | HL              |                    | 9.7         |      | 19.8        |          | 20.7        |      | 23.2        | ns    |

|                            |                            | <u>nl</u><br>LH |                    | 12.0        |      | 24.6        |          | 25.7        |      | 28.8        |       |

| tontoar                    | CNTUP to COUT delay        | HL              |                    | 5.1         |      | 10.4        |          | 10.9        |      | 12.2        | ns    |

| 1                          | •                          | LH              |                    | 7.9         |      | 16.3        |          | 17.0        |      | 19.0        |       |

| cntcer                     | CNTDN to COUT delay        | HL              |                    | 5.4         |      | 11.2        |          | 11.7        |      | 13.1        | ns    |

| tontsu                     | CNTUP/CNTDN setup time     | 111             | 12.9               |             | 26.5 |             | 27.7     |             | 31.0 |             | ns    |

| tenth                      | CNTUP/CNTDN hold time      |                 | 0                  |             | 0    |             | 0        |             | 0    |             | ns    |

| tclrh                      | Min CLR pulse width (high) |                 | 8.4                |             | 17.2 |             | 18.0     |             | 20.2 |             | ns    |

|                            | CLR recovery time          |                 | 8.4                |             | 17.2 |             | 18.0     |             | 20.2 |             | ns    |

| t <sub>ckpwl</sub>         | Min CK pulse width (low)   |                 | 8.4                |             | 17.2 |             | 18.0     |             | 20.2 |             | ns    |

| t <sub>ckpwh</sub>         | Min CK pulse width (high)  |                 | 8.4                |             | 17.2 |             | 18.0     |             | 20.2 |             | ns    |

Switching Characteristics (Input tr, tf=1.4ns, CL=0.5pF)

#### 16-Bit Up Counter with Load

| 16 BIT             | UP COUNTER with LOAD_OPT   |     | 1INAL<br>D=5V | WORST CASE<br>VDD=4.5V |            |      |                                         |      | ITS  |    |

|--------------------|----------------------------|-----|---------------|------------------------|------------|------|-----------------------------------------|------|------|----|

| SYMBOL             | PARAMETER                  | TA: | TA=25C TA=70C |                        | TA=85C TA= |      |                                         | 125C | UNIT |    |

| SIMBUL             | ranancion                  | MIN | MAX           | MIN                    | MAX        | MIN  | MAX                                     | MIN  | MAX  |    |

| + .                | CK to Q output delay       | 1   | 5.8           |                        | 11.9       |      | 12.4                                    |      | 13.9 |    |

| <sup>t</sup> ckp   | CK to a parbar delay       | _   | 6.2           |                        | 12.6       |      | 13.2                                    |      | 14.8 | ns |

| tckcar             | CK to COUT delay           | 1   | 14.3          |                        | 29.4       |      | 30.7                                    |      | 34.4 |    |

| CKCGP              | CK to Cool delay           | _   | 10.0          |                        | 20.5       |      | 21.4                                    |      | 24.0 | us |

| tclrp              | CLR to Q delay H           | _   | 6.0           |                        | 12.4       |      | 12.9                                    |      | 14.5 | ns |

| tclrcar            | CLR to COUT delay H        | _   | 11.3          |                        | 23.2       |      | 24.2                                    |      | 27.1 | ns |

| t                  | CNTUD 1 COUT 1 3           | 1   | 8.6           |                        | 17.7       |      | 18.5                                    |      | 20.7 |    |

| chicar             | CNTUP to COUT delay H      | _   | 4.7           |                        | 9.6        |      | 10.1                                    |      | 11.3 | ns |

| tdsu               | DIN setup time             | 5.1 |               | 10.5                   |            | 11.0 |                                         | 12.3 |      | ns |

| <sup>t</sup> dh    | DIN hold time              | 0   |               | 0                      |            | 0    |                                         | 0    |      | ns |

| tcntsu             | CNTUP set up time          | 9.3 |               | 19.0                   |            | 19.8 |                                         | 22.2 |      | ns |

| tenth              | CNTUP hold time            | 0   |               | 0                      |            | 0    |                                         | 0    |      | ns |

| tldsu              | LD setup time              | 5.3 |               | 10.9                   |            | 11.4 |                                         | 12.8 |      | ns |

| <sup>t</sup> ldh   | LD hold time               | 0   |               | 0                      |            | 0    |                                         | 0    |      | ns |

| tclrrec            | CLR recovery time          | 8.9 |               | 18.1                   |            | 18.9 | *************************************** | 21.2 |      | ns |

| tclrh              | Min CLR pulse width (high) | 8.9 |               | 18.1                   |            | 18.9 |                                         | 21.2 |      | ns |

| tckpwl             | Min CK pulse width (low)   | 8.9 |               | 18.1                   |            | 18.9 |                                         | 21.2 |      | ns |

| t <sub>ckpwh</sub> | Min CK pulse width (high)  | 8.9 |               | 18.1                   |            | 18.9 |                                         | 21.2 |      | ns |

Switching Characteristics (Input tr, tf=1.4ns, CL=0.5pF)

#### **APPLICATIONS NOTES**

#### **Primary Uses**

CNTRGEN generates synchronous n-bit binary counters. Count up, count down and load functions occur synchronously with the positive clock edge. If none of these control signals are active during a rising clock edge, the counter state will remain unchanged. LD will take priority over CNTUP or CNTDN if LD and either CNTUP or CNTDN are active. If both CNTUP and CNTDN are active, the cell will operate as if it is in count up mode. The clear function is asynchronous and sets all Q outputs low regardless of the state of clock or any control signal. The compare function is implemented with EXNOR gates comparing the Q output to the CMPIN input for each bit. These signals are then collected with an AND function to produce the CMPOUT signal. Note that the CMPIN input is not clocked and, therefore, changes on the CMPIN bus can produce changes on the CMPOUT pin regardless of the state of CK.

Note that if TRISTATE\_OPT = 0, then CMPOUT is a dependent output and the CK to CMPOUT delay is dependent upon the loading and delay to the Q outputs. To calculate the CK to CMPOUT delay, the delay to Q must be calculated first. For a more complete explanation of dependent outputs, refer to the Timing Information section for the VS2000 standard cell library in the NCR ASIC data book.

#### **Naming Conventions**

ViGen will automatically create a default cell name for each unique CNTRGEN configuration. The name of each configurations is encoded in the following manner:

CNT bits X load\_opt cntup\_opt cntdn\_opt compare\_opt tristate\_opt

Therefore, the default names for the two example counters would be:

CNT8X01111 CNT16X11000

#### Limitations

QUICKSIM Save and Restore functions will not currently operate with generated cells.

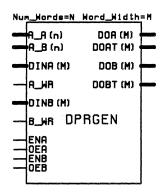

# **DPRGEN**

ViGen CONFIGURABLE FUNCTION

# **VS1500 Dual Port RAM**

#### **GENERAL DESCRIPTION**

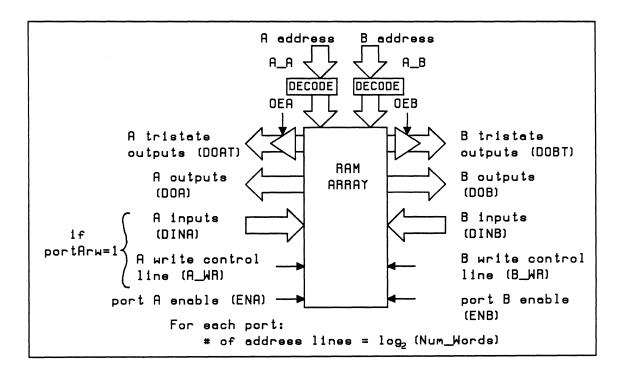

- Variable size RAM array with two independent, bidirectional ports (A,B).

- Read-only option on port A saves area.

- Tristate and always-driving outputs available on both ports.

- Variable number of words and word size, up to 16K bits.

The dual port RAM generator produces a RAM array with two fully independent read/write ports. Each port uses clocked operation to reduce complexity and operating power. Each port is precharged when its enable input is low and can read or write data when its enable input is high. To reduce logic circuitry and save cell area, Port A can be programmed to be a read-only port. Ports must be precharged between successive reads and writes.

#### **SYMBOL**

The symbol for DPRGEN will be unique for each configuration. An example is given here only for reference.

#### **INPUT PARAMETER RANGES**

| INPUT<br>PARAMETER | ALLOWED<br>RANGE     | EXPLANATION                                                                                                                                                                       |

|--------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Num_Words          | 2-2048,<br>even only | Number of data words in the RAM array. The number of address lines for each port will be n = log <sub>2</sub> (Num_Words). Number of bits = Num_Words*Word_Width must be ≤ 16384. |

| Word_Width         | 2 - 32               | Number of bits in a data word. This affects the number of DINA, DINB, DOA, DOAT, DOB, and DOBT pins. Number of bits = Num_Words*Word_Width must be ≤16384.                        |

| PortArw            | 0 or 1               | 0: port "A" is read-only. 1: port "A" is read/write. If port "A" is read-only, then the DINA and A_WR pins are removed from the schematic symbol.                                 |

#### INPUTS/OUTPUTS

Definitions of the DPRGEN inputs and outputs are given in the following table. Input and output pin names are listed in pin-number sequence.

| PIN NAME | DEFINITION                                            |      | CAP      |

|----------|-------------------------------------------------------|------|----------|

| INPUTS:  |                                                       |      |          |

| A_A (n)  | A port address bus (n = log <sub>2</sub> (Num_Words)) | REQ  | 0.159 pF |

| A_B (n)  | B port address bus (n = log <sub>2</sub> (Num_Words)) | REQ  | 0.159 pF |

| DINA (M) | A port data in bus (M = Word_Width)                   | OPT  | 0.113 pF |

| A_WR     | A port read/write control (active high write)         | OPT  | 0.058 pF |

| DINB (M) | B port data in bus (M - Word_Width)                   | REQ  | 0.113 pF |

| B_WR     | B port read/write control (active high write)         | REQ  | 0.058 pF |

| ENA      | A port enable pin                                     | REQ  | 0.167 pF |

| OEA      | DOAT (M) tristate enable pin                          | REQ  | 0.058 pF |

| ENB      | B port enable pin                                     | REQ  | 0.173 pF |

| OEB      | DOBT (M) tristate enable pin                          | REQ  | 0.058 pF |

| OUTPUTS: |                                                       |      |          |

| DOA (M)  | Always-driving A port output bus                      | REQ  |          |

| DOAT (M) | Tristate A port output bus                            | REQ  | 0.105 pF |

| DOB (M)  | Always-driving B port output bus                      | REQ  |          |

| DOBT (M) | Tristate B port output bus                            | REQ* | 0.105 pF |

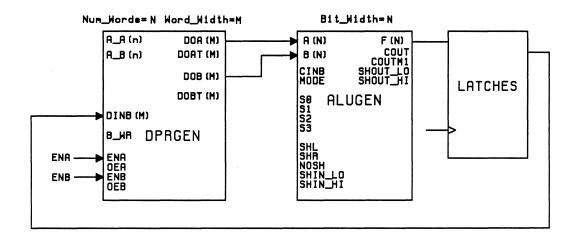

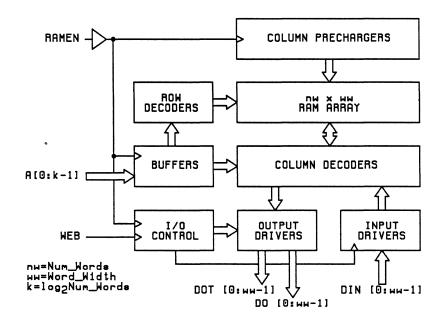

#### **FUNCTIONAL BLOCK DIAGRAM**

# **DPRGEN**

ViGen CONFIGURABLE FUNCTION

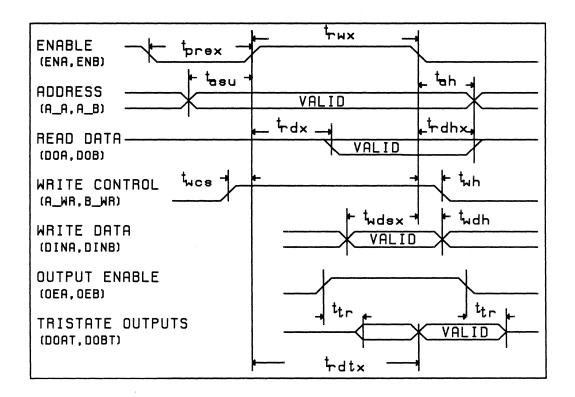

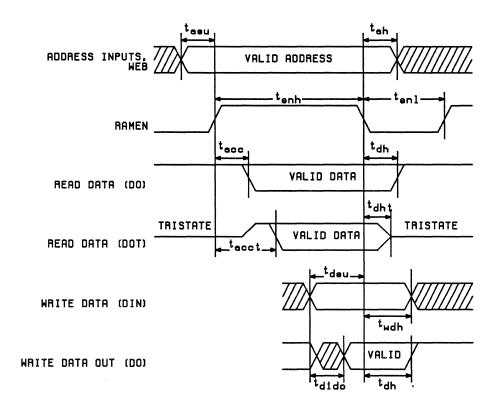

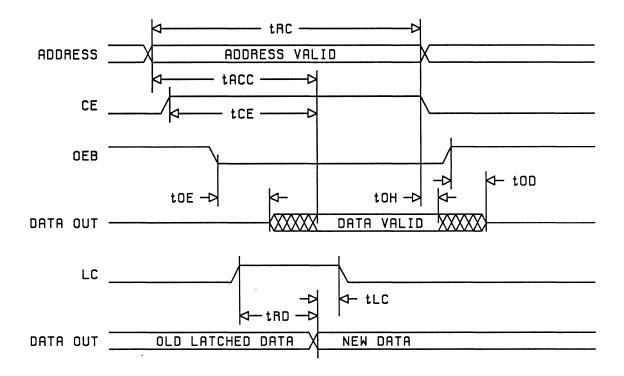

#### **AC WAVEFORMS**

The following waveforms apply equally to port A or port B. If the read only option is chosen for port A (portArw = 0), then ignore waveforms referring to write lines. A suffix of "x" in a timing parameter name should be substituted with "a" or "b" for the appropriate port.

#### **TIMING PARAMETERS**

| <sup>t</sup> prex  | Minimum precharge time for port x                                    |

|--------------------|----------------------------------------------------------------------|

| <sup>t</sup> asu   | Minimum address setup before rising enable (either port)             |

| <sup>t</sup> ah    | Minimum address hold after falling enable (either port)              |

| <sup>t</sup> rdx   | Maximum read access from rising enable on port x                     |

| <sup>t</sup> rdtx  | Maximum read access to tristate outputs from rising enable on port x |

| <sup>t</sup> rdhx  | Maximum read data hold after falling enable on port x                |

| <sup>t</sup> wcs   | Write control setup before rising enable (either port)               |

| <sup>t</sup> wh    | Write control hold after falling enable (either port)                |

| <sup>t</sup> wdsx* | Write data setup before falling enable of port x                     |

| <sup>t</sup> wdh   | Write data hold after falling enable (either port)                   |

| <sup>t</sup> tr    | Output enable to tristate on or off delay (either port)              |

| <sup>t</sup> rwx   | Minimum enable high time of port x for read or write                 |

|                    |                                                                      |

<sup>\*</sup> See Applications Note titled Port Contention which follows.

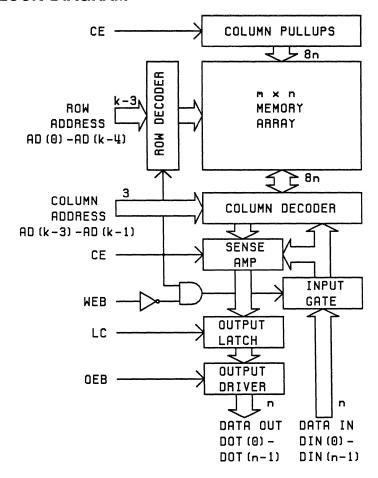

#### TIMING PARAMETERS AND CELL SIZE

- 1. The input parameters are: Num\_Words, Word\_Width, portArw. CL is output capacitance in pF.

- 2. Internal column decode ("coldec") must be determined first. Follow these steps (these are the same steps followed by the layout compiler for DPRGEN):

- a. nbits = Num\_Words\*Word\_Width;

- c. coldec = trial\_ncols/Word\_Width

- d. Round coldec down to nearest valid value (1,2,4,8, or 16)

- e. Word limits on different values of column decode:

Num\_words must be >= 384 for coldec = 16 Num\_words must be >= 80 for coldec = 8

- 3. Num\_Words is internally rounded up to the nearest multiple of 2\*coldec.

- 4. TIMING EQUATIONS & CELL SIZE: (use nrows = Num\_Words/coldec, ncols = Word\_Width\*coldec)

- <sup>t</sup> prea is for port A, <sup>t</sup> preb is for port B, etc. No "a" or "b" suffix means either port.

- All times in nanoseconds and are NOMINAL (Vdd=5.0 volts, T=25°C, Nom. process)

- -See NCR ASIC Data Book for process, voltage, and temperature derating.

| Examp | le: |

|-------|-----|

|-------|-----|

Num\_Words=16, Word\_Width=16,

portArw=1, CL=0 (coldec = 2) tasu = 1.38 + .0656\*nrowsMIN 1.9 ns tah = 0MIN 0.0 ns  $^{t}$  prea = 3.81 + .0419\*nrows + .0497\*ncols + 0.64\*CL MIN 5.7 ns  $^{t}$ preb = 3.77 + .0419\*nrows + .0509\*ncols + 0.63\*CL MIN 5.7 ns <sup>t</sup>rda = 7.18 + .1513\*nrows + .1134\*ncols + 0.99\*CL MAX 12.0 ns <sup>t</sup>rdta = 7.30 + .1513\*nrows + .1134\*ncols + 1.70\*CL MAX 12.1 ns  $^{t}$ rdb = 7.10 + .1538\*nrows + .1197\*ncols + 0.97\*CL MAX 12.2 ns  $^{t}$ rdtb = 6.90 + .1538\*nrows + .1197\*ncols + 1.66\*CL MAX 12.0 ns <sup>t</sup>rdha = <sup>t</sup>prea MAX 5.7 ns trdhb = tpreb MAX 5.7 ns  $t_{tr} = 2.0 + 1.70*CL$ MIN 2.0 ns  $^{t}$  wcs min. = -4.0, max. = 4.0 +4/-4 ns  $^{t}$  wh min. = 0, max. = 4.0 0 to 4.0 ns twdsa = 5.78 + .0538\*nrows + .0291\*ncols (See Note 1) MIN 7.1 ns 7.3 ns  $^{t}$ wdsb = 6.06 + .0500\*nrows + .0250\*ncols (See Note 1) MIN  $^{t}$  wdh = 1.17 + .0075\*nrows + .0138\*ncols MIN 1.7ns  $t_{rwx} = t_{rdx}$ a:12.0ns, b:12.2ns MIN

Cell Width (mils) = 12.683 + 1.924\*nrows + 1.745\*portArw + 0.448\*coldec (coldec > 2)

Cell Width (mils) = 16.876 + 1.924\*nrows + 3.109\*portArw (coldec = 1)

Cell Height (mils) = 11.237 + 1.143\*ncols + 0.963\*log<sub>2</sub>(nrows) + 0.211\*coldec - 0.039\*Word\_Width

Note 1: See Applications Note titled Port Contention for a possible exception to this parameter value.

# **DPRGEN**

ViGen CONFIGURABLE FUNCTION

# TIMING EXAMPLES FOR 16X16 AND 128X8 DUAL PORT RAMS

|                   | 16X16 DUAL PORT RAM (PORT A READ/WRITE) |     | IINAL<br>D=5V |     |        |     | ST CA<br>)=4.5 |     |         | UNITS |  |

|-------------------|-----------------------------------------|-----|---------------|-----|--------|-----|----------------|-----|---------|-------|--|

| SYMBOL            | OL (FORT H REND/MILLE)                  |     | TA=25C        |     | TA=70C |     | TA=85C         |     | TA=125C |       |  |

|                   | PARAMETER                               | MIN | MAX           | MIN | MAX    | MIN | MAX            | MIN | MAX     |       |  |

| tasu              | Address Setup<br>Time Before ENABLE     | 2   |               | f   |        | ſŤ  |                | 5   |         | us    |  |

| tah               | Address Hold<br>Time after ENABLE       | 0   |               | 0   |        | 0   |                | 0   |         | ns    |  |

| tprea             | Precharge Time                          | 6   |               | 12  |        | 13  |                | 15  |         | ns    |  |

| t <sub>preb</sub> | Precharge Time                          | 6   |               | 12  |        | 13  |                | 15  |         | ns    |  |

| trwa              | Read or Write Enable High               | 13  |               | 26  |        | 27  |                | 30  |         | ns    |  |

| trwb              | Read or Write Enable High               | 13  |               | 26  |        | 27  |                | 30  |         | ns    |  |

| trde              | Read Access Time                        |     | 13            | 26  |        | 27  |                | 30  |         | ns    |  |

| trdb              | Read Access Time                        |     | 13            | 26  |        | 27  |                | 30  |         | ns    |  |

| trdte             | Tristate Read Access Time               |     | 13            | 27  |        | 28  |                | 31  |         | ns    |  |

| <sup>t</sup> rdtb | Tristate Read Access Time               |     | 13            | 26  |        | 27  |                | 31  |         | ns    |  |

| <sup>t</sup> rdha | Read Data Hold Time                     |     | 6             |     | 12     |     | 13             |     | 15      | ns    |  |

| <sup>t</sup> rdhb | Read Data Hold Time                     |     | 6             |     | 12     |     | 13             |     | 15      | กร    |  |

| ttr               | Tristate and Untristate Time            |     | 3             | 6   |        | 6   |                | 7   |         | ns    |  |

| twcs              | Write Control Setup                     | -4  | Ц             | -8  | 8      | -9  | 9              | -10 | 10      | ns    |  |

| t <sub>wh</sub>   | Write Control Hold                      | 0   | ų             |     | 8 .    |     | 9              |     | 10      | ns    |  |

| twdsa             | Write Data Setup                        | 7   |               | 15  |        | 15  |                | 17  |         | ns    |  |

| t <sub>wdsb</sub> | Write Data Setup                        | 7   |               | 15  |        | 16  |                | 17  |         | ns    |  |

| t <sub>wdh</sub>  | Write Data Hold                         | 2   |               | 3   |        | ц   |                | 4   |         | ns    |  |

Switching Characteristics (Input tr, tf=1.4ns, CL=0.5pF)

#### DPRGFN

ViGen CONFIGURABLE FUNCTION

|                          | 128X8 DUAL PORT RAM (PORT A READ-ONLY) |    | IINAL<br>)=5V |    |        |    | T CA   |     |    | UNITS |

|--------------------------|----------------------------------------|----|---------------|----|--------|----|--------|-----|----|-------|

| SYMBOL                   | OL TONY H NERD-ONE IT                  |    | TA=25C        |    | TA=70C |    | TA=85C |     |    |       |

|                          | PARAMETER                              |    | MAX           |    | MAX    |    | MAX    |     |    | ا د   |

| tasu                     | Address Setup<br>Time Before ENABLE    | 2  |               | 5  |        | 5  |        | 6   |    | ns    |

| tah                      | Address Hold<br>Time after ENABLE      | 0  |               | 0  |        | 0  | ,      | 0   |    | ns    |

| t <sub>pree</sub>        | Precharge Time                         | 8  |               | 16 |        | 17 |        | 19  |    | US    |

| <sup>t</sup> preb        | Precharge Time                         | 8  |               | 16 |        | 17 |        | 19  |    | ns    |

| t <sub>rwa</sub>         | Read Enable High                       | 17 |               | 36 |        | 37 |        | 42  |    | ns    |

| t <sub>rwb</sub>         | Read or Write Enable High              | 18 |               | 36 |        | 38 |        | 43  |    | ns    |

| <sup>t</sup> rd <b>e</b> | Read Access Time                       |    | 17            | 36 |        | 37 |        | 42  |    | ns    |

| <sup>t</sup> rdb         | Read Access Time                       |    | 18            | 36 |        | 38 |        | 43  |    | SU    |

| trdta                    | Tristate Read Access Time              |    | 18            | 37 |        | 38 |        | 43  |    | ns    |

| t <sub>rdtb</sub>        | Tristate Read Access Time              |    | 18            | 37 |        | 38 |        | 43  |    | ns    |

| <sup>t</sup> rdha        | Read Data Hold Time                    |    | 8             |    | 16     |    | 17     |     | 19 | ns    |

| <sup>t</sup> rdhb        | Read Data Hold Time                    |    | 8             |    | 16     |    | 17     |     | 19 | ns    |

| ttr                      | Tristate and Untristate Time           |    | 3             | 6  |        | 6  |        | 7   |    | ns    |

| tucs                     | Write Control Setup                    | -4 | Ц             | -8 | 8      | -9 | 9      | -10 | 10 | ns    |

| t <sub>wh</sub>          | Write Control Hold                     | 0  | Ų             |    | 8      |    | 9      |     | 10 | ns    |

| t <sub>wdsb</sub>        | Write Data Setup                       | 8  |               | 17 |        | 18 |        | 20  |    | ns    |

| <sup>t</sup> udh         | Write Data Hold                        | 2  |               | 4  |        | 5  |        | 5   |    | ns    |

Switching Characteristics (Input tr, tf=1.4ns, CL=0.5pF)

ViGen CONFIGURABLE FUNCTION

#### **APPLICATION NOTES**

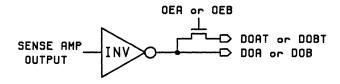

#### Using the Tristate Outputs DOAT(i) and DOBT(i)

The tristate outputs of the dual port RAM generator are not implemented in quite the same way as in some other NCR supercells. Figure 1 shows the circuits used for both always-driving outputs (DOA(i) and DOB(i)) and the tristate outputs. Instead of a full CMOS transmission gate for the tristate outputs, a single N-channel transistor is used to reduce circuit area. The effect of this is that the tristate outputs, when driven high, will not reach a full VDD level. Instead, they will reach a level of about 3.3 volts when VDD is 5.0 volts. This is enough to be considered a logic high for subsequent gate inputs, but there will be reduced noise margin and increased DC power dissipation caused by this non-rail level.

Figure 1 Tristate output circuit

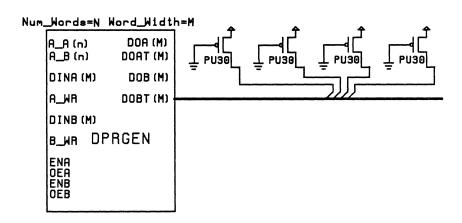

For this reason it is important to use pull-up cells on each tristate output line (see Figure 2). This is good design practice for any tristate line used in semicustom design. The PU30 cell is not meant to provide a valid logic level on a bus line, but only to provide a "default" level for those times when it is not actively driven by anything else.

Figure 2 Tristate bus pullups

The pullups will cause no problem with "late 1's" on the tristate outputs. During the precharge phase for each port, the internal bit lines and sense amp inputs are pulled high. This causes the always—driving outputs to also go high during precharge. If the output enable line (OEA or OEB) is asserted at the beginning of a read phase, then the tristate outputs will also stay high if they were not immediately previously driven low by another gate. There is no possibility of a glitch on this line (and therefore losing the good high

level) since the read access time for a "1" is actually zero. Only 0's in the data word being read have non-zero access time.

#### **Reducing AC Power Dissipation**

For most designers, the AC power dissipation of CMOS semicustom chips is not a problem needing consideration since it is very low compared to bipolar or NMOS implementations. Some applications, though, need low AC operating power as well.

If the address lines are allowed to switch several times before becoming stable at the address setup time, then excess AC power dissipation will occur due to the large capacitances on the internal address lines and their complements. This kind of power dissipation is calculated as:

$P=CV^2f$ , P=power  $C=total\ driven\ capacitance$   $V=voltage\ swing\ (=VDD)$  $f=switching\ frequency$

Since C is fixed inside the RAM, reducing this power can only be done by reducing the number of times that the address lines switch. This can be done by latching the address lines externally to the dual-port RAM.

#### **Port Contention**

The A and B ports of the dual-port RAM are meant to be independent in operation. The possibility of contention between the two ports does exist, however, and can happen in the following combinations:

- 1. One port's write cycle overlaps the other port's read cycle to the same address (read/write contention).

- 2. Both ports' write cycles overlap to the same address (write/write contention).

Note that port contention doesn't exist if both ports are reading from the same address. Discrete, dual-port RAM chips contain contention logic that detects when both ports are attempting to access the same address (whether reading or writing). The port which drives this address second is given a busy signal by the contention logic, which inhibits it from actually reading or writing to that address. When the first port has switched to a different address, the busy signal to the second port is deactivated.

This generator does not contain such contention logic, so care must be taken to assure correct operation. The benefit to not including this logic is more flexible operation. For instance, two-port reads can occur from the same address without one port being locked out. This is important for register files, for an example see Figure 4.

### **DPRGEN**

ViGen CONFIGURABLE FUNCTION

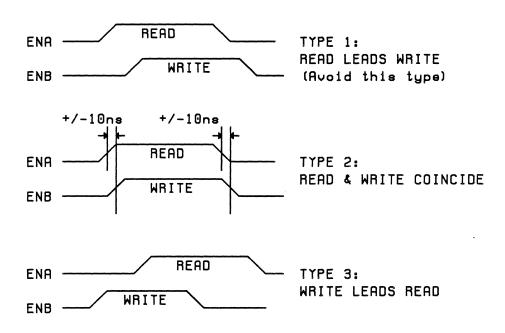

Read/write contention can happen in three different ways (see Figure 3), and only one of them causes real contention. Of the three read/write overlaps shown, only the first, where the read on one port isn't complete before the other port starts to write, is a case of real port contention and must be avoided. In the second case, where both enables overlap within +/- 10ns, there will be no contention if the data to be written is stable from the beginning of the write enable. This overrides the write data setup time parameter in the AC characteristics table. In the third case, the data written to the addressed word will be stable in time for the reading port to access it, so no contention occurs.

Figure 3 Read/Write port contention

Write/write combinations will always cause contention, since the data in the addressed word will contain unknown data except when both ports write identical data. If the enable signals ENA and ENB don't overlap their high times at all, then there is no contention.

#### **Designing for Testability**

A test program for a semicustom chip must be able to verify that all circuit functions operate correctly. This implies both functional correctness (correct design) and fault detection (the circuit was manufactured without defects). Several methods exist for a achieving both of these goals, all of which involve some trade-off between degree of checking and the amount of extra logic required. These include:

- 1. Multiplex part pins to the address and data pins in a test mode.

- 2. Use scan registers to serially shift in address and input data, and shift out output data.

See the NCR VS2000 Standard Cell Library Databook, Section 6, "Designing for Testability" for more information.

#### **Example of Register File Used With ALU**

Figure 4 DPRGEN as a register file source for ALU operands

In Figure 4, the two operands for the ALU are read simultaneously from the A and B ports of the RAM, and then the ALU result is written back to the RAM through port B on the next cycle. The "PortArw" parameter for this RAM is set to "0" because the A port never has data written to it. There will never be any possibility of port contention because of this. The enable signals for each port can be tied together, which causes a dummy read of port A when the result is being written back through port B, or they can be separated as shown. Tying them together requires less logic to generate the ENA signal, but increases the operating power dissipation.

VIGen CONFIGURABLE FUNCTION

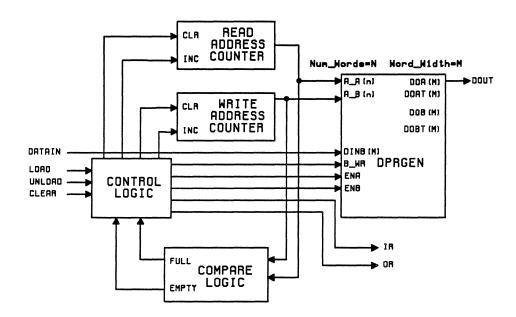

#### **Example of FIFO**

Figure 5 shows an implementation of a FIFO using the dual-port RAM supercell. Less sophisticated shift register type FIFOs can be built using the "SHFTGEN" supercell.

Figure 5 DPRGEN used in a FIFO buffer

Data is loaded with the LOAD input from DATAIN, and data is led out to the DOUT bus using UNLOAD. Address comparison determines whether the buffer is full (read address equals write address plus 1) or empty (write address equals read address plus 1). The IR flag (Input Ready) indicates that the FIFO is not full, and the OR flag (Output Ready) indicates the not empty condition.

#### **Naming Conventions**

ViGen will automatically create a default cell name for each unique DPRGEN configuration with the configuration information encoded in the following manner:

Therefore, the default names for the two example configurations would be:

DPR16X16W DPR128X16NW

#### Limitations

QUICKSIM Save and Restore functions will not currently operate with generated cells.

#### SIMULATION ERROR MESSAGES

Simulation using the Mentor Quicksim simulator is done using a behavioral language model (BLM). This model checks for timing and usage errors during simulation. A listing of the possible error message types and their descriptions is included here.

#### MESSAGES REPORTED BY DPRGEN CONTAIN TWO MAJOR TYPES:

OPERATIONAL ERRORS – caused by invalid operation: Unknown data on control lines. Invalid states/modes.

Improper sequence of states.

#### **OPERATIONAL ERROR SYNTAX**

\$inst\_name: ERROR time\_of\_error error\_description \$inst\_name: action taken by model because of error

\$inst\_name:

#### **OPERATIONAL ERRORS INCLUDE**

UNKNOWNS ON ADDRESSES DURING READ.

UNKNOWNS ON ADDRESSES DURING WRITE.

WRITE TO SAME ADDRESS FROM A&B PORTS SIMULTANEOUSLY.

READ/WRITE TO SAME ADDRESS FROM A&B PORTS OUT OF SPEC (see Port Contention).

NO PRECHARGE BETWEEN SUCCESSIVE READ/WRITE OPERATIONS.

#### example:

\$i21(dprgen): ERROR Time=2013 UNKNOWN ADDRESS ON A PORT DURING WRITE \$i21(dprgen): UNKNOWN DATA WILL BE WRITTEN TO EVERY BLOCK OF RAM ARRAY

\$i21(dprgen): WHICH IS ENABLED.

TIMING ERRORS/WARNINGS – caused by violation of timing specifications in documentation.

Warning messages are produced when transitions occur within a margin delta of specification value.

#### TIMING ERROR/WARNING SYNTAX

\$inst\_name: ERROR msg\_type OF TYPE type\_check spec\_name current\_time

\$inst\_name: control\_pin\_name direction\_of\_edge at transition\_time ns \$inst\_name: data\_pin\_name changed at transition\_time ns

\$inst\_name: spec is spec\_value ns (+margin\_value ns margin)

#### examples:

\$i21(dprgen): ERROR TIMING VIOLATION OF TYPE SETUP t\_WDS Time=2103 ns

\$i21(dprgen): ENB falling at 1987 ns \$i21(dprgen): DINB changed at 1980 ns \$i21(dprgen): spec is 17 ns (+5 ns margin)

\$i21(dprgen): ERROR MARGIN WARNING OF TYPE SETUP \tuberword WDS Time=2103 ns

\$i21(dprgen): ENB falling at 1987 ns \$i21(dprgen): DINB changed at 1967 ns \$i21(dprgen): spec is 17 ns (+5 ns margin) ViGen CONFIGURABLE FUNCTION

# VS1500 FIFO Generator

#### **FEATURES**

- Compiled FIFO cell allows flexible configurations of up to 6K bits

- Maximum word width of 36 bits

- Maximum number of words is 512

- Fully asynchronous Read/Write operation

- User configurable Almost Full flag

- User configurable Almost Empty flag

- · Retransmit ability

#### DESCRIPTION

FIFOGEN produces a compiled first in first out memory block. FIFOGEN is based on a dual port latch memory cell which allows for completely asynchronous read/write operation. Read and write address values are stored in ring counters which may be cleared with the RSb (Reset) input. The read counter may be independently cleared using the RTb (retransmit) input, thus allowing data to be re-read multiple times. FIFOGEN also has status flags for Empty, Full, Almost Empty, and Almost Full. The user may configure the Almost Full and Almost Empty flags to activate any chosen offset from full and empty respectively.

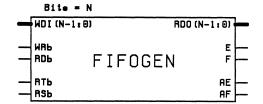

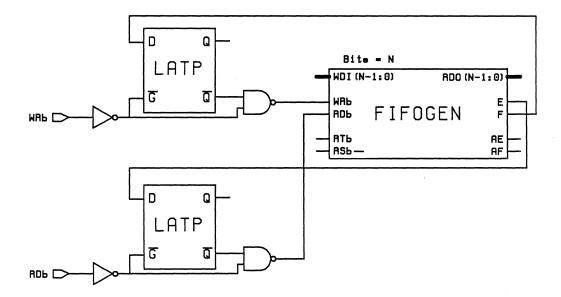

#### SYMBOL

The symbol for FIFOGEN will be unique for each configuration. An example is given here only for reference.

#### INPUT PARAMETER RANGES

| Input Parameter | Allowed<br>Range | Explanation                                        |

|-----------------|------------------|----------------------------------------------------|

| words           | 4 - 512          | Number of words in the $FIFO^1$ , $^2$             |

| bits            | 1 - 36           | Word size in <b>bits</b> <sup>1</sup>              |

| ae_offset       | 1 - words-1      | Almost Empty offset from Empty for flag activation |

| af_offset       | 1 - words-1      | Almost Full offset from Full for flag activation   |

<sup>&</sup>lt;sup>1</sup> Total number of bits (bits x words) must be  $\leq$  6K.

<sup>&</sup>lt;sup>2</sup> words is internally rounded up to a multiple of the column decode. The column decode is internally selected to be 1–8 (by 1) by FIFOGEN to optimize area and performance. Any changes in words will be reported to the user at configuration time.

# **INPUTS/OUTPUTS**

| Pin/Bus Name<br>(in TDL order) | Function                                                                                                    |     | Cap (pF) |

|--------------------------------|-------------------------------------------------------------------------------------------------------------|-----|----------|

| INPUTS:                        |                                                                                                             |     |          |

| WRb                            | Write control pin, active LOW                                                                               | Req | 0.10     |

| RDb                            | Read control pin, active LOW                                                                                | Req | 0.10     |

| RTb                            | Retransmit control pin, active LOW. Resets the read counter to first physical memory location               | Req | 0.10     |

| RSb                            | Reset control pin, active LOW. Resets the read and write counters to first physical memory location.        | Req | 0.15     |

| WDI[0:bits-1]                  | Write data input bus                                                                                        | Req | 0.08     |

| OUTPUTS:                       |                                                                                                             |     |          |

| RDO[0:bits-1]                  | Read data output bus                                                                                        | Req |          |

| E                              | Empty Flag, set HIGH on falling edge of RDb when reading last data word, reset on next rising edge of WRb   | Req |          |

| F                              | Full Flag, set HIGH on falling edge of WRb when writing last data word, reset on next rising edge of RDb    | Req |          |

| AE                             | Almost Empty Flag, set HIGH on falling edge of RDb when reading last data word, reset on rising edge of WRb | Req |          |

| AF                             | Almost Full Flag, set HIGH on falling edge of WRb when writing last data word, reset on rising edge of RDb  | Req |          |

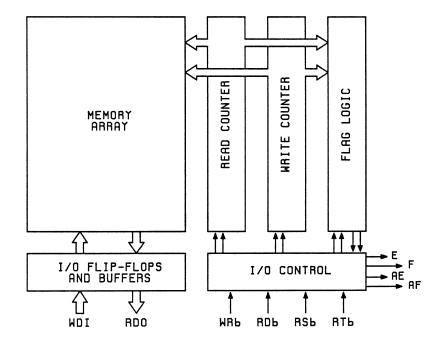

# **FUNCTIONAL BLOCK DIAGRAM**

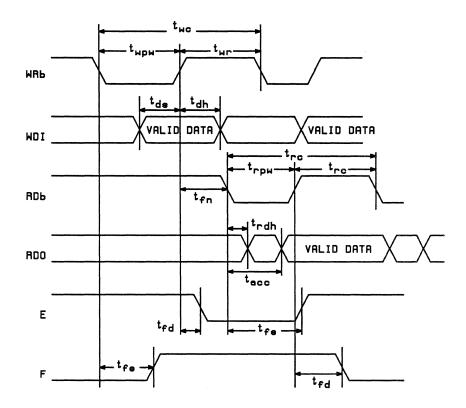

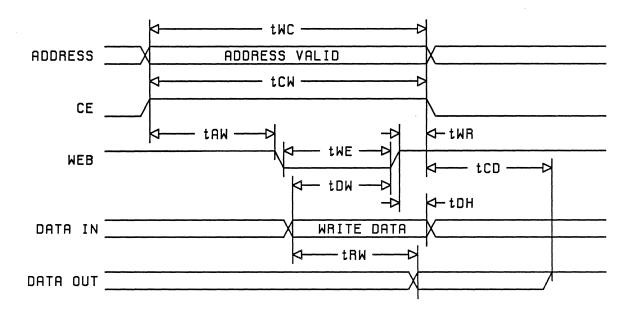

# AC WAVEFORMS - READ/WRITE

# TIMING PARAMETERS - READ/WRITE

| Name             | Description                                      |

|------------------|--------------------------------------------------|

| t <sub>w c</sub> | Minimum Write cycle time                         |

| twpw             | Minimum WRb pulse low                            |

| twr              | Minimum Write recovery time (WRb high)           |

| t <sub>d s</sub> | Minimum data setup time from rising edge of WRb  |

| t <sub>d h</sub> | Minimum data hold time after falling edge of WRb |

| trc              | Minimum Read cycle time                          |

| trpw             | Minimum RDb pulse low                            |

| trr              | Minimum Read recovery time (RDb high)            |

| tacc             | Maximum delay RDb falling to valid data          |

| trdh             | Minimum data hold time after falling edge of RDb |

| t <sub>fe</sub>  | Flag Enable Delay                                |

| tfd              | Flag Disable Delay                               |

| tfn              | First Write to first valid Read                  |

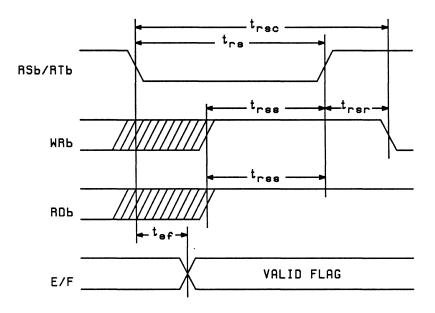

# AC WAVEFORMS - RESET/RETRANSMIT

# TIMING PARAMETERS - RESET/RETRANSMIT

| Name             | Description                                 |

|------------------|---------------------------------------------|

| trsc             | Minimum Reset/Retransmit cycle time         |

| trs              | Minimum Reset/Retransmit Pulse low          |

| trss             | Minimum WRb/RDb setup before RSb/RTb rising |

| trsr             | Minimum Reset/Retransmit recovery time      |

| t <sub>e f</sub> | Minimum Reset/Retransmit to flag output     |

# **FIFOGEN**

ViGen CONFIGURABLE FUNCTION

#### TIMING, POWER, AND AREA EQUATIONS

FIFOGEN will select its internal configuration based on the requested parameters. A simple algorithm is used which determines an internal architecture which will optimize area/performance tradeoffs. This architecture defines the number of rows and columns of the memory array. Because the user has no control over the internal column decode, the resulting configuration may have more words than requested (but never less). The algorithm is geared to minimize this discrepancy. The user will be notified at configuration time of the actual size of the array. Equations are given in terms of input parameters and internal architecture parameters. These can be found by following these steps:

- 1. CL is the output capacitance in pF.

- Generator input parameters which affect delays are words, bits. Derived parameters are ncols and nrows. ncols is the number of cell columns per I/O bit.

- Calculate first-pass values for derived parameters, for area and performance a square array is best. Use (i).

- 4. In order to assure reasonable wordline performance, check array width; if it is greater than optimum length (72), decrease column decode (**ncols**) by one. (ii).

- 5. Otherwise to optimize number of rows, check if increasing column decode would not cause too long a word line (iii).

- 6. Finally recalculate nrows if ncols changed (iv).

```

i. If (words ≤ 32) ncols = 1

else {

nrows = SQRT(words*bits), rounded up to an integer.

ncols = words/nrows, rounded up to an integer.

if (ncols > 8) ncols = 8

ii. if (ncols*bits > 72) ncols = ncols-1;

iii. else if (ncols*bits < (72 - bits) & ncols < 8) ncols = ncols +1;

}

iv. nrows = words/ncols, rounded up to an integer</li>

```

All times in nanoseconds and are nominal ( $V_{DD}$ =5.0 volts, T=25°C, Nominal process). See the *NCR ASIC Data Book* for process, voltage, and temperature derating factors.

| PARAM            | DESCRIPTION               | TYPICAL VALUE (ns)                                                       |

|------------------|---------------------------|--------------------------------------------------------------------------|

| t <sub>w c</sub> | Write Cycle               | - 16.26 + 0.212*nrows + 0.025*bits + 0.048*(ncols*bits)                  |

| twpw             | Write Pulse low           | = 7.10 + 0.036*(ncols-1) + 0.137nrows + 0.015*(ncols*bits)               |

| t <sub>w r</sub> | Write Pulse high          | = 5.20 + 0.010*nrows + 0.014*bits + 0.013*(ncols*bits)                   |

| t <sub>d s</sub> | Write Data Setup          | = 1.00                                                                   |

| t <sub>d h</sub> | Write Data Hold           | = 2.11 + 0.017*bits + 0.003*(ncols*bits)                                 |

| trc              | Read Cycle Time           | = 7.63 + 0.086*(ncols-1) + 0.084*nrows + 0.030*(ncols*bits)              |

| trpw             | Read Pulse low            | = 7.10 + 0.036*(ncols-1) + 0.137nrows + 0.015*(ncols*bits)               |

| trh              | Read Pulse high           | = $6.07 + 0.149*(ncols-1) + 0.044*(ncols*bits)$                          |

| t <sub>acc</sub> | Read Access               | = 3.99 + 0.018*(ncols-1) + 0.030*bits + 0.003*(ncols*bits) + 0.626*CL    |

| trdh             | Read Data Hold            | = 5.70 + 0.34*CL                                                         |

| t <sub>fe</sub>  | Flag Enable Delay         | = 4.37 + 0.626* <b>CL</b>                                                |

| $t_fd$           | Flag Disable Delay        | <b>-</b> 3.94 + 0.626* <b>CL</b>                                         |

| t <sub>f n</sub> | 1st Write to Read         | = $8.71 + 0.089*(ncols-1) + 0.055*nrows + 0.032*(ncols*bits)$            |

| trsc             | RSb/RTb Cycle Time        | = 9.56 + 0.118*(ncols-1) + 0.209*nrows + 0.012*bits + 0.009*(ncols*bits) |

| trs              | RSb/RTb Pulse low         | = 2.61 + 0.082*nrows + 0.005*(ncols*bits)                                |

| trss             | WRb/RD/b Setup to RSb/RTb | = 0.75 + 0.059*nrows + $0.007*$ (ncols*bits)                             |

| trsr             | RSb/RTb Recovery Time     | = 2.88 + 0.068*(ncols-1) + 0.038*nrows + 0.007*bits                      |

| t <sub>e f</sub> | RSb/RTb to Flag delay     | = 4.10 + 0.019*(ncols-1) + 0.076*nrows + 0.007*(ncols*bits) + 0.626*CL   |

#### **Output Rise and Fall Times**

$t_r = 0.632 + 2.26 CL$  $t_f = 1.07 + 1.39 CL$

Current Requirements: I = 0.148 + 0.004\*nrows + 0.02\*(bits) mA/MHz Worst case current process, VDD = 5.0V, T = 25°C

Cell Width (mils) = 30.33 + 1.18\*(ncols\*bits)

Cell Height (mils) = 23.06 + 1.45\*(nrows) + 0.46\*(cols-1)

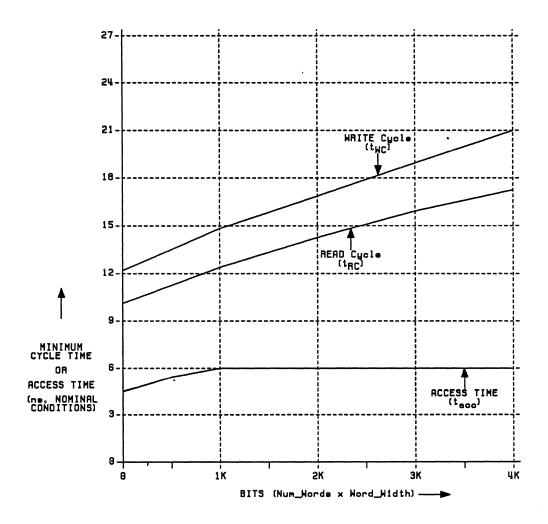

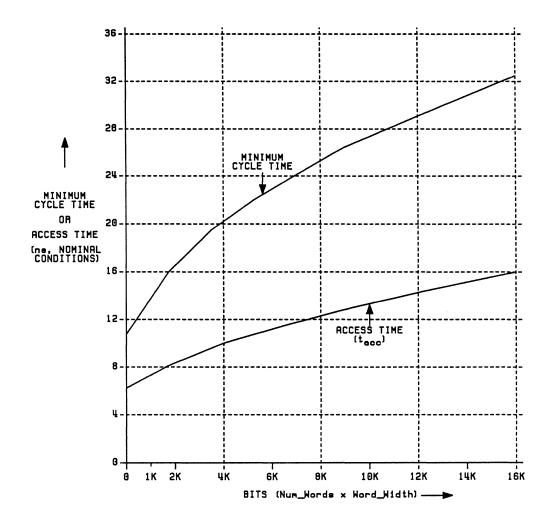

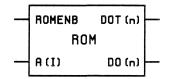

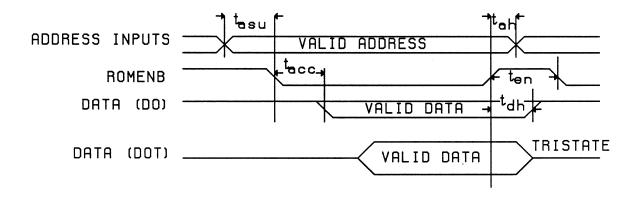

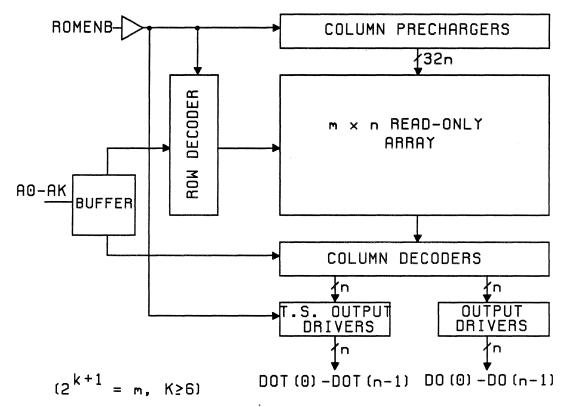

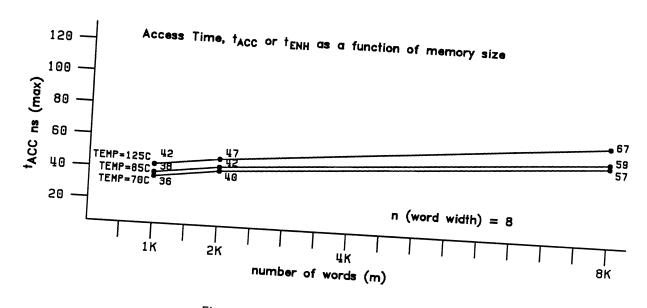

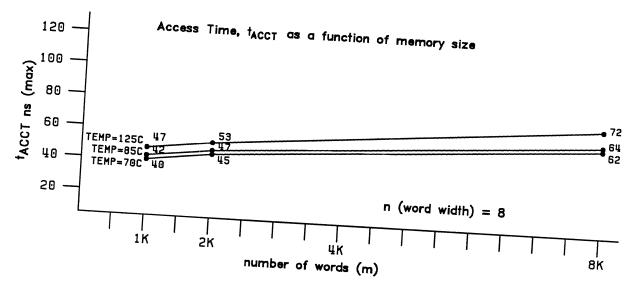

## **ACCESS AND CYCLE TIMES**

(See NCR VS1500 ASIC Data Book for process, voltage, and temperature derating factors.)

## TIMING EXAMPLES

## Timing for a 64x4 FIFO

| Symbol           | 64x4 FIFO                   |      | ninal<br>= 5V |      |      |      | case<br>= 4.5V |      |       |       |

|------------------|-----------------------------|------|---------------|------|------|------|----------------|------|-------|-------|

|                  |                             | TA = | 25°C          | TA = | 70°C | TA = | 85°C           | TA = | 125°C | Units |

|                  | Parameter                   | Min  | Max           | Min  | Max  | Min  | Max            | Min  | Max   | ]     |

| tacc             | Read access time            |      | 4.8           |      | 8.9  |      | 9.3            |      | 10.4  | ns    |

| <sup>t</sup> rdh | Read data hold              |      | 3.6           |      | 6.8  |      | 7.1            |      | 7.9   | ns    |

| t <sub>w c</sub> | Write cycle                 | 12.7 |               | 23.7 |      | 24.7 |                | 27.7 |       | ns    |

| trc              | Read cycle                  | 10.7 |               | 19.9 |      | 20.8 |                | 23.3 |       | ns    |

| tfn              | First write till first read | 11.5 |               | 21.4 |      | 22.3 |                | 25.1 |       | ns    |

| trsc             | Reset cycle time            | 8.2  |               | 15.3 |      | 15.9 |                | 17.9 |       | ns    |

| t <sub>d s</sub> | Write data setup time       | 0.7  |               | 1.2  |      | 1.2  |                | 1.4  |       | ns    |

| t <sub>d h</sub> | Write data hold             | 2.5  |               | 4.6  |      | 4.8  |                | 5.4  |       | ns    |

Switching characteristics (Input  $t_{\Gamma}$ ,  $t_{f} = 1.4$ ns, CL = 0.15pF)

Current Requirements:  $\mu A/MHz = 0.364$

Cell Width(mils) = 53.93Cell Height(mils) = 43.75Cell Area(mils $^2$ ) = 2360

## Timing for a 256x9 FIFO

| Symbol           | 256X9 FIFO                  |      | ninal<br>= 5V |      |      |      | Case<br>= 4.5V |      |       | Units |  |  |

|------------------|-----------------------------|------|---------------|------|------|------|----------------|------|-------|-------|--|--|

| Symbol           |                             | TA = | 25°C          | TA = | 70°C | TA = | 85°C           | TA = | 125°C | Units |  |  |

|                  | Parameter                   | Min  | Max           | Min  | Max  | Min  | Max            | Min  | Max   |       |  |  |

| tacc             | Read access time            |      | 5.2           |      | 9.6  |      | 10.0           |      | 11.2  | ns    |  |  |

| <sup>t</sup> rdh | Read data hold              |      | 3.7           |      | 6.5  |      | 7.1            |      | 8.0   | ns    |  |  |

| t <sub>w c</sub> | Write cycle                 | 17.2 |               | 32.0 |      | 33.4 |                | 37.5 |       | ns    |  |  |

| trc              | Read cycle                  | 14.5 |               | 25.9 |      | 28.1 |                | 31.6 |       | ns    |  |  |

| tfn              | First write till first read | 14.7 |               | 26.2 |      | 28.5 |                | 32.0 |       | ns    |  |  |

| trsc             | Reset cycle time            | 12.4 |               | 22.0 |      | 24.2 |                | 27.1 |       | ns    |  |  |

| t <sub>d s</sub> | Write data setup time       | 0.7  |               | 1.1  |      | 1.2  |                | 1.4  |       | ns    |  |  |

| <sup>t</sup> d h | Write data hold             | 2.7  |               | 4.9  |      | 5.2  |                | 6.0  |       | ns    |  |  |

Switching characteristics (Input  $t_r$ ,  $t_f = 1.4$ ns, CL = 0.15pF)

Current Requirements:  $\mu A/MHz = 0.476$

Cell Width (mils) = 104.67Cell Height (mils) = 79.47Cell Area (mils<sup>2</sup>) = 8320

## **APPLICATION NOTES**

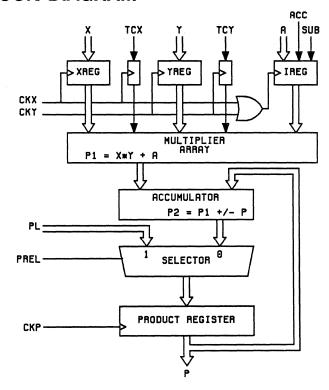

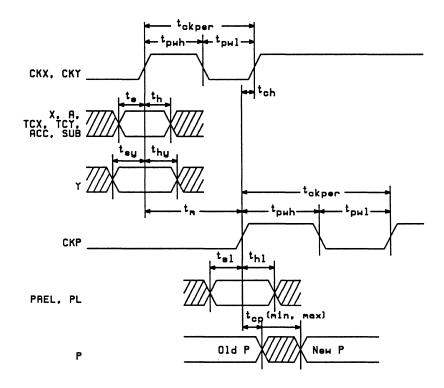

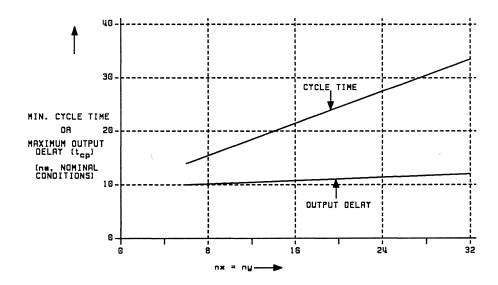

On power up a Reset must be performed before any other operations are performed. This assures that the FIFO is starting from a known state.