# Parallel Port Interface Chip - Peripheral Side

#### **FEATURES**

- ! Creates PC/AT-Style Bus from Parallel Printer Port Signals

- Single Chip Interface to Any Bus Capable Peripheral

- ! Supports Standard, Bi-Directional, EPP, and ECP Parallel Ports

- ! Burst Mode for Improved Data Transfer Rates

- ! Adaptive Interface Optimizes Transfer Rates to Parallel Port Characteristics

- ! Digital Signal Filtering Increases Noise Immunity

- ! Allows Daisy-Chain of up to Eight Peripherals Including Standard Printer

- ! Provides Interrupt Sharing with Daisy-Chained Devices

- ! 16-Bit Product ID Support

- Peripheral Bus Clock Selectable at System Clock /2, /3, /5, or /6

- ! Interfaces to 8-Bit and/or 16-Bit Peripherals

- ! FIFO Operation Permits Overlapping Parallel Port and Peripheral Bus Cycles for Maximum Data Transfer Rate

- ! Flexible DRAM Buffer Support and DMA Capability

- ! Four Output Lines Individually Configurable as Chip Selects or General Purpose Outputs

- ! Three Output Lines Individually Configurable as Strobes or General Purpose Outputs

- ! Four Uncommitted Inputs

- ! Watchdog Monitors Host Computer Activity

- Low Battery Detect Input

- ! Direct Output for Piezo Transducer

- ! Support for Automatic Power Up/Down

- ! Prevents Host System Latchup with Powerback Control

- ! On Chip Crystal Oscillator

#### **GENERAL DESCRIPTION**

The PPC34C60 provides a means of re-generating an IBM® AT® style (ISA) bus from the PC printer port signals. In addition to Standard (Compatible) printer ports, the PPC34C60 supports PS/2® (bi-directional), EPP, and ECP ports. Up to eight peripherals may be daisy chained between the computer and the printer. Printer operation is unaffected.

The PPC34C60 performs as an intelligent data mux. It multiplexes the printer port signals between the daisy chain (pass-through) outputs and there-generated ISA bus. Furthermore, it handles

breaking up 8- and 16-bit ISA data into 4- or 8-bit chunks for the parallel port.

The PPC34C60 also provides a piezo transducer driver for battery-powered systems. The transducer will signal low battery with two repeated beeps. If the cable to the computer is disconnected, or if the host is dormant for about a minute, the transducer will signal inactivity with four beeps. Additionally, a power-down signal can be provided to external circuitry to automatically shut down system power during inactivity.

## **TABLE OF CONTENTS**

| FEATURES                     | . 1 |

|------------------------------|-----|

| GENERAL DESCRIPTION          | . 1 |

| PIN CONFIGURATION            | . 3 |

| DESCRIPTION OF PIN FUNCTIONS | . 3 |

| FUNCTIONAL DESCRIPTION       | 13  |

| PPC34C60 BLOCK DESCRIPTION   |     |

| DAISY CHAIN COMMAND PROTOCOL | 14  |

| PERIPHERAL SYSTEM DESIGN     | 15  |

| DEVICE ADDRESSING            | 17  |

| NTERNAL REGISTER MAP         | 19  |

| REGISTER DESCRIPTIONS        | 20  |

| DRAM BUFFER OPERATION        | 33  |

| DRAM PHYSICAL ADDRESSING     |     |

| SYSTEM DATA BUS CYCLES       | 35  |

| POWERING THE PPC34C60        |     |

| OPERATIONAL DESCRIPTION      | 40  |

|                              | 40  |

80 Arkay Drive Hauppauge, NY 11788 (516) 435-6000 FAX (516) 273-3123

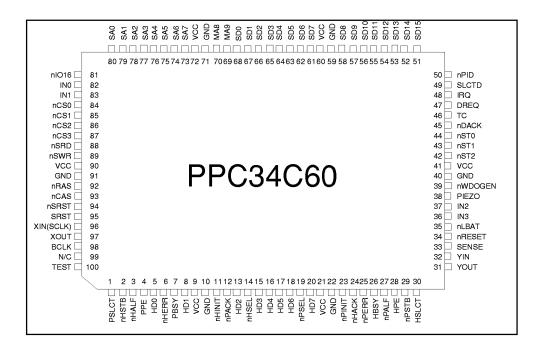

#### PIN CONFIGURATION

|         |                         |              | BUFFER   |                                                                                                                                                                                                                                          |

|---------|-------------------------|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NO. | NAME                    | SYMBOL       | TYPE     | DESCRIPTION                                                                                                                                                                                                                              |

|         | PARALLEL PORT           | HOST CONTROL | AND COMM | ION DATA BUS INTERFACE                                                                                                                                                                                                                   |

| 2       | nHost:Strobe            | nHSTB        | I,PU     | An active low pulse on this input is used to strobe printer data into the printer. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes.                                                       |

| 3       | nHost:Auto Line<br>Feed | nHALF        | I,PU     | This input goes low to cause the printer to automatically feed one line after each line is printed. Connects to AUTOFD output from Host. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes. |

| PIN NO. | NAME                  | SYMBOL | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                |  |  |

|---------|-----------------------|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 14      | nHost:SelectIn        | nHSEL  | I              | This active low input is driven by the host to select the printer. Connects to SELECT IN output from Host. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes. (See Note 1 on Page 11.)                                        |  |  |

| 11      | nHost:Initiate        | nHINIT | l              | This active low input initiates the printer when low. Connects to INIT output from Host. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes. (See Note 1 on Page 11.)                                                          |  |  |

| 24      | nHost:<br>Acknowledge | nHACK  | O16            | This active low output from the printer is used to indicate that the printer has received the data and is ready to accept new data. Connects to the ACK input to the Host. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes. |  |  |

| 26      | Host:Busy             | HBSY   | O16            | This status output, generated by the printer, goes high to indicate that it is not ready to receive new data from the host. Connects to the BUSY input to the Host. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes.        |  |  |

| 28      | Host:Paper End        | HPE    | O16            | This status output, generated by the printer, goes high to indicate that the printer is out of paper. Connects to the PERROR input to the Host. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes.                            |  |  |

|                      | DESCRIPTION OF FIRT ORCHORS      |               |                |                                                                                                                                                                                                                                                                       |  |  |  |

|----------------------|----------------------------------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                      |                                  |               | BUFFER<br>TYPE |                                                                                                                                                                                                                                                                       |  |  |  |

| PIN NO.              | NAME                             | SYMBOL        |                | DESCRIPTION                                                                                                                                                                                                                                                           |  |  |  |

| 30                   | Host:Printer<br>Selected         | HSLCT         | O16            | This status output, generated by the printer, goes high to indicate that the printer is selected. Connects to the SELECT input to the Host. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes.                           |  |  |  |

| 6                    | nHost:Printer Error              | nHERR         | O16            | This status output, generated by the printer, goes low to indicate an error condition at the printer. Connects to the ERROR input to the Host. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes.                        |  |  |  |

| 5,8,13,15<br>-18, 20 | Host:Data[0:7]                   | HD[0:7]       | I/O16,<br>PU   | Parallel port bi-directional data bus connected to host system is used by SPP, ECP and EPP to transfer data between the host CPU and peripherals. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes.                     |  |  |  |

|                      | PARAL                            | LEL PORT PASS | THROUGHI       | NTERFACE PINS                                                                                                                                                                                                                                                         |  |  |  |

| 29                   | nPass-Through:<br>Strobe         | nPSTB         | O16            | An active low pulse on this output is used to strobe printer data into the printer. Connects to the STROBE input on the next device along the chain. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes.                  |  |  |  |

| 27                   | nPass-Through:<br>Auto Line Feed | nPALF         | O16            | This output goes low to cause the printer to automatically feed one line after each line is printed. Connects to the AUTOFD input on the next device along the chain. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes. |  |  |  |

|         | 1                             | 1      | I              |                                                                                                                                                                                                                                                                                                     |

|---------|-------------------------------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NO. | NAME                          | SYMBOL | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                         |

| 19      | nPass-Through:<br>SelectIn    | nPSEL  | O16            | This active low output selects the printer. Connects to the SELECT IN input on the next device along the chain. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes.                                                                                     |

| 23      | nPass-Through:<br>Initiate    | nPINIT | O16            | This active low output initiates the printer when low. Connects to the INIT input on the next device along the chain. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes.                                                                               |

| 12      | nPass-Through:<br>Acknowledge | nPACK  | I, PU          | This active low input from the printer is used to indicate that the printer has received the data and is ready to accept new data. Connects to the ACK output from the next device along the chain. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes. |

| 7       | Pass-Through:<br>Busy         | PBSY   | I, PU          | This status input, generated by the printer goes high to indicate that it is not ready to receive new data from the Pass-Through. Connects to the BUSY output from the next device along the chain. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP/EPP modes.     |

| 4       | Pass-Through:<br>Paper End    | PPE    | I, PU          | This status input, generated by the printer, goes high to indicate that the printer is out of paper. Connects to the PERROR output from the next device along the chain. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes.                            |

|                 | Ι                                 | DESCRIPTION     | · · · · · · · · · · · · · · · · · · · | T                                                                                                                                                                                                                                                                        |

|-----------------|-----------------------------------|-----------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NO.         | NAME                              | SYMBOL          | BUFFER<br>TYPE                        | DESCRIPTION                                                                                                                                                                                                                                                              |

| 1               | Pass-Through:<br>Printer Selected | PSLCT           | I, PU                                 | This status input, generated by the printer, goes high to indicate that the printer is selected. Connects to the SELECT output from the next device along the chain. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP/EPP modes.         |

| 25              | nPass-Through:<br>Printer Error   | nPERR           | I, PU                                 | This status output, generated by the printer, goes low to indicate an error condition at the printer. Connects to the ERROR output from the next device along the chain. Refer to Section 4 of the IEEE STD 1284 (Reference 1) for use of this pin in ECP and EPP modes. |

| ĺ               | SYSTEM                            | (REGENERATED    | ISA PERIPH                            | IERAL) INTERFACE                                                                                                                                                                                                                                                         |

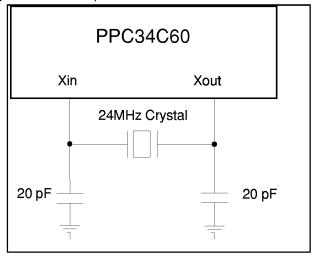

| 96<br>97        | System<br>Clock/Crystal           | XIN (SCLK) XOUT | l<br>О8                               | XIN may be connected to a ttl peripheral system clock or a crystal may be placed across XIN/XOUT (typically 24MHz). This is used to derive the internal clock (BUSCLK) used for all system interface timing.                                                             |

| 80-73           | System Address<br>[0:7]           | SA[0:7]         | O8                                    | These lower eight address bits are presented to the system bus directly by the PPC34C60 during bus and DRAM access. Upper address bits, if needed, should be latched through use of the PPC34C60's strobe lines prior to generating bus accesses.                        |

| 70,69           | Memory Address [8,9]              | MA[8:9]         | 08                                    | These address bits are appended to SA[0:7] to create a 10-bit row or column address for DRAM access.                                                                                                                                                                     |

| 68-61,<br>58-51 | System Data [0:15]                | SD[0:15]        | I/O8,<br>PU                           | These bi-directional pins are used to transfer data during bus or DRAM cycles to or from the system.                                                                                                                                                                     |

| 88              | nSystem Read                      | nSRD            | O8                                    | This indicates that a bus read cycle is occurring, similar to an ISA MEMR signal.                                                                                                                                                                                        |

| DESCRIPTION OF FIRST GROTTONS |                           |        |                |                                                                                                                                                                                                                     |  |  |

|-------------------------------|---------------------------|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN NO.                       | NAME                      | SYMBOL | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                         |  |  |

| 89                            | nSystem Write             | nSWR   | O8             | This indicates that a bus write cycle is occurring, similar to an ISA MEMW signal.                                                                                                                                  |  |  |

| 81                            | n16-Bit I/O               | nIO16  | I, PU          | This signal is asserted by the remote system to indicate whether or not the address being accessed is capable of a 16-bit transfer.                                                                                 |  |  |

| 48                            | Interrupt Request         | IRQ    | I, PU          | This rising edge activated signal indicates an interrupt request from the System.                                                                                                                                   |  |  |

| 94                            | nSystem Reset             | nSRST  | O8             | This low going signal can be used to reset the System. This signal is asserted for 16 SCLKs.                                                                                                                        |  |  |

| 95                            | System Reset              | SRST   | O8             | This high going signal can be used to reset the System. This signal is asserted for 16 SCLKs.                                                                                                                       |  |  |

| 92                            | nRow Address<br>Strobe    | nRAS   | O8             | This low going strobe signal is used by the DRAM to latch the row address, present on the SA[0:7] and MA[8:9] pins. This output drives the DRAM directly, however a series resistor is recommended on this line.    |  |  |

| 93                            | nColumn Address<br>Strobe | nCAS   | O8             | This low going strobe signal is used by the DRAM to latch the column address, present on the SA[0:7] and MA[8:9] pins. This output drives the DRAM directly, however a series resistor is recommended on this line. |  |  |

| 45                            | nDMA<br>Acknowledge       | nDACK  | O8             | This active low output signal is issued to inform the System that data is to be transferred using DMA transfer cycles.                                                                                              |  |  |

| 46                            | Terminal Count            | TC     | 08             | This active high output is asserted with the last DMA data transfer to indicate to the System that the DMA data transfer is complete. TC is asserted in conjunction with DACK.                                      |  |  |

|                 |                                     |                | BUFFER   |                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-------------------------------------|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NO.         | NAME                                | SYMBOL         | TYPE     | DESCRIPTION                                                                                                                                                                                                                                                                                                                       |

| 47              | DMA Request                         | DREQ           | I, PD    | The remote system indicates that it is ready to perform DMA transfers by driving this line high. This signal is asserted as long as the System is ready to receive or send data and is deasserted on the last byte of the data transfer.                                                                                          |

|                 |                                     | MISCE          | LLANEOUS |                                                                                                                                                                                                                                                                                                                                   |

| 39              | nWatchdog Enable                    | nWDOGEN        | I, PU    | Pulling this line low enables the watchdog. The watchdog will generate four beeps on the piezo driver if there are no transitions on the host port lines for a minute. This circuitry can also automatically power down the system when the watchdog "barks". This feature requires software to tickle the port every 30 seconds. |

| 34              | nReset Chip                         | nRESET         | I, PU    | Pulling this line low for two SYSCLKs will reset the PPC34C60 to its initial state. This will reset all internal registers to their default values.                                                                                                                                                                               |

| 35              | nLow Battery<br>Indicator           | nLB <b>A</b> T | I, PU    | A low level on this input line signals that the battery power is low and the PPC34C60 will generate low battery tones. It is the responsibility of the remote system to monitor battery power and generate this input signal.                                                                                                     |

| 82,83,<br>37,36 | General Purpose<br>Inputs [0:3]     | IN[0:3]        | I, PU    | The host may obtain the level at these pins by reading the Internal Input Register.                                                                                                                                                                                                                                               |

| 38              | Piezo Crystal Drive PIEZO           |                | O24      | This high current output can be directly hooked up to a piezo speaker to provide audio tones.                                                                                                                                                                                                                                     |

| 44,43, 42       | nStrobes[0:2]<br>(special function) | nST[0:2]       | O8       | These pins are individually configured as general purpose outputs or as strobe outputs as programmed in the Output Configuration Register. ST2 may also be programmed as the Auto-Power pin.                                                                                                                                      |

|          | DESCRIPTION OF THAT CHOTCHS              |          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|----------|------------------------------------------|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN NO.  | NAME                                     | SYMBOL   | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 84-87    | nChip Selects[0:3]<br>(special function) | nCS[0:3] | O8             | These pins are individually configured as general purpose outputs or as chip select outputs as programmed in the Output Configuration Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

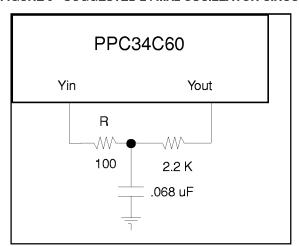

| 32<br>31 | Oscillator Input Oscillator Output       | YOUT     | l<br>08        | A parallel resonant crystal or RC network may be placed across YIN and YOUT. This nominal 32KHz clock (32.768KHz) is used by the internal piezo driver and watchdog timer.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 49       | Selected Device                          | SLCTD    | O8             | This signal is an active high output that indicates that the device is the active device on the daisy chain. This may be used for debug purposes, to enable drivers, or to qualify signals.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 50       | nProduct ID                              | PID      | 08             | This signal is an active low output asserted when the host performs a request for the peripheral's Product ID. This function is used by the daisy chain and multiplexor protocols.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

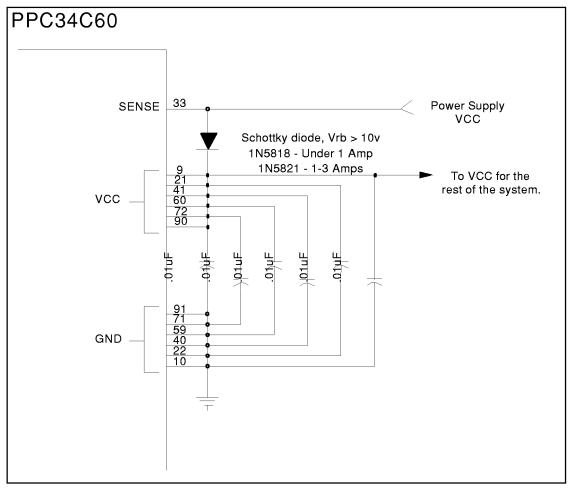

| 33       | Sense VCC                                | SENSE    | I, PD          | When pulled high, this input will enable all output drivers of the PPC34C60. When low, all outputs are tri-stated. This resolves the back-power problem inherent in parallel port peripherals. Isolate the chip's VCC from the rest of the peripheral's VCC using a schottky diode. The SENSE input should be tied to the peripheral's VCC and the anode of the diode. In this manner, when the peripheral's power is off, the sense input will shut down all outputs, preventing the chip from driving into a low impedance load and consequently damaging the chip's input protection diodes. |  |  |  |

| PIN NO.                   | NAME          | SYMBOL   | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                       |

|---------------------------|---------------|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 100                       | Test Counters | TEST     | I, PD          | This is an active high signal that allows access to some large counter chains that are normally buried within the chip. For normal operation this input should be left unconnected, or tied to ground. For more information on the test mode contact the factory. |

| 98                        | BUSCLK        | BCLK     | O8             | BUSCLK is the SCLK divided by the value programmed in the Configuration Register.                                                                                                                                                                                 |

| 99                        | Reserved      | RESERVED |                | Leave floating, no connection                                                                                                                                                                                                                                     |

| 9,21,<br>41,60,<br>72,90  | Power         | VCC      |                | +5 Volt supply pins.                                                                                                                                                                                                                                              |

| 10,22,<br>40,59,<br>71,91 | Ground        | GND      |                | Ground pins                                                                                                                                                                                                                                                       |

Note 1: By pulling both these lines low (illegal state), the PPC34C60's output ports can be disabled.

## **BUFFER TYPE DESCRIPTIONS**

| <b>BUFFER TYPE</b> | DESCRIPTION                        |

|--------------------|------------------------------------|

| 1                  | Input, Schmitt Trigger             |

| I/O8               | Input, Schmitt Trigger/8mA Output  |

| I/O16              | Input, Schmitt Trigger/16mA Output |

| 08                 | 8mA Output                         |

| O16                | 16mA Output                        |

| O24                | 24mA Output                        |

| PU                 | Pull Up, nominal 100K              |

| PD                 | Pull Down, nominal 100K            |

## **GENERAL CONVENTIONS**

Throughout this document, the following various terms and conventions will be used:

Compatible = "Centronics"

SPP = "Standard Bi-Directional Parallel Port" (PS/2)

EPP = "Enhanced Parallel Port"

ECP = "Extended Capabilities Port"

## REFERENCE DOCUMENTS

- 1. IEEE STD 1284, February 2, 1993.

- 2. The Enhanced Parallel Port, an Introduction; FarPoint Communications.

- 3. Daisy Chain Specification, Rev. 1.1, September 16, 1993; Disctec Corporation.

- 4. Enhanced Parallel Port BIOS Specification, Rev 3, February 12, 1993; FarPoint Communications.

- 5. ECP: Specification Kit, Rev 1.03, February 10, 1993; Microsoft Corporation.

#### **FUNCTIONAL DESCRIPTION**

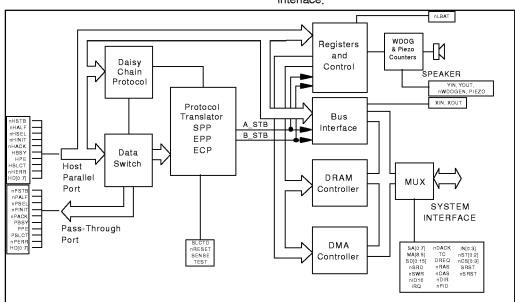

#### PPC34C60 BLOCK DESCRIPTION

The PPC34C60 can be broken down into eight functional blocks as shown in Figure 1.

The PPC34C60 implements and complies with the Daisy Chain Specification (Reference 3) through the Daisy Chain Protocol block. Under the Daisy Chain protocol, the PPC34C60 operates in either Pass-Through or Selected mode. Pass-Through mode is the power up default, and is electrically transparent to devices further down the chain. When in Pass-Through mode, the Data Switch gates the control and status lines of the parallel port to the Pass-Through port. Selected mode connects the System Interface bus to the parallel port. When in Selected mode, the Data Switch gates the control and status lines to the PPC34C60's Protocol Translator functional block.

The Protocol Translator block gives the PPC34C60 its capability to communicate with the parallel port in either SPP, EPP, or ECP mode. The Protocol Translator interprets the Multiport Access Protocol (MAP) packets described in the Daisy Chain Specification (Reference 3). The MAP packets and command codes are described in the Daisy Chain Command Protocol. The Protocol Translator also decodes the type of parallel port transfer (ie. Address Write/Data Read\_Write Cycle) and provides the proper control of the data to the Registers and Control block and to the Bus Interface block. The PPC34C60's internal registers, contained in the Register and Control block, control the operation of the chip's internal DRAM Controller, DMA Controller, and Watchdog Controller. The Bus Interface block controls data transfers between the Parallel Port and the peripheral's System Interface Bus. The MUX block routes data and control signals to the System Interface

FIGURE 1 - INTERNAL BLOCK DIAGRAM

## DAISY CHAIN COMMAND PROTOCOL

The daisy chain protocol is used to select the mode of each device and to allow connection of up to eight devices on one parallel port. The daisy chain commands use the Multiport Access

Protocol (MAP) to access the devices. The format of the MAP packets is as follows:

The command byte in the MAP packet represents a code and possibly an address as well. The currently defined codes are:

| (00- | 07) | 0000 0aaa | Assign address aaa to the current device   |

|------|-----|-----------|--------------------------------------------|

| -80) | 0F) | 0000 1aaa | Query Interrupt from device aaa            |

| (10- | 17) | 0001 0aaa | Query Product ID from device aaa           |

| (20- | 27) | 0010 0aaa | Select device aaa in EPP mode              |

| (30) |     | 0011 xxxx | De-select all devices                      |

| (40) |     | 0100 0xxx | Disable Daisy Chain Interrupts             |

| (48) |     | 0100 1xxx | Enable Daisy Chain Interrupts              |

| (50- | 57) | 0101 0aaa | Clear Interrupt Latches on device aaa      |

| (58- | 5F) | 0101 1aaa | Set Interrupt Latch on device aaa          |

| (D0- | D7) | 1101 Oaaa | Select device aaa in ECP mode              |

| (E0- | E7) | 1110 Oaaa | Select device aaa in Compatible Mode - SPP |

|      |     |           |                                            |

aaa = Device Address

xxx = Undefined - set to zero

Refer to the Daisy Chain Specification (Reference 3) for more information.

## PERIPHERAL SYSTEM DESIGN

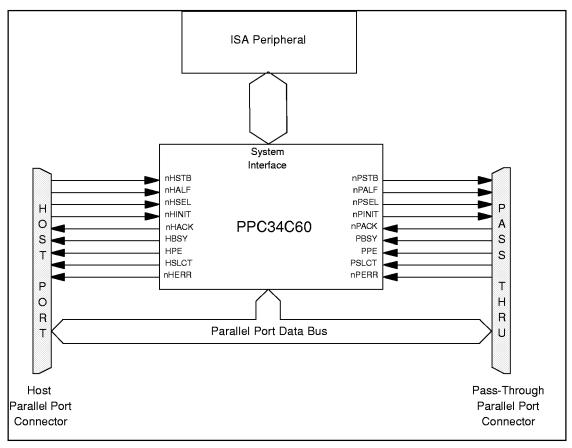

The PPC34C60 simplifies the design of a peripheral to exploit the benefits of IEEE STD 1284, Standard Signaling for a Bi-Directional Parallel Port (Reference 1). Figure 2 depicts a high-level System Block Diagram which shows the peripheral chip's three primary data paths.

Note that the Parallel Port Data Bus is not switched through the PPC34C60; this allows all daisy chained devices to receive a special "out of band" Control Packet as defined in the Distec Daisy Chain Specification (Reference 3).

FIGURE 2 - SYTEM BLOCK DIAGRAM

#### **DESIGN EXAMPLE**

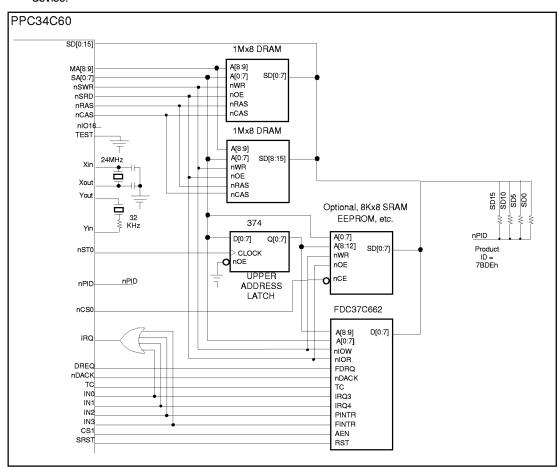

Figure 3 shows a simple system design that uses most of the PPC34C60's interface functions. This example shows:

- 1) A DRAM interface.

- 2) An 8Kx8 NV-memory device interface using nStrobe Output 0 to latch the upper address bits and nChip Select Output 0 to enable the device.

- An interface to SMSC's FDC37C662 Super I/O Floppy Disk Controller. This section of the design illustrates how the PPC34C60 can handle a direct memory access interface, four interrupts, and an additional chip select output configured as a standard output pin. The SRST (reset output) is used to reset the floppy disk controller.

- 4) The use of 10K bias resistors to implement a product ID code.

FIGURE 3 - TYPICAL SYSTEM INTERFACE

#### **DEVICE ADDRESSING**

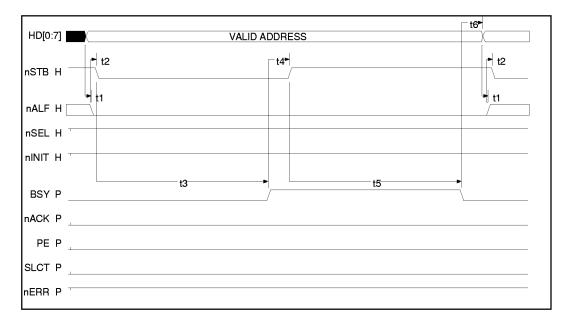

The Bi-Directional Parallel Peripheral Interface protocol, defined by the IEEE STD 1284 (Reference 1), describes two basic types of 8-bit information transfers: data read/write operations and address read/write operations. The PPC34C60's bus and internal registers are accessed via data read/write operations.

The PPC34C60's address mode is set through an SPP, EPP, or ECP address write operation. Table 1 specifies the control signals used by each protocol to perform Address and Data Cycles and to indicate reverse data flow. Refer to the IEEE STD 1284 (Reference 1) for further information.

Table 1 - Key Address/Data Cycle Signals

| SIGNAL          | SPP         | EPP      | ECP        |  |

|-----------------|-------------|----------|------------|--|

| Address         | Address SEL |          | STB(ALF=0) |  |

| Strobe          |             |          |            |  |

| Data            | STB         | ALF      | STB(ALF=1) |  |

| Strobe          |             |          |            |  |

| Reverse Channel | INIT=0      | IMPLICIT | INIT = 0   |  |

| Signal          |             |          |            |  |

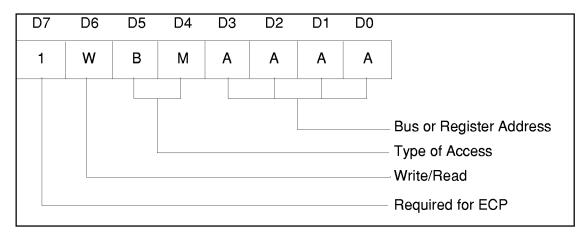

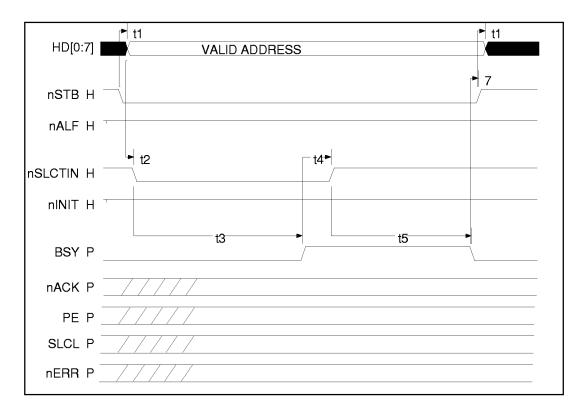

The Parallel Port provides a byte-wide parallel data path. Figure 4 defines the data bits of

this parallel port data path during an address write operation to the PPC34C60.

FIGURE 4 - PARALLEL PORT ADDRESS WRITE AND DATA BITS

An address write cycle is used to select the PPC34C60's address mode for subsequent data write cycles. Table 2 shows ten types of Address Modes into which the PPC34C60 may be placed. The address write data byte required for each mode is encoded as '1WBMA3A2A1A0'.

Table 2 also illustrates three separate System Data Bus addressing modes along with DRAM and Internal Registers addressing.

When the Host Address Write data is 1X100XXX, the PPC34C60 provides unrestricted System Data Bus access for all subsequent Host Parallel Port data exchanges.

Unrestricted System Data Bus access can also occur following Address Write operations where 1WBMA3A2A1A0 = 1X00(A3-A0), except that in this short hand addressing mode A3-A0 is also written to the least significant four bits of the PPC34C60 internal Address Register. Address Write operations where 1WBMA3A2A1A0 = 1X01(A3-A0) provides block count limited System Data Bus access with shorthand addressing.

For example, an Address Write operation in which  $B=1,\ M=0,\ and\ A3A2A1A0=0000$  selects System Data Bus access but does not alter the value of the PPC34C60 Address Bus, SA[0:7].

**Table 2 - Address Mode Operations**

| 1WBM | A3A2A1A0                  | Access Type | W=1(Write)              | W=0(Read)              |

|------|---------------------------|-------------|-------------------------|------------------------|

| 1X00 | (A3-A0)                   |             | Unrestricted Bus Write  | Unrestricted Bus Read  |

|      |                           |             | (Shorthand Mode)        | (Shorthand Mode)       |

|      |                           |             |                         |                        |

|      |                           | SYSTEM DATA |                         |                        |

|      |                           | BUS         |                         |                        |

| 1X01 | ( <b>A</b> 3- <b>A</b> 0) |             | Block Restricted Bus    | Block Restricted Bus   |

|      |                           |             | Write (Shorthand Mode)  | Read (Shorthand Mode)  |

| 1X10 | 0XXX (BUS)                |             | Unrestricted Bus Write  | Unrestricted Bus Read  |

|      |                           |             | Access                  | Access                 |

| 1X10 | 1XXX                      | DRAM        | DRAM Write Access       | DRAM Read Access       |

|      | (DRAM)                    |             |                         |                        |

| 1X11 | RRRR                      | INTERNAL    | Write Internal Register | Read Internal Register |

|      |                           | REGISTERS   | RRRR                    | RRRR                   |

W = Write B = Bus M = Max Count A3A2A1A0 = Address Selector RRRR = Register Selector

## **INTERNAL REGISTER MAP**

The internal registers of the PPC34C60 are selected by performing an Address Write Cycle with bits B and M (bits 5 and 4) set to 1,1 (see Table 2). The desired register is selected by the binary value of A3A2A1A0 (bits-3:0), also shown as RRRR. Internal register RRRR is made available for Read or Write based on the bit value of W (bit 6) as shown below. All internal registers are eight bits wide.

Table 3 - Internal Register Map

| W* | ВМ | RRRR | REGISTER DESCRIPTION           | DEFAULTS |  |

|----|----|------|--------------------------------|----------|--|

| Х  | 11 | 0000 | Address Register               | 00       |  |

| Х  | 11 | 0001 | Output Configuration Reg       | 10       |  |

| Х  | 11 | 0010 | Output Register                | 80       |  |

| 1  | 11 | 0011 | Sound Register                 | NA       |  |

| 0  | 11 | 0011 | Input Register                 | SF       |  |

| Х  | 11 | 0100 | Operation Register             | 00       |  |

| Х  | 11 | 0101 | DRAM Buffer Size Register      | 0C       |  |

| Х  | 11 | 0110 | Host DRAM Buffer Pointer       | 00       |  |

| Х  | 11 | 0111 | DMA DRAM Buffer Pointer        | 00       |  |

| Х  | 11 | 1000 | Host Max Block Count - Low     | 00       |  |

| Х  | 11 | 1001 | Host Max Block Count - High    | 10       |  |

| Х  | 11 | 1010 | DMA Byte Count - Low           | 00       |  |

| Х  | 11 | 1011 | DMA Byte Count - High          | 00       |  |

| Х  | 11 | 1100 | Configuration Register         | 04       |  |

| 0  | 11 | 1101 | Chip Revision Level 00         |          |  |

| 1  | 11 | 1110 | Port Test Register NA          |          |  |

| 0  | 11 | 1110 | Port Test Register             | 00       |  |

| Χ  | 11 | 1111 | Data Transfer Control Register | 01       |  |

$\frac{*W}{X} = \text{Read/Write}$

1 = Write

0 = Read

#### **REGISTER DESCRIPTIONS**

#### ADDRESS REGISTER - 0000 (Read/Write)

The value in the Address Register represents the current address presented to the Bus Address lines SA[0:7]. The primary method of updating this value is the following sequence. First the Address Register is selected to be written to by performing an Address Write operation (XWBMA3A2A1A0=x1110000). Next a Data Write operation is issued to write A<0:7> as a group equal to the value presented on the parallel port host data lines HD[0:7].

A shorthand mode is also provided to allow the Address to be modified and Bus Operation to be selected in one Address Write operation. If B = 0, then bus operation is selected and A3A2A1A0 is written to A<0-3>; A<4-7> are unaffected. In this mode, if M = 1, then the bus access will be limited by the Host Max Block Count Register. Any attempts to read more data will return invalid data. The PPC34C60 contains an integrated FIFO to enhance performance by reading the Bus one or two bytes ahead of the Host Port. As an example, some devices such as IDE hard drives expect data

to be read in a fixed block length (sector). Set MAXCNT (Configuration Register bit 6) and set the value of Host Max Block Count Register to the length of the IDE data block to read only the desired amount of data (1 sector) from the peripheral.

If M = 0, then the current setting of MAXCNT and Host Max Block Count are ignored. This allows polling of a status register without limiting the number of times the register may be accessed.

The PPC34C60 directly provides eight address lines. If more than eight bits of address are necessary, three strobe lines are available which may be used with external circuitry to latch higher-order address bits off of SA[0:7]. For example, the address register can be written with higher order address bits and latched with one or more of the three programmable strobe lines. The address register is then written with A0-A7, and normal bus reads/writes follow. This scheme may be extended to any size address bus needed.

An auto-increment option may be activated by setting AUTOINC (bit 4 in the Operation Register, RRRR=0100) which will increment A<0:7> after each bus access.

#### OUTPUT CONFIGURATION REGISTER - 0001 (Read/Write)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SP1   | SP0   | SO1   | SO0   | CO3   | CO2   | CO1   | COO   |

The Output Configuration Register defines the operation of the bits in the Output Register.

The PPC34C60 has eight independent output lines. The functionality of seven of these output lines is selected through the Output Configuration Register. All eight output lines are then controlled or activated through the Output Register (RRRR=0010).

The seven programmable output lines controlled by Output Register bits 0-6 can be selected to

operate as either general purpose output pins (inverting), or as special function output pins. The special functions are: Chip Select, Strobe, and Auto-Power.

The eighth (non-programmable) output line is controlled by Output Register bit 7. This output line is defined as "Bus Reset", but it is simply an output bit. It may be used for other purposes if a Bus Reset signal is not required or generated elsewhere. This bit is present on two pins (95 and 94) in both normal and inverted polarities.

## Bits 0-3: SPECIAL FUNCTIONS FOR PROGRAMMABLE OUTPUT LINES 0-3:

Programmable output lines 0-3 can be individually configured as General Purpose (inverting) outputs or as chip select outputs. Chip selects are generated by the bus cycle state machine.

During a bus cycle, the chip select goes low at the start of the cycle and remains low until the end of the cycle.

Output line N (N=0...3) is controlled through Output Register Bit N. Output line N, configured as a General Purpose output, will present the inverted value written to Output Register bit N. Output line N, configured as a Chip Select, will follow the bus chip select if Output Register bit N is a 1.

| Bit 0:CO0 - Chip Select 0/Standard Output 0 |                                                                      |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------|--|--|--|

| 0                                           | Select Output line 0 (Pin 84) as a General Purpose inverting output. |  |  |  |

| 1                                           | Select Output line 0 (Pin 84) as a Chip Select output.               |  |  |  |

| Bit 1:CO1 - Chip Select 1/Standard Output 1 |                                                                      |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------|--|--|--|

| 0                                           | Select Output line 1 (Pin 85) as a General Purpose inverting output. |  |  |  |

| 1                                           | Select Output line 1 (Pin 85) as a Chip Select output.               |  |  |  |

| Bit 2:CO2 - Chip Select 2/Standard Output 2 |                                                                      |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------|--|--|--|

| 0                                           | Select Output line 2 (Pin 86) as a General Purpose inverting output. |  |  |  |

| 1                                           | Select Output line 2 (Pin 86) as a Chip Select output.               |  |  |  |

| Bit 3:CO3 - Chip Select 3/Standard Output 3 |                                                                      |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------|--|--|--|

| 0                                           | Select Output line 3 (Pin 87) as a General Purpose inverting output. |  |  |  |

| 1                                           | Select Output line 3 (Pin 87) as a Chip Select output.               |  |  |  |

## Bits 4-7: SPECIAL FUNCTIONS FOR PROGRAMMABLE OUTPUT LINES 4-6

Programmable Output lines 4-6 can be individually configured as general purpose (inverting) outputs or as strobe outputs. These strobe signals may be used to clock any edge-triggered flip-flop or register. Additionally, Programmable Output line 6 may be programmed as an Auto-Power pin. This signal allows a peripheral to automatically control

its power on state, so that a separate power switch is not necessary. The external circuitry necessary for this passively pulls down the INIT line from the host. The power supply is turned on when the INIT line rises to a high logic level. The PPC34C60 will then monitor the host, and will bring the Auto-Power pin to a logic low level when the power can be shut off.

Output line N, configured as a Strobe signal, is normally high and pulses low momentarily when a 1 is written to Output Register bit N.

| Bit 4:S00 - Strobe 0/Standard Output 4 |                                                                      |  |  |  |

|----------------------------------------|----------------------------------------------------------------------|--|--|--|

| 0                                      | Select Output line 4 (Pin 44) as a General Purpose inverting output. |  |  |  |

| 1                                      | Select Output line 4 (Pin 44) as a Strobe output.                    |  |  |  |

| Bit 5:SO1 - Strobe 1/Standard Output 5 |                                                                      |  |  |

|----------------------------------------|----------------------------------------------------------------------|--|--|

| 0                                      | Select Output line 5 (Pin 43) as a General Purpose inverting output. |  |  |

| 1                                      | Select Output line 5 (Pin 43) as a Strobe output.                    |  |  |

| Bit 6,7:SP0,SP1 - Auto-Power/Strobe 2/Standard Output 6 |                                                                      |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------|--|--|

| 0,x                                                     | Select Output line 6 (Pin 42) as an Auto-Power Pin.                  |  |  |

| 1,0                                                     | Select Output line 6 (Pin 42) as a General Purpose inverting output. |  |  |

| 1,1                                                     | Select Output line 6 (Pin 42) as a Strobe output.                    |  |  |

#### OUTPUT REGISTER - 0010 (Read/Write)

| Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| BRESET | nOP6  | nOP5  | nOP4  | nOP3  | nOP2  | nOP1  | nOP0  |

|        | nPWR  | STB1  | STB0  | CS3   | CS2   | CS1   | CS0   |

|        | STB2  |       |       |       |       |       |       |

Each Output Register bit independently controls the operation of its respective Output pin. The function of each output pin, except for BRST (Pins 94 and 95), is determined by the data stored in the Output Configuration Register.

#### **CHIP SELECT OUTPUTS**

Output lines 0-3 (Pins 84-87) are programmable as Chip Selects (CS0-CS3) via the Output Configuration Register. When programmed as a Chip Select, the output pin will go low during bus operations if its associated bit in the Output Register is set. If the associated bit is not set in this register, the output pin will remain high.

#### STROBE OUTPUTS

Output lines 4-6 (Pins 44-42), when programmed as strobes (STB0-STB2) via the Output Configuration Register, will pulse low for two BUSCLK periods when the associated bit is set. The strobes recover and may be re-written at any time. Note: the strobe Output Register bits are reset automatically after the strobe is generated.

#### **AUTO-POWER OUTPUT**

Output line 6 (Pin 42), when programmed as Auto-Power (nPWR), via the Output Configuration Register, will remain at a high level as long as host activity is detected. When the chip determines that power may be shut off, this pin will go low.

There are two mechanisms driving this output. The first mechanism monitors the levels on the host port. If the port assumes the terminated levels or all low levels for 16 to 20 seconds, then the host is presumed off (or disconnected). The second mechanism monitors Host port activity (signal transitions). After a one minute period of inactivity (given that the WDOGEN pin is tied low) the watchdog will be triggered sending four beeps to the piezo driver. After completion of the tones the Auto-Power pin will go low.

## **GENERAL PURPOSE OUTPUTS**

Bit 7 (BRESET) and any other bits that are programmed through the Output Configuration Register as general purpose output bits are inverted and passed to the associated output pin.

## SOUND REGISTER - 0011 (Write Only)

| Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|--------|-------|-------|-------|-------|

| FREQ  | LTONE | STONE | SQULCH | rsvrd | rsvrd | rsvrd | rsvrd |

These bits allow the piezo driver to generate tones under program control.

#### Bits 0-3:rsvrd

These bits are reserved and should be written as zeros.

## Bit 4:SQULCH

Setting this bit terminates currently active low battery tones. If the low battery input (Pin 35) goes high, and then low again after this bit is set, low battery tones will resume. In order to squelch these low battery tones, this bit simply needs to be re-written with a logic "1".

## Bit 5:STONE

Setting this bit generates a 1/8 second tone. This bit self-clears after the tone is generated and when set again will generate another 1/8 second tone.

## **Bit 6:LTONE**

Setting this bit generates a 1/2 second tone. This bit self-clears after the tone is generated and when set again will generate another 1/2 second tone.

#### Bit 7:FREQ

This bit selects the Nominal frequency for the piezo driver circuit. 0 selects 2KHz, 1 selects 4 KHz.

## INPUT REGISTER - 0011 (Read Only)

| Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|-------|-------|--------|-------|-------|-------|-------|

| LOBATT | IRQ   | IRQ   | QIC-80 | IN3   | IN2   | IN1   | IN0   |

|        |       | LATCH |        |       |       |       |       |

The PPC34C60 has six Input pins, of which two are dedicated and four are uncommitted. The Input Register provides the Host with bit access to each of these input pins. Bit 4 is a special purpose bit useful for QIC-80 tape drive peripherals.

#### Bit 0:IN0 (Pin 82)

This bit represents the current state of the uncommitted input pin IN0.

## Bit 1:IN1 (Pin 83)

This bit represents the current state of the uncommitted input pin IN1.

## Bit 2:IN2 (Pin 37)

This bit represents the current state of the uncommitted input pin IN2.

#### Bit 3:IN3 (Pin 36)

This bit represents the current state of the uncommitted input pin IN3.

#### Bit 4:QIC-80

This bit will be set if more than 2.5ms have passed since the last rising edge of IRQ (pin 48). This function is designed for QIC-80 tape drives that require 2.5ms between the completion of one command and the start of a subsequent command.

#### Bit 5:IRQ LATCH

This bit is used to latch an interrupt request event and is enabled by setting INTEN (bit 6 of the Operation Register). When enabled this bit is set by a rising edge on the IRQ pin (Pin 48), and cleared by setting INTCLR (bit 7of the Operation Register), or by following a Clear Interrupt command from the Daisy Chain control packet (see the Daisy Chain Specification - Reference 3).

#### Bit 6:IRQ (Pin 48)

This bit represents the current state of the IRQ pin.

## Bit 7:LOBATT (Pin 35)

This bit represents the current state of the LOBATT input. When low, the piezo driver circuitry will provide a "low battery beep."

## OPERATION REGISTER - 0100 (Read/Write)

| Bit 7  | Bit 6 | Bit 5    | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|-------|----------|-------|-------|-------|-------|-------|

| INTCLR | INTEN | AUTO-INC | PDMA  | DIREC | DMAEN | D16   | F16   |

The bits in this register control the operation of the PPC34C60.

#### Bit 0:F16

Setting this bit overrides Pin 81 (nIO16), forcing all bus accesses to 16-bit. Use this bit to access a 16-bit peripheral which does not generate nIO16.

#### Bit 1:D16

This bit controls the bus width of the DMA cycles. 1 selects 16-bit, 0 selects 8-bit. nlO16 and F16 are ignored during DMA cycles.

#### Bit 2:DMAEN

This bit must be set for the DMA state machine to recognize DREQs. This bit will be automatically cleared when the DMA is complete.

#### Bit 3:DIREC

This bit controls the direction of DRAM - BUS DMA cycles. 1 selects a write from DRAM to BUS, 0 selects a read from BUS to DRAM.

## Bit 4:PDMA

Setting this bit enables the psuedo-DMA mode. In the PDMA mode DMA functions are performed, but CS is used instead of DACK to qualify the bus cycles. Use the PDMA mode to DMA to or from a device which does not explicitly support DMA.

#### **Bit 5:AUTOINC**

Setting this bit causes the bus address (A0-A7) to increment after every bus access.

#### Bit 6:INTEN

Setting this bit enables the interrupt latch.

#### Bit 7:INTCLR

Writing a 1 to this bit will clear any pending interrupt. This bit always reads 0.

## DRAM BUFFER SIZE REGISTER - 0101 (Read/Write)

| Bit 7 | Bit 6      | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1      | Bit 0 |

|-------|------------|-------------|-------|-------|-------|------------|-------|

|       | DMA DRAM I | BUFFER SIZE |       | H     |       | BUFFER SIZ | _     |

This register determines the size of the DRAM buffers, both for DMA DRAM and Host DRAM

accesses. The buffer sizes are encoded as follows:

| 0001 | = | 2   | Bytes | 1001 | = | 512  | Bytes |

|------|---|-----|-------|------|---|------|-------|

| 0010 | = | 4   | Bytes | 1010 | = | 1 K  | Bytes |

| 0011 | = | 8   | Bytes | 1011 | = | 2 K  | Bytes |

| 0100 | = | 16  | Bytes | 1100 | = | 4 K  | Bytes |

| 0101 | = | 32  | Bytes | 1101 | = | 8 K  | Bytes |

| 0110 | = | 64  | Bytes | 1110 | = | 16 K | Bytes |

| 0111 | = | 128 | Bytes | 1111 | = | 32 K | Bytes |

| 1000 | = | 256 | Bytes | 0000 | = | 64 K | Bytes |

## **HOST DRAM BUFFER POINTER REGISTER - 0110 (Read/Write)**

| Bit 7    | Bit 6      | Bit 5        | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|------------|--------------|-------|-------|-------|-------|-------|

| HOST DRA | M BUFFER P | OINTER (0-25 | 55)   |       |       |       |       |

This register sets the Host's DRAM pointer to the selected buffer. The DRAM address is calculated using this pointer, the DRAM Buffer Size Register, and the DRAM bus width from the Configuration Register. If MAXCNT is set during the Host to DRAM transfer, then this register is incremented upon reaching maximum count, and the DRAM address is recalculated for the next buffer.

A maximum of 256 buffers are available in this register. The actual number of buffers depends on the DRAM loaded, and the buffer size selected. If the pointer is incremented past the last buffer, it will wrap back around to the first buffer. No active buffer count is maintained; the driver software must prevent overwriting existing buffers.

## DMA DRAM BUFFER POINTER REGISTER - 0111 (Read/Write)

| Bit 7 | Bit 6 | Bit 5 | Bit 4     | Bit 3     | Bit 2   | Bit 1 | Bit 0 |

|-------|-------|-------|-----------|-----------|---------|-------|-------|

|       |       | DMA [ | RAM BUFFE | R POINTER | (0-255) |       |       |

This register sets the DMA DRAM pointer to the selected buffer. Its operation is similar to the Host DRAM Buffer Pointer Register. This

register is incremented upon completion of a DMA transfer and the DRAM address is recalculated for the next buffer.

## HOST MAX BLOCK BYTE-COUNT LOW REGISTER - 1000 (Read/Write)

| Bit 7 | Bit 6 | Bit 5    | Bit 4      | Bit 3     | Bit 2        | Bit 1 | Bit 0 |

|-------|-------|----------|------------|-----------|--------------|-------|-------|

|       |       | HOST MAX | BLOCK BYTE | -COUNT LO | W (HBC[7:0]) |       |       |

This register sets the low byte of the counter for Host block transfers. It is used in conjunction with MAXCNT in the Configuration register to

limit external DRAM and bus read accesses. The counter is reloaded with this value at every Address Write cycle.

## HOST MAX BLOCK BYTE-COUNT HIGH REGISTER - 1001 (Read/Write)

| ſ | Bit 7 | Bit 6 | Bit 5      | Bit 4      | Bit 3       | Bit 2         | Bit 1 | Bit 0 |

|---|-------|-------|------------|------------|-------------|---------------|-------|-------|

| ſ |       |       | HOST MAX E | SLOCK BYTE | -COUNT HIGI | H (HBC[15:8]) | )     |       |

This register sets the high byte of the counter for Host block transfers. It is used in conjunction with MAXCNT in the Configuration register to

limit external DRAM and bus read accesses. The counter is reloaded with this value at every Address Write cycle.

## DMA BYTE-COUNT LOW REGISTER - 1010 (Read/Write)

| Bit 7 | Bit 6 | Bit 5 | Bit 4     | Bit 3       | Bit 2  | Bit 1 | Bit 0 |

|-------|-------|-------|-----------|-------------|--------|-------|-------|

|       |       | DMA   | BYTE-COUN | IT LOW (DBC | [7:0]) |       |       |

This register sets the low byte of the 16-bit byte counter used for terminating DMA transfers.

Subsequent DMA transfers with the same byte count can be kicked off by resetting the DMA Enable bit in the Operation Register.

## DMA BYTE-COUNT HIGH REGISTER - 1011 (Read/Write)

| Bit 7 | Bit 6 | Bit 5       | Bit 4     | Bit 3       | Bit 2   | Bit 1 | Bit 0 |

|-------|-------|-------------|-----------|-------------|---------|-------|-------|

|       |       | D <b>MA</b> | BYTE-COUN | T HIGH (DBC | [15:8]) |       |       |

This register sets the high byte of the 16-bit byte counter used for terminating DMA transfers.

Subsequent DMA transfers with the same byte count can be kicked off by resetting the DMA Enable bit in the Operation Register.

## CONFIGURATION REGISTER - 1100 (Read/Write)

|   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|---|-------|--------|-------|-------|--------|--------|--------|--------|

| ſ | RST   | MAXCNT | SFIFO | rsvrd | RAMSZ1 | RAMSZ0 | CKSEL1 | CKSEL0 |

The bits in this register define the configuration of the system.

#### Bit 7:RST

Setting this bit resets the storage elements in the chip.

#### Bit 6:MAXCNT

When this bit is set, the Max Block Count Registers are used to limit the bus and DRAM accesses.

## Bit 5:SFIFO

This bit selects the operating mode of the Read FIFO. Setting this bit causes the internal Read FIFO to operate as a single-word read-ahead. If this bit is clear, the Read FIFO will operate as a two-word read-ahead.

#### Bit 4:rsvrd

This bit is reserved and should be written as zeros.

Bits[3:2]:RAMSZ[1:0]

| RAMSZ1 | RAMSZ0 | AMSZ0 DRAM BUS WIDTH                |  |  |  |

|--------|--------|-------------------------------------|--|--|--|

| 0      | 0      | Selects DRAM data width of 4 bits.  |  |  |  |

| 0      | 1      | Selects DRAM data width of 8 bits.  |  |  |  |

| 1      | Х      | Selects DRAM data width of 16 bits. |  |  |  |

Bits[1:0]:CKSEL[1:0]

| CKSEL1 | CKSEL0 | BUS CYCLE (BUSCLK)                    |

|--------|--------|---------------------------------------|

| 0      | 0      | Bus Cycle (BUSCLK) = System Clock / 2 |

| 0      | 1      | Bus Cycle (BUSCLK) = System Clock / 3 |

| 1      | 0      | Bus Cycle (BUSCLK) = System Clock / 5 |

| 1      | 1      | Bus Cycle (BUSCLK) = System Clock / 6 |

BUSCLK clocks the Bus Interface State Machine responsible for generating Bus Access, DRAM access, and DRAM Refresh timing. BUSCLK is also responsible for Output Strobe timing. System Clock is the SCLK input (pin 96) and is typically 24MHz.

#### CHIP REVISION LEVEL REGISTER - 1101 (Read Only)

| Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3    | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|---------|-------|----------|-------|-------|-------|

|       |       | TYPF ID |       | REVISION |       |       |       |

It is expected that the PPC34C60 will be used in various designs at different integration levels. This register provides a means of determining which type of chip is in use. The most significant five bits are reserved for a Type ID;

The least significant three bits may be used to identify different masks and/or process types. This document refers to chips with Revision Level values:

0000 0000

## PORT TEST WRITE REGISTER - 1110 (Write Only)

|   | Bit 7                           | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---------------------------------|-------|-------|-------|-------|-------|-------|-------|

| ſ | INCREMENTING WRITE TEST PATTERN |       |       |       |       |       |       |       |

The Port Test Write Register is used to determine the highest reliable printer port data transfer rate. An interface test must be performed at various speeds until data integrity can be assured. To enable this test, select the Port Test Write Register with an Address Write cycle. After being selected, the register looks for an incrementing pattern starting at 00. If data is written out of sequence, or if a communications error occurs, the ERR bit in the Data Transfer Control Register will be set.

## PORT TEST READ REGISTER - 1110 (Read Only)

| Bit 7 | Bit 6                          | Bit 6 Bit 5 |  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|-------|--------------------------------|-------------|--|-------|-------|-------|-------|--|

|       | INCREMENTING READ TEST PATTERN |             |  |       |       |       |       |  |

The Port Test Read Register verifies the read data transfer rate. To enable this test, select the Port Test Read Register with an Address Write cycle. After being selected, this Register

reads 00 when first addressed, and increments with every access. The ERR bit in the Data Transfer Control Register is not affected by the Port Test Read.

## DATA TRANSFER CONTROL REGISTER - 1111 (Read/Write)

|   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

| Г | ERR   | rsvrd | rsvrd | rsvrd | rsvrd | rsvrd | BURST | 8BIT  |

Bits 0 and 1 of this register provide options to regulate data transfer on non-enhanced ports. Bit 7 provides data transfer rate status information as described in the Port Test Write Register.

## Bit 7:ERR

This bit is set if an error occurs writing to the Port Test Write Register. It is cleared by selecting the Port Test Register with an Address Write cycle.

#### Bits 6-2:rsvrd

These bits are reserved and should be written as zeros.

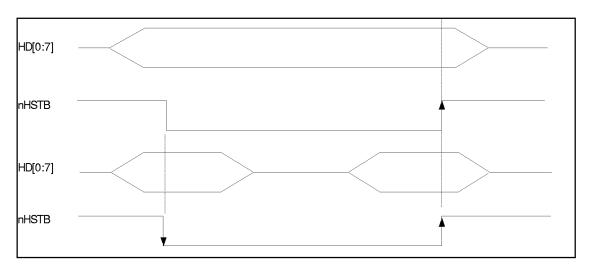

## Bit 1:BURST

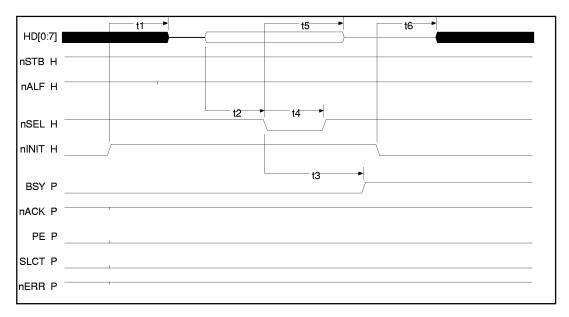

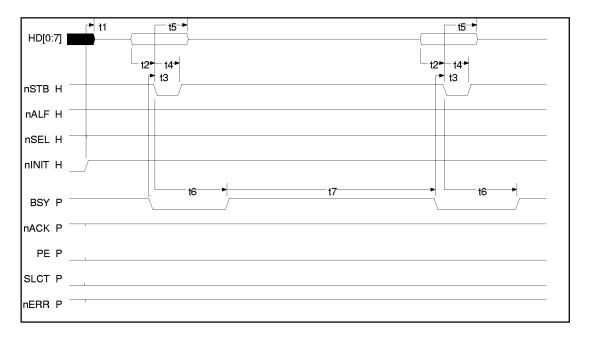

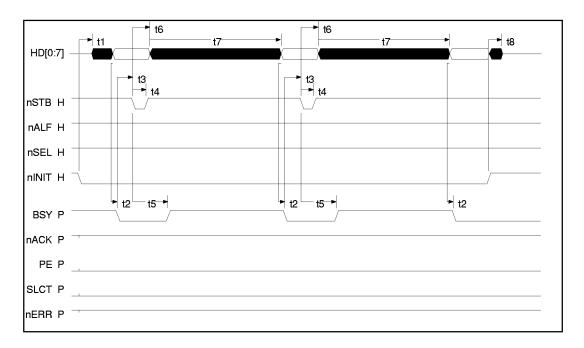

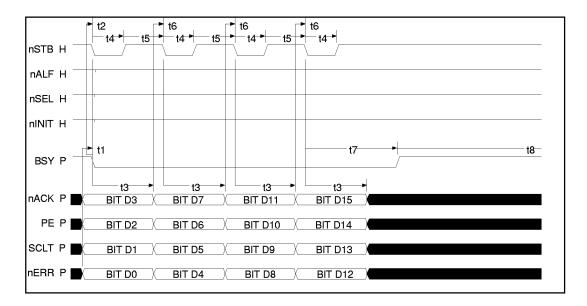

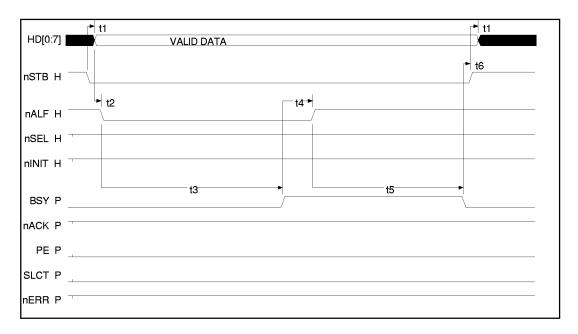

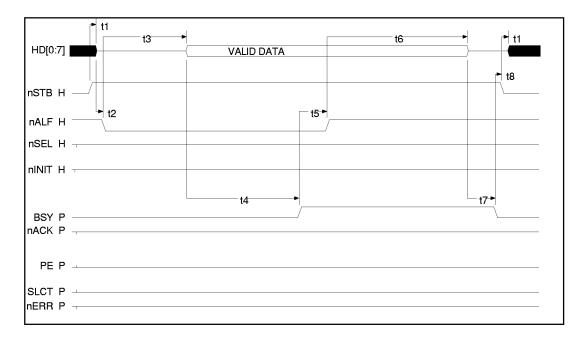

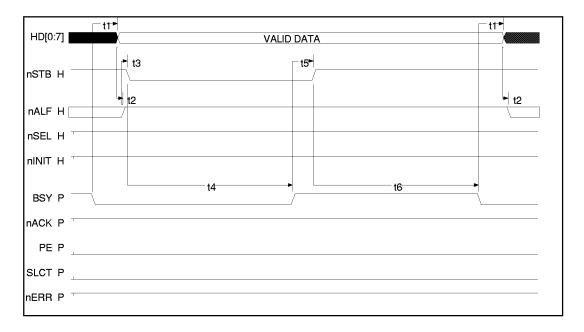

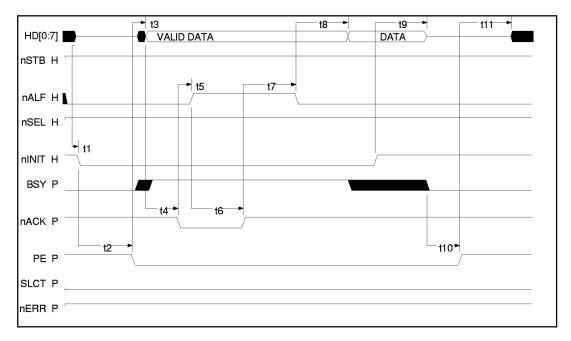

This bit is valid if the PPC34C60 is selected for Compatibility mode. Burst mode applies for reads and writes in Byte mode and reads in Nibble mode (see IEEE STD 1284 - Reference 1). Setting this bit maximizes data transfer by minimizing handshaking requirements. Data is latched on each edge of the Burst strobe as shown in Figure 5.

#### Bit 0:8BIT

This bit is only valid with a bi-directional port in Compatibility mode. Setting this bit selects Reverse Transfer Byte mode. Clearing this bit selects Reverse Transfer Nibble mode (see IEEE STD 1284 - Reference 1).

FIGURE 5 - BURST MODE

#### DRAM BUFFER OPERATION

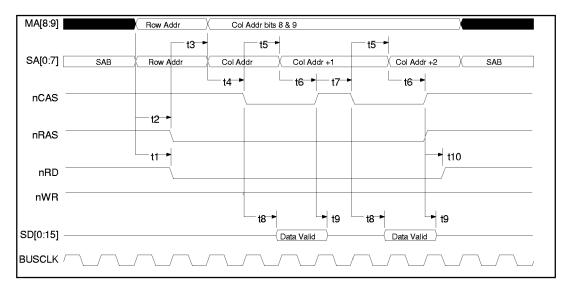

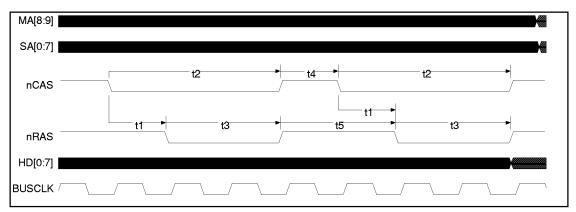

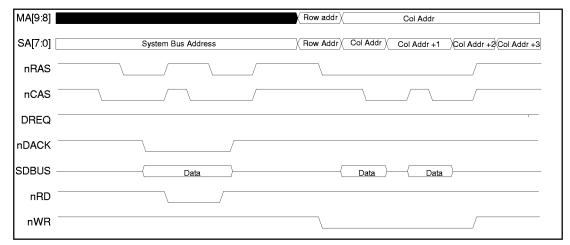

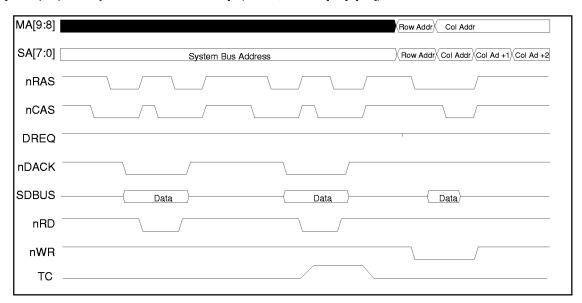

The PPC34C60 provides support for a DRAM buffer with DMA capability. DRAM bus widths of 4, 8, or 16 bits may be used, with linear 20 bit addressing. DMA to and from the DRAM may be either 8 or 16 bit cycles. The PPC34C60 will take care of matching the bus widths between the DMA Controller and the DRAM. If multiple DRAM accesses are necessary for a DMA cycle, they will use fast page mode.

DRAM refresh is automatic, and uses a CAS before RAS refresh method. The DRAM is

addressed as a number of buffers. The buffer size is programmable to 'power of 2' sizes between 2 and 64K bytes. A byte counter is used to control the DRAM access. It may be programmed to any value from 1 up to the buffer size. To prevent overwriting data, the byte counter should not be set to a value exceeding the buffer size.

The DRAM may be independently accessed by the host and the DMA Controller. There are separate buffer and byte counters for each. When a DRAM transfer is complete, the buffer number is incremented, and further DRAM access is blocked.

**DRAM Linear Address Mapping**

|     |             |             |            | - : : : : : : : : : : : : : : : : : : : | 11001 7100 |     | PP9        |             |            |            |  |

|-----|-------------|-------------|------------|-----------------------------------------|------------|-----|------------|-------------|------------|------------|--|

|     | MA9         | MA8         | SA7        | SA6                                     | SA5        | SA4 | SA3        | SA2         | SA1        | SA0        |  |

| ROW | <b>A</b> 19 | A17         | A15        | A14                                     | A13        | A12 | A11        | <b>A</b> 10 | <b>A</b> 9 | <b>A</b> 8 |  |

| COL | <b>A</b> 18 | <b>A</b> 16 | <b>A</b> 7 | <b>A</b> 6                              | <b>A</b> 5 | A4  | <b>A</b> 3 | <b>A</b> 2  | A1         | <b>A</b> 0 |  |

|     |             |             |            |                                         | 64K x N    | ١   |            |             |            |            |  |

|     | 256K x N    |             |            |                                         |            |     |            |             |            |            |  |

|     | 1M x N      |             |            |                                         |            |     |            |             |            |            |  |

#### DRAM PHYSICAL ADDRESSING

Users access the PPC34C60 DRAM through the Host and DMA logical addressing controls found in the Internal Registers. The system automatically calculates the physical DRAM addresses based on the values stored in these registers and the width of the system data paths.

The logical addressing controls are the 4-bit encoded Host and DMA DRAM buffer size controls in the DRAM Buffer Size Register (0101h) and the 8-bit DRAM buffer pointers in the Host DRAM Buffer Pointer Register (0110h) and the DMA DRAM Buffer Pointer Register (0111h). The DRAM Data Bus width is determined by RAMSZ0 and

RAMSZ1, bits 2 and 3, in the Configuration Register (1100h). The System DMA Data Bus width is determined by D16, bit 1 in the Operation Register (0100h). Host access is always eight bits.

The PPC34C60 determines physical DRAM addresses by calculating the buffer start address and adjusting this value for bus width. The buffer start address is the buffer pointer multiplied by the buffer size. If the DRAM Bus width is greater than or equal to the System Bus width then the buffer start address is the physical DRAM address, otherwise the physical DRAM address is the buffer start address multiplied by the System Bus width divided by the DRAM Bus width as shown in the Figure 6 below.

#### HOST/DMA Bus Width Greater Than DRAM Bus Width

Physical Address = Buffer Ptr \* Buffer Size \* System Bus Width / DRAM Bus Width

## HOST/DMA Bus Width Less Than or Equal to DRAM Bus Width

Physical Address = Buffer Ptr \* Buffer Size

For example, during a DMA transfer where;

- 1. the DRAM data bus width is four bits,

- 2. the DMA device data bus width is sixteen bits,

- 3. the DMA Buffer Size is 4096 bytes (1000h),

- 4. the DRAM Buffer Pointer is 2,

the Physical DRAM Address for the start of this transfer will be 32768 (8000h)

FIGURE 6 - DRAM PHYSICAL ADDRESSING

#### **SYSTEM DATA BUS CYCLES**

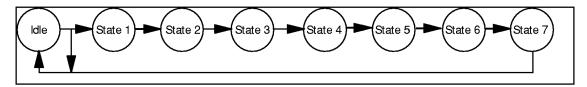

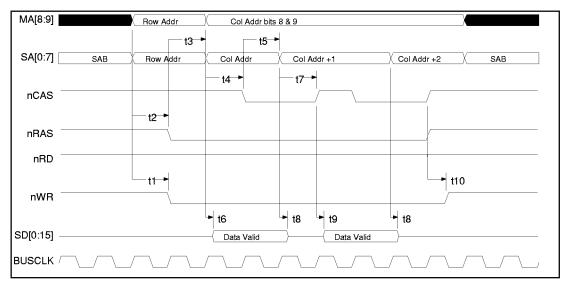

The System Data Bus is controlled by an internal state machine with seven states as shown below in Figure 7. The state machine is clocked by the BUSCLK which is software- programmable as SCLK divided by 2, 3, 5, or 6.

Three types of operations are performed by the bus interface: a Bus Cycle, a DRAM Access, and a DRAM Refresh. Refer to Tables 4-6 for the state flow description for each operation. The bus controller normally sits in the idle state. When a bus interface operation is kicked off, it advances to state 1. It then advances to the next state at every BUSCLK cycle. After state 7, the controller returns to idle.

## FIGURE 7 - GENERIC SYSTEM DATA BUS CYCLE

#### **BUS CYCLE TIMING**

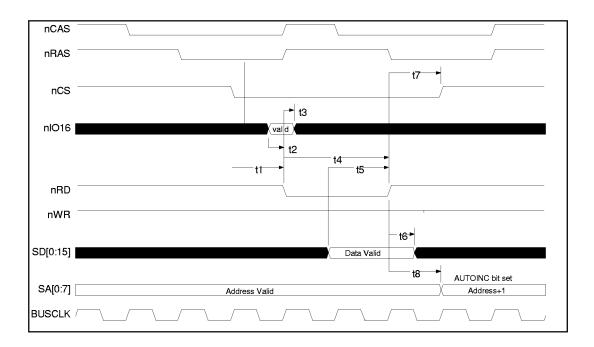

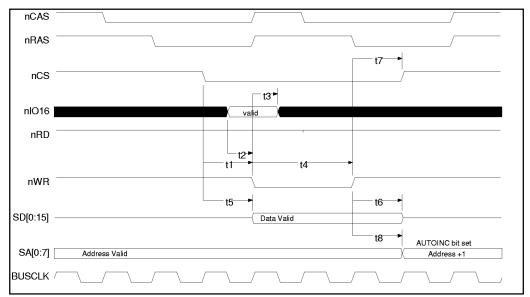

When an Address Write cycle selects a bus write, the next data received is written to the bus. The interface must, however, know whether to expect an 8 or 16 bit bus address. To determine the bus

width, a bus cycle is started from the Address Write cycle. This "pre-write" cycle asserts chip select and samples and latches nIO16. The write cycle is initiated after the first byte received for 8 bit writes, or after the second byte of data for 16 bit writes.

Table 4 - Bus Cycle State Flow Description