Xceljournal

SOLUTIONS FOR A PROGRAMMABLE WORLD

FPGAs Enable Greener Future for Industrial Motor Control

#### INSIDE

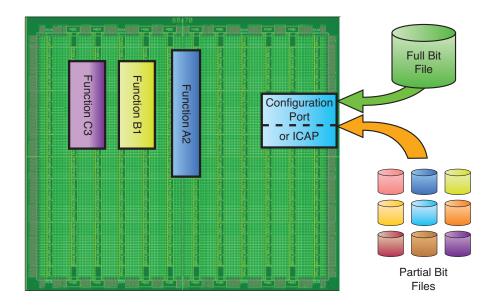

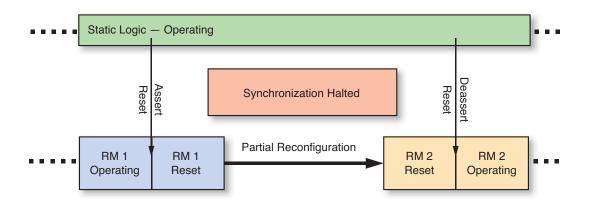

FPGA Partial Reconfiguration Goes Mainstream

Resurrecting the Mighty Cray on a Spartan-3 FPGA

How Hardware Accelerators Can Speed Your Processor's Sine Calculations

Xilinx Releases 2009 Quality Report

DESIGNED BY AVNET

# Introducing the First-ever Battery-powered Xilinx FPGA Development Board

The low-cost Xilinx<sup>®</sup> Spartan<sup>®</sup>-6 FPGA LX16 Evaluation Kit, designed by Avnet, combines a Spartan-6 LX16 FPGA with a Cypress PSoC<sup>®</sup> 3 controller and LPDRAM memory. This kit demonstrates a versatile batterypowered solution for low-power applications and provides a sound development environment for the most demanding applications. The baseboard can also be expanded with new FPGA Mezzanine Card (FMC) modules, making design porting and FMC swapping nearly seamless between Avnet and Xilinx platforms. FMC modules for ISM Networking, Dual Image Sensing and DVI I/O are currently available from Avnet.

#### Spartan<sup>®</sup>-6 FPGA LX16 Evaluation Kit Includes:

- Spartan-6 LX16 DSP FPGA

- LCD add-on panel

- USB A-mini B cable

- ISE<sup>®</sup> WebPACK<sup>™</sup> DVD

- AvProg configuration & programming utility

TAVNET

Downloadable documentation

& reference design

To purchase this kit, visit www.em.avnet.com/spartan6lx-evl or call 800.332.8638.

# **Quickly see inside your FPGA**

Get the most out of your test equipment and shave time out of your next debug cycle with Agilent oscilloscopes and logic analyzers. Our innovative FPGA dynamic probe application allows you to quickly connect to multiple banks of internal signals for rapid validation with real time measurements. Reduce errors with automatic transfer of signal names from the .cdc file from your Xilinx Core Inserter.

Also works with all InfiniiVision and Infiniium MSO models.

Toggle among banks of internal signals for incremental real-time internal measurements without: • Stopping the FPGA • Changing the design • Modifying design timing

Shown with: 9000 Series oscilloscope and 16900 logic analyzer with FPGA dynamic probes

See how you can save time by downloading our free application note. www.agilent.com/find/fpga app note

u.s. 1-800-829-4444 canada 1-877-894-4414

# Xcell journal

| PUBLISHER         | Mike Santarini<br>mike.santarini@xilinx.com<br>408-626-5981                      |

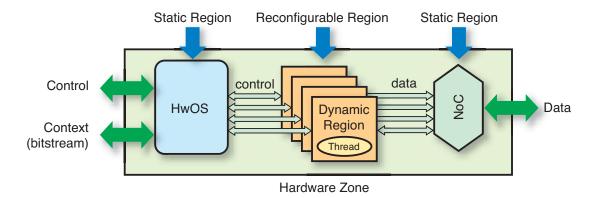

|-------------------|----------------------------------------------------------------------------------|

| EDITOR            | Jacqueline Damian                                                                |

| ART DIRECTOR      | Scott Blair                                                                      |

| DESIGN/PRODUCTION | Teie, Gelwicks & Associates<br>1-800-493-5551                                    |

| ADVERTISING SALES | Dan Teie<br>1-800-493-5551<br>xcelladsales@aol.com                               |

| INTERNATIONAL     | Melissa Zhang, Asia Pacific<br>melissa.zhang@xilinx.com                          |

|                   | Christelle Moraga, Europe/<br>Middle East/Africa<br>christelle.moraga@xilinx.com |

|                   | Miyuki Takegoshi, Japan<br>miyuki.takegoshi@xilinx.co                            |

| REPRINT ORDERS    | 1-800-493-5551                                                                   |

|                   |                                                                                  |

www.xilinx.com/xcell/

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 Phone: 408-559-7778 FAX: 408-879-4780 www.xilinx.com/xcell/

© 2010 Xilinx, Inc. All rights reserved. XILINX, the Xilinx Logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xilinx makes no warranties, express, implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim it might have against Xilinx for any loss, damage, or expense caused thereby.

## Xilinx Demonstrates Quality Commitment to Customers

few years ago, I wrote a cover story for *EDN* magazine on the subject of reliability in electronic design. In the process of researching the topic, I learned many interesting things—first of which is that most companies don't want to speak publicly about the quality of their products. Most, not all.

That original article was inspired by a shopping experience. While ringing up an Xbox 360 that I was purchasing for the kids, the salesperson strongly suggested I also buy an aftermarket cooling unit that plugged into the console to keep it from getting too hot. At the time it seemed absurd that after forking over hundreds of dollars for a videogame system I'd need to pony up extra money to make up for the possibility that there were deficiencies in the Xbox 360's design.

Needless to say, I didn't buy the cooling gizmo, and a year later (and a year after I wrote the reliability article) my Xbox 360 experienced what many Xbox 360 owners collectively called "the red ring of death." Microsoft subsequently fixed the defect (rumored to be a thermal issue with

an ASIC) for free for all its customers. The company must have forked over untold amounts of cash to respin the ASIC, set up the infrastructure to refurbish units, cover postage and organize the training for customer service folks to say "I've never heard of the term 'red ring of death" with some attempt at sincerity. Given the quasi recall, one has to wonder how much more successful the Xbox would have been had Microsoft not encountered the quality issue.

Quality is really something everyone in electronics should be more mindful of, especially as IC silicon processes continue to shrink and can accommodate evermore-elaborate designs that power a broader range of applications, spanning from consumer electronics to medical and mission-critical systems.

So given this background, I was very proud to see our quality team establish one of the few corporate quality reports available for public consumption. For many years, our customers have recognized Xilinx for its outstanding quality. The 2009 quality report—downloadable in PDF

form at *https://docs.google.com/viewer?url=http://www.xilinx.com/publications/prod\_mktg/2009-quality-annual-report.pdf*—highlights Xilinx's continued improvements in quality and customer satisfaction.

"Quality is no longer just about silicon," said Vincent Tong, senior vice president of worldwide quality and new product introductions. "The whole Xilinx design experience and IP ecosystem are now being transformed into the types of programs we've run for decades to drive relentless quality improvements and superb customer experiences."

In keeping with this thrust, Tong says this year's report will focus on Xilinx's Targeted Design Platforms, with an emphasis on how quality is important in each element of what Xilinx delivers to its customers. "We offer outstanding FPGAs, but our commitment to quality does not end with silicon," said Tong. "We are committed to improving the overall customer experience. Our customers have done amazing things with our products and we are committed to helping them become even more successful in creating wonderful new innovations."

I encourage you to give the 2009 quality report a read.

Mike Santarini Publisher

# VIRTEX

- High bandwidth serial connectivity with up to 72 low-power transceivers supporting up to 11.18Gbps

- Ultra high-performance DSP using up to 2016 low-power, performance-optimized DSP slices

- Integrated high-performance ExpressFabric<sup>™</sup> technology running at 600 MHz clocking and performance-tuned IP blocks

- Proven cost-reduction with EasyPath<sup>™</sup>-6 FPGAs

# Potential. Realized.

Unleash the full potential of your product design with Xilinx<sup>®</sup> Virtex<sup>®</sup>-6 and Spartan<sup>®</sup>-6 FPGA families — the programmable foundation for Targeted Design Platforms.

- Reduce system costs by up to 60%

- Lower power by 65%

- Shrink development time by 50%

#### Realize your potential. Visit www.xilinx.com/6.

© Copyright 2010 Xilinx, Inc. All rights reserved. Xilinx and the Xilinx logo are registered trademarks of Xilinx in the United States and other countries. All other trademarks are property of their respective holders.

#### CONTENTS

#### VIEWPOINTS

Letter From the Publisher At Xilinx, Quality Extends Beyond Silicon...4

# Cover Story

FPGAs Create a Greener Future for Industrial Motor Control

# APPLICATION FEATURES

Xcellence in Industrial FPGAs Fuel a Revolution in Intelligent Drive Design...12

Xcellence in A&D Using FPGAs in Mission-Critical Systems...16

Xcellence in Wireless Comms Virtex-4 Forms Foundation for GSM Security...20

Xcellence in Networking Research Design Platform Ignites Real-World Network Advances...24

**Xcellence in New Applications** A Flexible Operating System for Dynamic Applications...**30**

#### FOURTH QUARTER 2010, ISSUE 73

#### THE XILINX XPERIENCE FEATURES

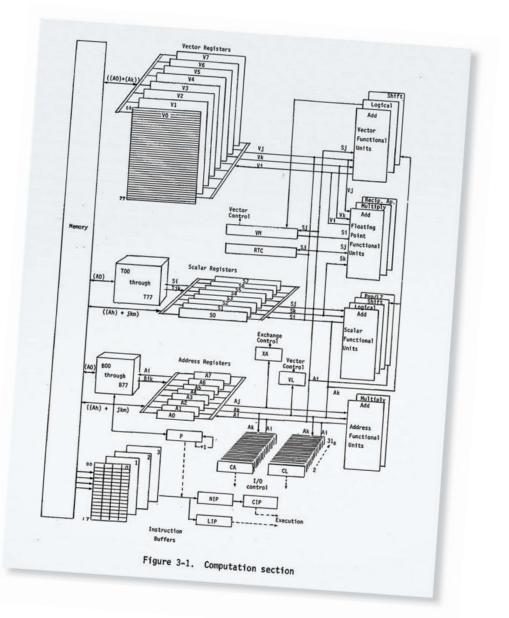

**Xperiment** Resurrecting the Cray-1 in a Xilinx FPGA...**36**

Xperts Corner FPGA Partial Reconfiguration Goes Mainstream...42

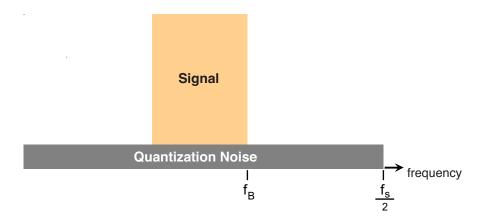

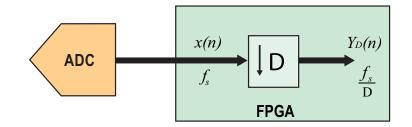

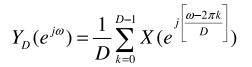

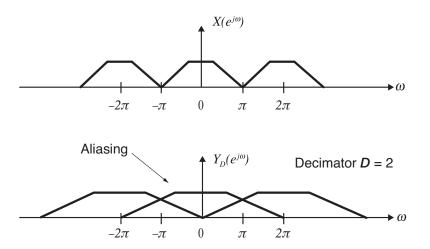

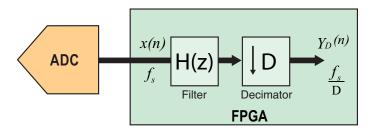

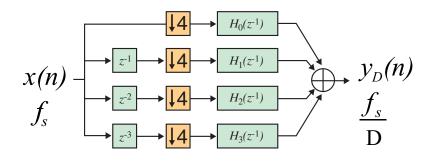

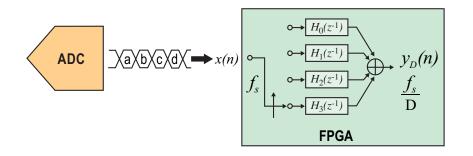

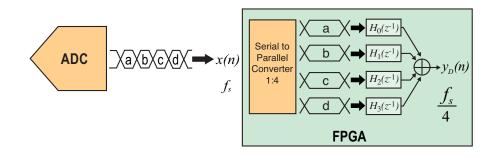

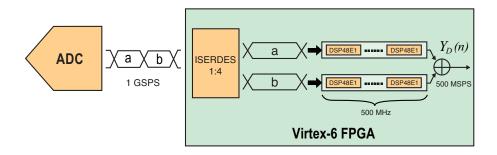

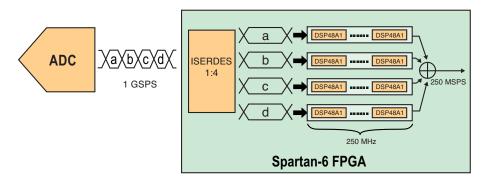

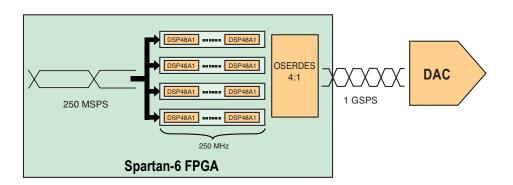

Xplanation: FPGA 101 Multirate Signal Processing for High-Speed Data Converters...50

Ask FAE-X How to Speed Sine Calculations for Your Processor...54

#### XTRA READING

Are You Xperienced? Take advantage of a simplified training experience...60

**Xtra, Xtra** The latest Xilinx tool updates and patches, as of September 2010...62

**Xclamations!** Share your wit and wisdom by supplying a caption for our cartoon, and win an SP601 Evaluation Kit...**66**

Xcell Journal recently received 2010 APEX Awards of Excellence in the categories "Magazine & Journal Writing" and "Magazine & Journal Design and Layout."

### COVER STORY

# Xilinx FPGAs: Creating a Greener Future for Industrial Motor Control

FPGAs are advancing the sophistication of industrial motor control products. An upcoming Targeted Design Platform aims to push it further.

by Mike Santarini Publisher, Xcell Journal Xilinx, Inc. mike.santarini@xilinx.com

Electric motors are everywhere—running toys and appliances in your home, cooling your office and powering cars, trains and factory assembly lines worldwide. They are even found in robots on Mars. Given this wide range of applications, it isn't surprising that there are dozens of types of electric motors, each with advantages and disadvantages. Function, size, power consumption/efficiency, performance, reliability, product life and, of course, cost are all attributes companies take into account when designing new electric motors and deciding which ones to incorporate in their products.

Today, however, the electric motor is at the dawning of a new era of maximum efficiency and automation built upon highly sophisticated FPGA-powered motor control systems. These new systems are just starting to make their way into the factories that create the world's products and consume a huge percentage of the world's power. In the first quarter of 2011, Xilinx will deliver a Targeted Design Platform that will allow companies to quickly develop the most advanced motor control systems to date and help factories reach new <u>levels of automation and efficiency</u>.

coll Journe

### 'Creating algorithms to control the efficiency of a motor is very complex, and adding these diagnostic capabilities on top of efficiency controls requires a far more sophisticated algorithm.'

#### The Growing Complexity of Factory Motor Control

Joe Mallett, senior product line manager in Xilinx's industrial, scientific and medical group, breaks industrial motor control into five elements: communications, control, drive, feedback and diagnostics.

At a minimum, said Mallett, all industrial motor control systems employ some type of communications to the outside world to allow a motor to work with other motors via master controllers or enterprise software. "Traditionally, the communications part of motor control for the factory has been based on serial communications, but it is rapidly moving to Ethernet due to the real-time requirements of communications, especially in safety applications, and to more easily link with the enterprise, which has been Ethernet based for years," said Mallett.

Then comes an element called "control," which is the term the industry generally uses to describe the algorithm at the heart of the motor control system. This algorithm controls another element called drive—essentially, the silicon power devices that switch the current on and off to drive the motor. The control and drive work together in what's called "the control and drive loop" to run motors at optimum performance and efficiency given their application.

The next element in a motor control system is feedback. "These are sensors that monitor various aspects of a motor in real time, including position, speed and torque, among others," said Mallett. "To ensure reliability, many companies are trying to minimize the number of sensors they use in their motor control systems. As such, many are moving to sensorless control, which requires high-performance, advanced algorithms to retrieve the feedback information."

The final piece of the system puzzle is diagnostics. "Being able to predict when a motor is likely to fail is becoming a common requirement," said Mallett. Here too, "prediction and diagnostics require fast decisions and sophisticated signalprocessing capabilities."

In recent years, most of the R&D and work in the motor control segment whether it be for factory equipment, automobiles or even toys—has focused on improving motor efficiency.

Factories depend heavily on electric motors to power robots, tools, assembly lines and HVAC (heating, cooling and ventilation) systems. Many run all this machinery 24 hours a day, seven days a week, to fill orders and keep revenue coming in. As such, reliability and efficiency are paramount, as an unexpected failure in an electric motor can bring an entire assembly line or factory to a halt, and may even harm workers.

#### Advanced Motor Control Combines Efficiency, Reliability and Safety

Further, with 24/7 operation, energy consumption has a drastic impact on the total cost of ownership and bottom line. In the factory space, efficiency is increasingly mandatory, said Mallett.

"It's always great to drive down energy bills, but the fact is, many factories have no choice in the matter," said Mallett. "They have to comply with government mandates to reduce the pollution they create and the energy they consume. However, most factories can't afford to shut down for a long period of time and replace their entire manufacturing lines with newer, more efficient ones. What they would prefer to do is run their existing machinery more efficiently and swap in newer, more efficient motors over time, as needed-keeping factory downtime to a minimum." To that end, equipment manufacturers are racing to develop the most efficient motor and control combination possible to help factories meet their energy-savings goals, Mallett said.

However, Giulio Corradi, ISM systems architect for the industrial, scientific and

medical markets at Xilinx, pointed out that it's quite complex to create a motor control unit that makes even one motor more efficient because for maximum efficiency, the control algorithms must be tailored to a given motor's targeted task in the factory. The complexity of the algorithm grows exponentially if it needs to control multiple motors and even more so if the motor needs to incorporate feedback or diagnostics.

Corradi explained that even the most basic motor control systems employ complex algorithms to regulate the amount of power going into a motor or series of motors. Incorporating feedback and diagnostics adds another level of complexity, but delivers systems that will instantly warn operators if there is a potential problem with a motor, and perhaps identify what the problem is and gauge its severity. The most advanced systems even estimate how long the motor will last given the problem.

"All motors will eventually wear out, but it's extremely valuable if you can estimate if and when it will happen," said Corradi. "If a motor in an assembly line fails unexpectedly, it can bring an entire factory to a standstill. Creating algorithms to control the efficiency of a motor is very complex, but adding these diagnostic capabilities on top of efficiency controls requires a far more sophisticated algorithm, and a sophisticated device to execute that algorithm."

The most advanced control systems today include active, real-time safety features such as sensors that spot cracks in machinery and stop the machines in milliseconds to avoid catastrophic failure or conditions that could injure factory workers. Mallett notes that in many cases these advanced safety features are also becoming standardized and mandated by government. The IEC 61508 standards effort, for example, stipulates that control systems include functionality to detect potentially dangerous conditions and prevent hazardous events. In Europe, the

9

#### COVER STORY

Machinery Directive 2006/42/EC went into effect in December 2009, mandating that machinery manufacturers provide products that comply with IEC 61508.

But motor control in the factory is not restricted to monitoring efficiency, safety and motor longevity, Corradi explained. Companies also leverage motor controls to make robots perform ever-more-sophisticated and exacting functions. "A single robot has several motors and they must be able to perform several functions," said Corradi. "They must be programmable to change tasks and they must work in concert with other robots. The algorithms to run the motors in a robot are extremely advanced."

Even an HVAC system motor control is vitally important. Many factories use chemicals, solvents and contaminants and must ventilate them properly. Clean rooms must also minimize contaminants. These machines must operate correctly all the time.

Mallett points out that in modern factories all these systems—assembly lines, robots and HVAC—are interrelated and interconnected. They must be orchestrated in concert with one another. In many cases, newer systems use high-speed wired interconnect standards such as Industrial Ethernet, while some are starting to even use wireless communications. Since factories tend to be noisy environments, the latter trend adds further layers of complexity to motor control designs.

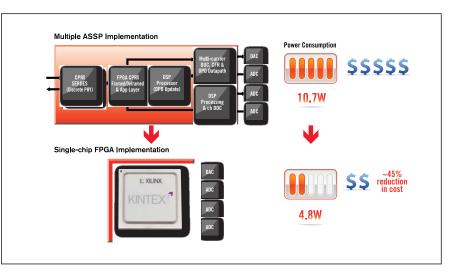

#### FPGAs Displacing Off-the-Shelf Processors in Advanced Motor Control

Because of all this complexity on the factory floor, the demand for processing performance is growing exponentially and programmable logic control is increasingly displacing traditional processor-based motor control.

Historically, engineers have used microcontrollers for factory-class motor control, said Corradi. But that design approach is hitting a wall. "The new factory systems are so sophisticated now and integrate so many functions that you would have to use several microcontrollers, and often the biggest and most expensive ones," he said. "Then, after you've done that, you are fairly restricted in what functionality you can add to your motor control. With an FPGA, you can add all the advanced features required to a single chip and even add new functions after you've deployed the system in a factory."

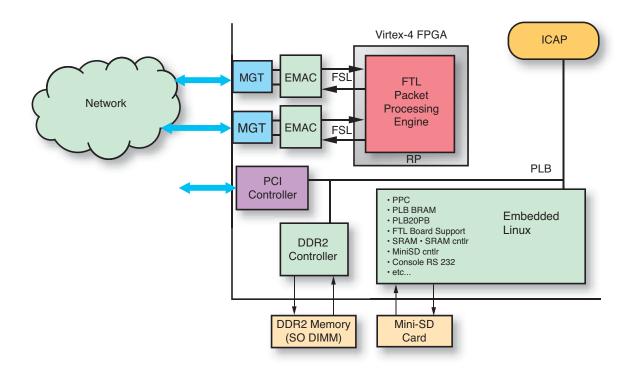

A prime example of this elevated complexity is a new trend called "networked control systems," in which motor control feedback is routed via networking to enterprise software systems, not just to a local operator's station. In this application, "not only are the control algorithms more complex, but also, the network is essentially 'in-the-loop,' demanding real-time performance far beyond what standard off-the-shelf processors can handle," Corradi said. "By contrast, FPGAs can perform networking and control support simultaneously" (see Figure 2).

"A single FPGA can really do the work of dozens of microcontrollers," said Corradi. "It's much easier to have this com-

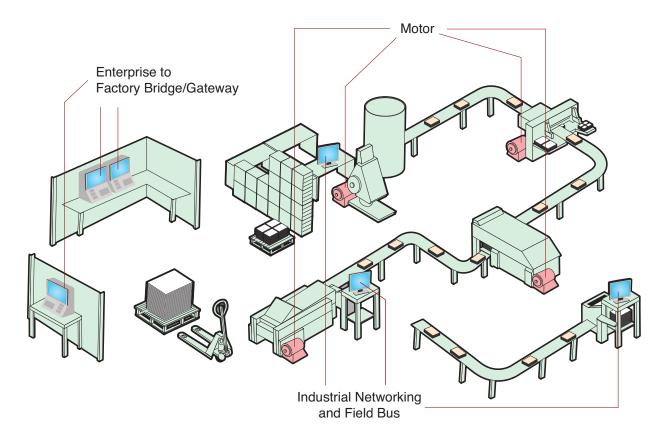

Figure 1 – Xilinx FPGAs play an increasing role in advanced motor control at multiple points in the factory and even the connection between the factory and the enterprise.

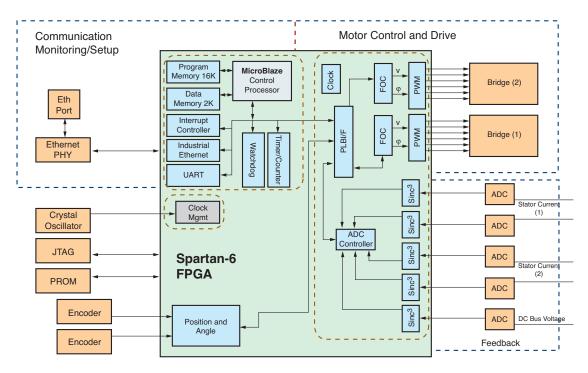

Figure 2 – Engineers can implement many motor control features on a single FPGA.

plexity in one device rather than distributed across a board with many processors."

What's more, FPGAs excel at parallel as well as serial operations. This means designers can program a single FPGA to coordinate multiple motor controller functions for a variety of motors simultaneously. The realtime requirements don't stop there, but also include functional safety features, with the concomitant need to shut down a line in milliseconds if attached sensors detect unsafe conditions. "Functional safety is enabled within FPGAs by using silicon-specific functions, dedicated hardware IP and a software stack that, combined, make the complete system," said Corradi.

Corradi noted that customers can leverage an FPGA's reliability and the design techniques Xilinx has refined over 20 years for aerospace applications to implement safety features in their motor control systems. "Companies that add safety features to their motor control units typically have to design specific chips dedicated to safety," said Corradi. "In an FPGA, you can partition a segment of the chip just for this purpose and have a clear separation between the safety and nonsafety segments of the chip. This makes it easier if they need to create derivative systems or upgrade systems, because they can simply leave the safety part of the chip alone." Another option would be to add duplicate or triplicate functions in the design to ensure space-quality safety controls in these systems.

In fact, the companies that specialize in the safety aspect of motor control have been the early adopters of FPGA technology. "They see the advantage in how the FPGA could clearly bring a reduction in development times and additional reliability, and a clear separation of safety and nonsafety functions," Corradi said.

#### Xilinx Readies Industrial Ethernet Motor Control Targeted Design Platform

It is for these reasons that companies are turning to FPGAs over processor-based systems for industrial motor control. Mallett predicts that the pace of adoption will advance rapidly over the next few years, especially once engineers get their hands on the upcoming Xilinx Targeted Design Platform tailored for factory automation and motor control.

This market-specific platform will pull all the pieces together for the end customer developing advanced motor controllers. The development environment will include the hardware, tools and IP needed to integrate Industrial Ethernet and motor control into a single platform. Corradi said the Targeted Design Platform will also include a targeted reference design to help customers shorten their development cycles and differentiate their products.

Xilinx will base the first-generation system on a Spartan<sup>®</sup>-6 FPGA running a MicroBlaze<sup>®</sup> processor. Looking forward, one can envision a platform leveraging Xilinx's ARM<sup>®</sup> MPU-based Extensible Processing Platform, further accelerating the role of programmable logic in motor control design—potentially saving factories millions of dollars and ensuring the safety of industrial workers worldwide.

A key part of the factory automation Targeted Design Platform is a library of general-purpose and market-specific IP that Xilinx and its alliance partners will offer to help customers develop Spartan-6based integrated motor controllers quickly (see related story, page 12).

Mallett predicts that as companies become more familiar with programming FPGAs for motor control systems that end up in factories, they will start to use FPGA-based motor control across other product lines and for other control applications. "Companies are always seeking ways to build a better motor or at least a better way to control them, and FPGAs are ideal for the job," said Mallett. **\***

### XCELLENCE IN INDUSTRIAL

# Revolutionizing Intelligent Drive Design with the Spartan-6

Xilinx Design Services uses the SP605 Evaluation Kit and state-of-the-art motor control IP to prototype an interface-independent intelligent drive control system.

by Kasper Feurer Embedded Systems Engineer Xilinx Ireland kasper.feurer@xilinx.com

Richard Tobin Embedded Systems Engineer Xilinx Ireland richard.tobin@xilinx.com

Manufacturers of intelligent drives, as well as many other players in the automotive and ISM sectors, are facing numerous challenges to satisfy new market demands and meet constantly evolving standards. In modern industrial and automotive applications, motors must provide maximum efficiency, low acoustic noise, a wide speed range and reliability, all at an acceptable cost. On today's factory floor, motor-driven equipment consumes twothirds of total electricity energy, leading to the urgent need to develop more energyefficient systems. Interoperability is also a critical design requirement, as in many cases a drive will serve as a component in a large-scale process. A key factor that influences this requirement is the breadth of industrial networking protocols (the field buses) and associated device profiles, which serve to standardize the representation of a drive within a network. The field buses themselves (for example, CAN and Profibus) are diverse, and despite sharing the same generic name they are not readily interchangeable. In an attempt to reduce cost and improve communications between industrial controllers, field bus

providers have developed Ethernet-based industrial networking solutions, and several new protocols, such as EtherCAT, Profinet and EtherNet I/P among others, have emerged in recent years. However, these are also divergent technologies and drive manufacturers struggle to support all the major players.

Xilinx Design Services (XDS) has addressed all of these issues in developing an FPGA-based prototype motor control platform supporting the CANopen and EtherCAT interfaces for a key player in the ISM space. Our role was to design and implement a fully functional and modular system fit for reuse in the customer's next-generation intelligent drives. The Xilinx<sup>®</sup> Spartan<sup>®</sup>-6 FPGA SP605 Evaluation Kit Base Targeted Design Platform, along with third-party IP, provided state-of-the art motor control algorithms and industrial networking support in a modular system architecture, yielding an efficient and scalable design.

B

100

#### **Choosing the FPGA Path**

The customer's existing, microcontrollerbased solutions did not deliver what the customer wanted most: a scalable platform. A Spartan-6 FPGA-based intelligent drive control system provides all the necessary scalability, logic and compute power in a single chip, reducing costs while also avoiding obsolescence. Such a platform can be upgraded for years to come with the latest standards of industrial networking and the most efficient motor control algorithms. In addition, the reprogrammable nature of FPGAs facilitates customization of a single base motor control system to meet specific customer requirements, allowing easy integration into the existing industrial network. In short, the Spartan-6 FPGA fulfills all the challenging requirements of the industrial space.

For newcomers to the world of FPGAbased system design, like our customer, Xilinx's Targeted Design Platforms offer the ideal starting point by providing a robust set of well-integrated and tested elements right out of the box. You can automate an even greater portion of the final design by adding domain-specific and market-specific platform offerings to the Base platform. These targeted reference designs reduce the learning curve by demonstrating FPGA implementations of real-world concepts, allowing customers to put their muscle into the design and development of the differentiating features of the final product.

Our solution combined the Spartan-6 SP605 Evaluation Kit with third-party offerings-namely the NetMot FMC board and IP from QDeSys plus industrial networking IP from Bosch and Beckhoff. Not only were all the basic building blocks of the desired system in place from the start, but we could proceed with prototype development without the need for a custom FPGA board, thus allowing the customer to verify the viability of this new platform at minimum cost. To further enhance the time-to-market and reduce the risks involved with a first-time FPGA system design, the customer asked us to not only deliver this prototype but also to support the adoption of FPGAs in its nextgeneration intelligent drives.

Ultimately, both engineers and their managers benefited by this approach. The former learned FPGA-based design faster, armed with best practices gleaned from XDS, while the management slashed the time it took to deliver product along with the business risks.

#### Intelligent Drive Control System Prototype

The XDS portfolio covers the entire FPGA design development cycle, from specification creation through coding, verification, timing closure and system integration. Drawing on years of experience in embedded-processor system and

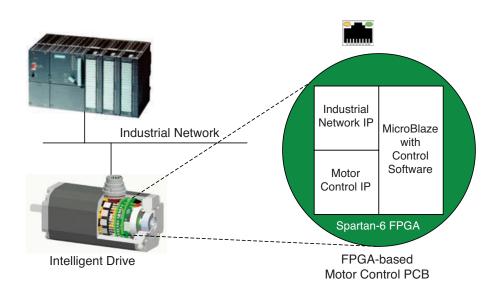

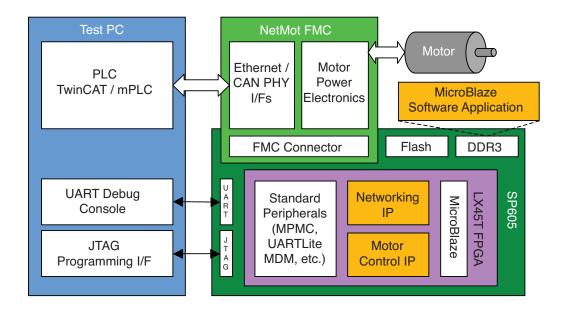

Figure 1 – The drive control system prototype

software application design, along with the ability to integrate third-party IP, good project management practices and a fully certified ISO9001 development process, XDS delivered the intelligent drive control system prototype very early in the customer's product development cycle. The resulting custom Targeted Design Platform enabled the customer's engineers to familiarize themselves with FPGA design processes and hence optimize the power of this new technology in their next-generation products.

Let's look more closely at the main components of this intelligent drive control system prototype as illustrated in Figure 1.

The programmable logic controller (PLC) operates the intelligent drive, which is attached to the industrial network in real time. For the purpose of this prototype, we used two PC-based PLCs to handle the two industrial networking standards the system supports: miControl mPLC for the controller-area network (CAN) and TwinCAT for the EtherCAT industrial Ethernet field bus system. The PLC generates predefined command messages (for example, start and stop) and verifies the correct behavior of the motor by analyzing the responses received (current speed, temperature, voltage and so on). Depending on the combination of PLC and the type of intelligent drive (CAN or EtherCAT), the industrial network is either a serial bus or a standard 100-Mbit Ethernet interface. For both solutions the prototype uses a direct line link between the PLC and the motor—either a two-wire serial interface for CAN, or a standard RJ45 100Base-TX Ethernet connection for EtherCAT.

The motor control printed-circuit board, typically one of a number of PCBs in an intelligent drive, is dedicated to controlling the motor via commands from the PLC. This motor control board is where the flexibility of an FPGA comes into play. Rather than a single interface and single motor control algorithm solution, as in the conventional ASIC/microprocessor approach, the Spartan-6 FPGA can be reprogrammed with dedicated networking and motor control IP blocks, as well as the control software to suit the customer's specific needs. In this manner, a single FPGAbased PCB can fulfill the functions of many ASIC-based boards. At the same time, it future-proofs the intelligent drive by providing a mechanism to update the IP to the latest standards.

Rather than designing this motor control board from scratch, XDS exploited the

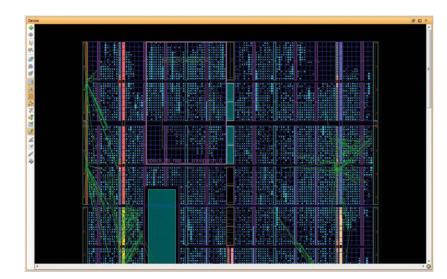

Figure 2 – Prototype Spartan-6 FPGA-based motor control board

Targeted Design Platform concept, integrating all the customer's desired elements by combining the Xilinx Spartan-6 SP605 Evaluation Kit, the NetMot FMC board, and industrial networking and motor control IP, thus delivering this proof-of-concept prototype before the customer had completed its new PCB. Figure 2 shows how we combined the various components to yield the prototype development platform. As a result, the customer greatly reduced the integration effort and was able to explore the best design options without re-engineering the final design.

The SP605 Base Targeted Design Platform is a general-purpose FPGA platform that hosts a Spartan-6 LX45T in a proven implementation, alongside many commonly needed peripherals such as DDR3 RAM, flash memories for program/bitstream storage, UART for debug and JTAG for FPGA programming. Another key element of the SP605 as well as all recent Xilinx boards is the FPGA Mezzanine Card (FMC) connector, which enables designers to expand the base board with custom functions and interfaces.

This feature of the SP605 enabled us to build on this base by using features provided by the QDeSys NetMot FMC (*www.qdesys.com*), which implements the power electronics required for motor control, such as voltage inverters and ADCs for obtaining sensor data. You can connect the motor directly to these inputs/outputs as shown in Figure 2. The NetMot FMC also expands the industrial network connectivity features of the SP605 by adding two CAN and two Ethernet physical-layer interfaces. They are accessible to the FPGA via the FMC connector and a PLC over standard interfaces.

The test PC functions as both a host for the PLC software and an FPGA programming/debug platform using the UART and JTAG interfaces. In addition, we used this test PC to develop the MicroBlaze<sup>TM</sup> embedded-processor system for the SP605's LX45T FPGA with Xilinx's ISE<sup>®</sup> 12.1 Design Suite. This embedded system is responsible for processing the commands received from the PLC and controlling the motor accordingly.

The MicroBlaze software application, networking and motor control IP blocks seen in Figure 2 represent the modules of the design that change depending on the interface (EtherCAT or CANopen) and motor type chosen. One of the main challenges for XDS was to ensure that the process of switching between these options be as simple as possible, thus ensuring that the customer would be able to reuse the same methods in the future for further industrial network types like Profinet and for new motors.

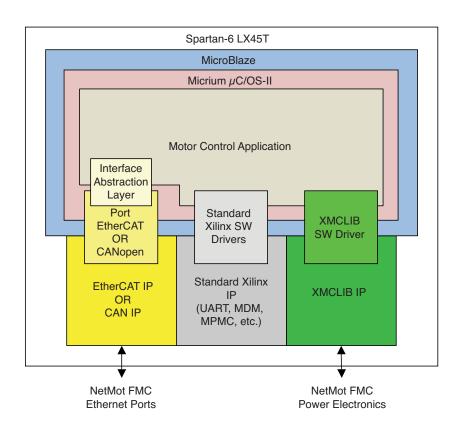

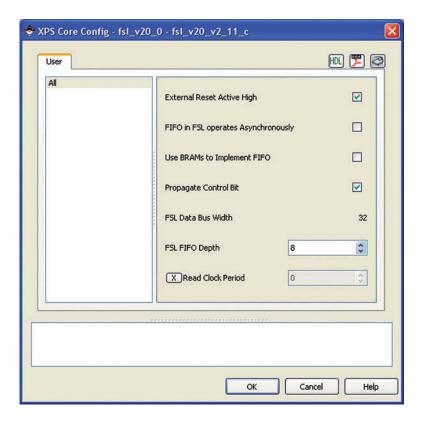

#### **Implementation Details**

Let's examine these parts of the Spartan-6 embedded system in greater detail. As shown in Figure 3, the motor control IP block that we used-the Xilinx Motor Control Library (XMCLIB)-is identical for both versions of the design. This custom IP core, which permits the FPGA to control the NetMot FMC's motor power electronics, plugs directly into Xilinx's Embedded Development Kit (EDK). This allowed us to add the IP to our embedded design from the Xilinx Platform Studio (XPS) project and configure it to suit the motor that was connected to the FPGA via the FMC connector. The XMCLIB software driver is a set of low-level functions giving the motor control application access to the XMCLIB register interface.

The networking IP, on the other hand, is where the system differs for the two variants. For the CAN version of the design we chose the standard LogiCORE<sup>TM</sup> IP XPS Controller Area Network, delivered with the ISE 12.1 design suite and licensed by Bosch GmbH. For the EtherCAT version, we used Beckhoff's EtherCAT Slave Controller IP

Figure 3 – CAN/EtherCAT embedded system

Core (*www.beckhoff.com*) for Xilinx FPGAs. Both of these IP cores are also available from the XPS tools' IP Catalog tab, making integration and configuration in the design very straightforward. In this case, instead of using a simple driver to provide access to the networking IP, we used Port's (*www.port.de*) CANopen and EtherCAT Stack solutions, which offer fully featured protocol implementations right out of the box.

Finally, we designed a custom embedded-software application to run on Micrium's (*www.micrium.com*)  $\mu$ C/OS-II on the MicroBlaze processor system. This embedded operating system enhances the prototype system's real-time capabilities and provides multitasking, message queues and semaphores, among other features.

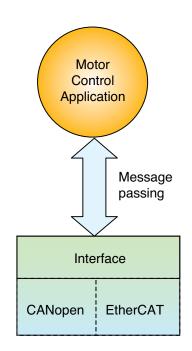

We also recognized that it was important to structure the application in a way that would allow us to retarget it to different network interfaces. To achieve this, we designed an interface abstraction layer that lets us encapsulate the communications and motor control elements of the software.

Figure 4 – Interface abstraction layer

On one side of this interface (Figure 4), we implemented a networking module (Port's CANopen or EtherCAT) to manage the communications for the networking IP available in the system. These modules plug in seamlessly to our interface abstraction layer. At the top level of these stacks, we pass communications and control data (such as PDOs, SDOs and NMT state transitions) into the abstraction layer, which interprets the data and presents it to the motor control application as commands such as start/stop or rotate at a specified velocity or to a specified position.

To determine a common set of messages and commands for the interface abstraction, we researched existing publications in the area of industrial networking and encountered the IEC 61800-7 standard. For the existing field bus technologies, several schemes are used to standardize the communications with a drive device (such as CiA-402 for CANopen or PROFIdrive for Profinet). IEC 61800-7 presents a common representation of a drive and proceeds to provide a set of mappings between this representation and the existing drive profiles.

The concepts presented in this standard allowed us to develop our interface abstraction, which in turn allowed us to encapsulate the networking component of the system. We can therefore change the networking interface present in the system, and we only need to tailor a small portion of the software to make it compatible with the existing motor control application.

#### **Going Forward**

The successful delivery of the intelligent drive control system prototype has clearly illustrated the potential power of FPGAs in industrial Ethernet networking, field buses and motor control. Although some work remains to develop a fully featured product, XDS tailored a Targeted Design Platform and enhanced it for the customer, creating a custom solution that will greatly reduce the risks and effort required to come to a final, engineered product. As a next step, XDS is investigating expanding this Targeted Design Platform to support the Profinet IP core and stack, demonstrating that the modular approach and the design practices adopted are very effective for the customer. 🍕

### XCELLENCE IN AEROSPACE & DEFENSE

# Using FPGAs in Mission-Critical Systems

SEU-resistant state machines hold the key to adapting programmable logic devices for high-reliability applications.

by Adam Peter Taylor Principal Engineer EADS Astrium aptaylor@theiet.org

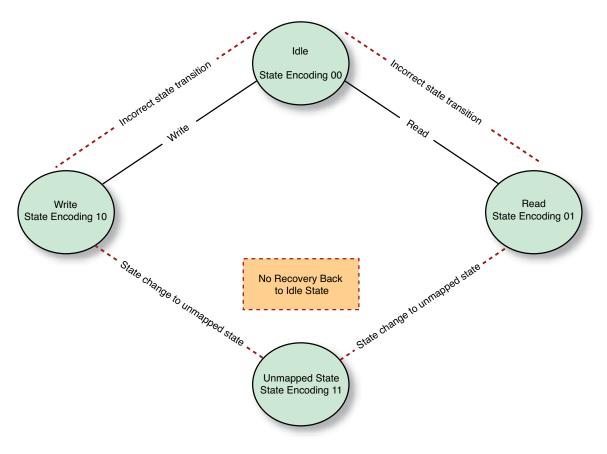

Dramatic surges in FPGA technology, device size and capabilities have over the last few years increased the number of potential applications that FPGAs can implement. Increasingly, these applications are in areas that demand high reliability, such as aerospace, automotive or medical. Such applications must function within a harsh operating environment, which can also affect the system performance. This demand for high reliability coupled with use in rugged environments often means you as the engineer must take additional care in the design and implementation of the state machines (as well as all accompanying logic) inside your FPGA to ensure they can function within the requirements.

One of the major causes of errors within state machines is single-event upsets caused by either a high-energy neutron or an alpha particle striking sensitive sections of the device silicon. SEUs can cause a bit to flip its state ( $0 \rightarrow 1$  or  $1 \rightarrow 0$ ), resulting in an error in device functionality that could potentially lead to the loss of the system or even endanger life if incorrectly handled. Because these SEUs do not result in any permanent damage to the device itself, they are called soft errors. The backbone of most FPGA design is the finite state machine, a design methodology that engineers use to implement control, data flow and algorithmic functions. When implementing state machines within FPGAs, designers will choose one of two styles, binary or "one hot," although in many cases most engineers allow the synthesis tool to determine the final encoding scheme. Each implementation scheme presents its own challenges when designing reliable state machines for mission-critical state machine does not enter when it is functioning normally. Designers must address these unused states to ensure that the state machine will gracefully recover in the event that it should accidentally enter an illegal state. There are two main methods of achieving this recovery. The first is to declare all  $2^{N}$  number of states when defining the state machine signal and cover the unused states with the "others clause" at the end of the case statement. The others clause will typically set the outputs to a safe

startup following reset release. Typically, these states also keep the outputs in a safe state; should they be accidentally entered, the machine will cycle around to its idle state again.

One-hot state machines have one flipflop for each state, but only the current state is set high at any one time. Corruption of the machine by having more than one flip-flop set high can result in unexpected outcomes. You can protect a one-hot machine from errors by

Figure 1 – Even a simple state machine can encounter several types of errors.

systems. Indeed, even a simple state machine can encounter several problems (Figure 1). You must pay close attention to the encoding scheme and in many cases take the decision about the final implementation encoding away from the synthesis tool.

#### **Detection Schemes**

Let's first look at binary implementations (sequential or "gray" encoding), which often have leftover, unused states that the state and send the state machine back to its idle state or another state, as identified by the design engineer. This approach will require the use of synthesis constraints to prevent the synthesis tool from optimizing these unused states from the design, as there are no valid entry points. This typically means synthesis constraints within the body of the RTL code ("syn\_keep").

The second method of handling the unused states is to cycle through them at

monitoring the parity of the state registers. Should you detect a parity error, you can reset the machine to its idle state or to another predetermined state.

With both of these methods, the state machine's outputs go to safe states and the state machine restarts from its idle position. State machines that use these methods can be said to be "SEU detecting," as they are capable of detecting and recovering from an SEU, although the state machines' oper-

#### XCELLENCE IN AEROSPACE & DEFENSE

ation will be interrupted. You must take care during synthesis to ensure that register replication does not result in registers with a high fanout being reproduced and hence left unaddressed by the detection scheme. Take care also to ensure that the error does not affect other state machines that this machine interacts with.

Many synthesis tools offer the option of implementing a "safe state machine" option. This option often includes more logic to detect the state machine entering an illegal state and send it back to a legal one normally the reset state. For a high-reliability application, design engineers can detect and verify these illegal state entries more easily by implementing any of the previously described methods. Using these approaches, the designers must also take into account what would happen should the detection logic suffer from an SEU. What effect would this have upon the reliability of the

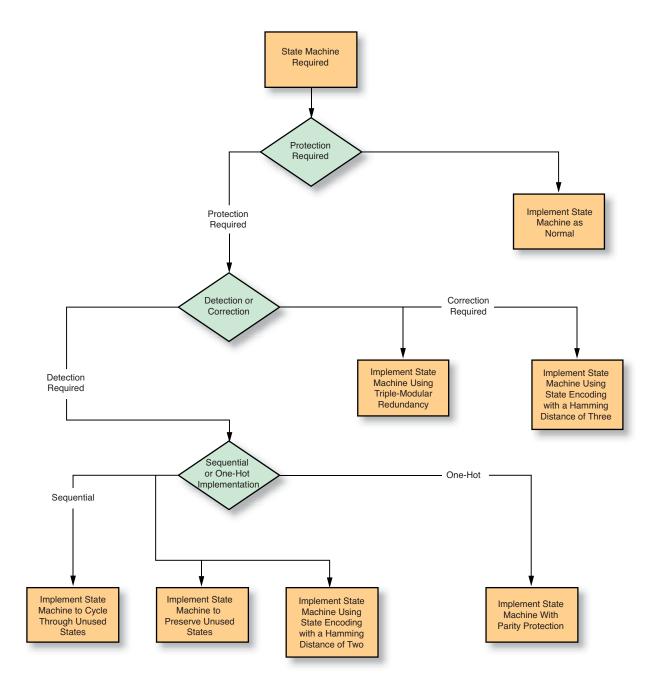

design? Figure 2 is a flow chart that attempts to map out the decision process for creating reliable state machines.

#### **Correction Schemes**

The techniques presented so far detect or prevent an incorrect change from one legal state to another legal state. Depending upon the end application, this could result in anything from a momentary system error to the complete loss of the mission.

Figure 2 – This flow chart maps out the decision process for creating reliable state machines.

Techniques for detecting and fixing incorrect legal transitions are triple-modular redundancy and Hamming encoding. The latter provides a Hamming distance of three and covers all possible adjacent states. A simpler technique for preventing legal transitions is the use of Hamming encoding with a Hamming distance of two (rather than three) between the states, and not covering the adjacent states. This, however, will increase the number of registers your design will require.

Triple-modular redundancy, for its part, involves implementing three instantiations of the state machine with majority voting upon the outputs and the next state. This is the simpler of the two approaches and many engineers have used it in a number of applications over the years. Typically, a TMR implementation will require spatial separation of the logic within the FPGA to ensure that an SEU does not corrupt more than one of the three instantiations. It is also important to remove any registers from the voter logic, since they can create a single-point failure in which an SEU could affect all three machines.

The use of a state machine with encoding that provides a Hamming distance of three between states will ensure both SEU detection and correction. This guarantees that more than a single bit will change between states, meaning an SEU cannot make the state transition from one legal state to another erroneously. The use of a Hamming distance of two between states is similar to the implementation for the sequential machine, where the unused states are addressed by the "when others" clause or reset cycling. However, as the states are explicitly declared to be separate from each other by a Hamming distance of two within the RTL, the state machine cannot move from one legal state to another erroneously and will instead go to its idle state should the machine enter an illegal state. This provides a more robust implementation than the binary one mentioned above.

If you wish to implement a state machine that will continue to function correctly should an SEU corrupt the current state register, you can do so by using a Hammingcode implementation with a Hamming

Fourth Quarter 2010

distance of three and ensuring its adjacent states are also addressed within the state machine. Adjacent states are those which are one bit different from the state register and hence achievable should an SEU occur. This use of states adjacent to the valid state to correct for the error will result in N\*(M+1) states, where N is the number of states and M is the number of bits within the state register. It's possible to make a small high-reliability state machine using this technique, but crafting a large one can be so complicated as to be prohibitive. The extra logic footprint associated with this approach could also result in lower timing performance.

#### **Deadlock and Other Issues**

There are other issues to consider when designing a high-reliability state machine beyond the state encoding schemes. Deadlock can occur when the state machine enters a state from which it is never able to leave. An example would be one state machine awaiting an input from a second state machine that has entered an illegal state and hence been reset to idle without generating the needed signal. To avoid deadlock, it is therefore good practice to provide timeout counters on critical state machines. Wherever possible, these counters should not be included inside the state machine but placed within a separate process that outputs a pulse when it reaches its terminal count. Be sure to write these counters in such a way as to make them reliable.

When checking that a counter has reached its terminal count, it is preferable to use the greater-than-or-equal-to operator, as opposed to just the equal-to operator. This is to prevent an SEU from occurring near the terminal count and hence no output being generated. You should declare integer counters to a power of two and, if you are using VHDL, they should also be modulo the power of two to ensure in simulation that they will wrap around as they will in the final implementation [ count <= (count + 1) Mod 16; for a 0- to 15-bit integer counter]. Unsigned counters do not require this, since there is no simulation mismatch between RTL and post-route simulation regarding wraparound.

You can replicate data paths within the design and compare outputs on a cycleby-cycle basis to detect whether one of them has been subjected to an SEU event. Wherever possible, edge-detect signals to enable the design to cope with inputs that are stuck high or stuck low. You should analyze each module within the design at design time to determine how it will react to stuck-high or stucklow inputs. This will ensure it is possible to detect these errors and that they cannot have an adverse effect upon the function of the module.

#### **Simulation and Verification**

Once you have designed the state machine, you will of course wish to simulate it to ensure it meets requirements. It is also possible during simulation to try to test how the machine will behave when subjected to an SEU (it is worth noting that this can take considerable time and effort to achieve in full). You can corrupt the state machine using the force option within the ModelSim utilities library from a test bench. When attempting to simulate the effects of SEUs, it is important to remember that they are asynchronous events that can occur at any point in time. There are also third-party tools available that can test designs for SEU performance. One free offering, which injects SEUs into the design, is the ESA Single Event Upsets Simulation Tool, available at http://www.nebrija.es/~jmaestro/esa/.

Designers can undertake a similar approach upon the post-route simulation. However, it's a better idea to verify the correct performance of the RTL code with regard to functionality and SEU tolerance and then conduct a formal equivalence check between the RTL and the postroute simulation netlist to ensure that they both behave in the same manner.

FPGAs will continue to be used in an increasing number of mission-critical applications as the growth in capability and performance demanded of these systems increases. The techniques presented here will provide you with the methodology required to make such a design a success.

# Virtex-4 FPGA Forms Foundation for Secure GSM Standards

Here are some design mechanisms and tips you can try when implementing current and future A5/x algorithms using Xilinx FPGAs.

by Mansoor Naseer Assistant Professor Bahria University, E-8, Islamabad, Pakistan mansoor.naseer@gmail.com

Mobile telephony, the Internet and streaming applications enable people to communicate over long distances and find information and entertainment online. But with the explosion in mobile communications usage, the tremendous volume of information transmitted in the air is vulnerable to security risks. In order to maintain security, engineers use cryptographic techniques to disguise the data. For the Global System for Mobile communication (GSM) standard, their algorithm of choice is the A5/1. Using A5/1, the encryption and decryption are performed over the network, both at the handset and at the base station.

This article will walk you through an implementation of the A5/1 stream cipher, taking note of the code snippets used to implement different blocks of the cipher. We will also take a look at a couple of new and different twists on the original A5/1 algorithm for enhanced security. In particular, I am changing how the feedback function behaves as well as reworking the combiner output. For this work, I used a Xilinx<sup>®</sup> Virtex<sup>®</sup>-4 LX series FPGA for hardware implementation and the Xilinx ISE<sup>®</sup> for synthesis. I used Mentor Graphics' ModelSim 6.0 for simulation.

Before plunging into implementation details, let us begin with a brief description of the A5/1 algorithm.

#### Ins and Outs of A5/1 Algorithm

In the GSM standard, information travels over the airwaves as sequences of frames. Frame sequences contain a digitized version of the user's voice as well as streaming audio and video data used in mobile Internet browsing. The system transmits each frame sequentially, 4.6 milliseconds apart. A frame consists of 228 bits; the first 114 bits are called "uplink data" and the next 114 bits are known as "downlink data."

We initialize A5/1 using a 64-bit secret key together with a known frame number that is 22 bits wide. The next step is to feed the input bits of the frame and secret key into three linear feedback shift registers (LFSRs) that are 19, 22 and 23 bits in size respectively. The feedback is provided after XOR'ing of selected taps, which helps increase randomness in the final output. I will call the three LFSRs R0, R1 and R2, such that each LFSR follows a primitive function. R0, R1 and R2 respectively use  $x^{19}+x^5+x^2+x+1$ ,  $x^{22}+x+1$  and  $x^{23}+x^{15}+x^2+x+1$  as their primitive functions.

The clocking sequences of LFSRs use a particular mechanism; otherwise, it would be very easy to decipher the output of LFSRs. Therefore, clocking is based on a majority rule. This rule uses one tap each from R0, R1 and R2, and determines whether the taps are mainly 0 or 1. That is, two or more taps with a value of 0 imply a majority value 0; otherwise, it is 1. Once the majority is established, clock the LFSRs if their input bit matches the majority bit. If the input bit does not match the majority value, no input bit will be inserted in the LFSR and hence, no shifting will take place. Additionally, we get the output by XOR'ing each output bit of R0, R1 and R2 in the original A5/1. In this work, I have replaced the standard XOR'ing with a more sophisticated output-generating function that we call a "combiner."

The key setup routine of the A5/1 algorithm is as follows:

- 1. Initialize R0, R1 and R2 with 0.

- 2. Load the value of session key KC and frame Fn into the LFSRs, one after the

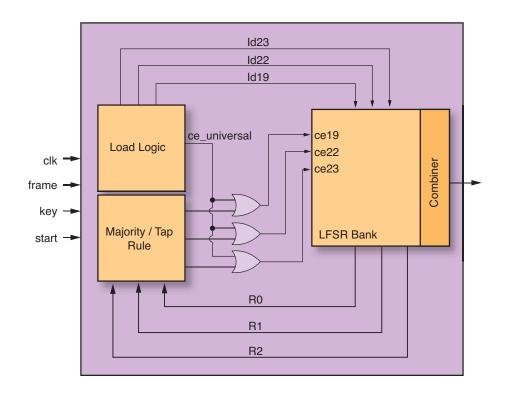

Figure 1 – Architectural diagram of the top module

other. The session key KC takes 64 cycles in loading whereas Fn takes another 22 cycles. In every cycle, the input bit is XOR'ed with a linear feedback value coming from selective taps.

- 3. Next, allow the LFSRs to clock for 100 cycles, a process called mixing. Linear feedback is active and so are the chip enables, allowing a shift/noshift that is also active.

- 4. After the mixing step is complete, the next 228 cycles result in the final output key stream. The uplink and downlink streams (each consisting of 114 bits) are used for decryption and encryption operations. This step employs nonlinear feedback and a modified combiner as against the traditional A5/1 algorithm defined above.

- 5. You can repeat the previous steps for every new frame Fn. The frame numbers are updated where the session key remains unchanged until authentication protocols provoke it.

#### **Hardware Implementation**

I did the hardware implementation of the proposed algorithm on Xilinx Virtex-4 series FPGAs. Because we designed the implementation logic for compactness, I targeted the smallest device in the Virtex-4 family, namely the XC4VLX15. Figure 1 shows the overall architecture of the top-level module.

The top level comprises two building blocks and glue logic. I designed the glue logic to provide chip connectivity, start logic and data-loading features. There are two other building blocks, Majority/Tap rule and LFSR bank, each with its own unique functions.

The Majority/Tap rule block receives the selective tap positions from the LFSR bank and performs two separate functions independently. As the selection criteria for Majority or Tap rule are based on the last tap of R0, R1 and R2, the logic for Majority rule and Tap rule is implemented in parallel. I also performed one other optimization in the implementation of Majority rule. The pseudo algorithm for selecting majorities is described as: If (R0[13] + R1[12] + R2[16])

>= 2 then maj1 = 1

else then maj1 = 0

Similarly, we find the value of maj2 based on tap numbers 7, 5 and 8. Based on these majority functions, we define the chip enable for R0 as:

# If (R0[13]== maj1) AND (R0[7] == maj2) then chip enable for Majority rule is 1 else 0.

I implemented the pseudo code for selecting maj1 and maj2 in the form of simple and/or gates. Similarly, the pseudo code for chip enables maps onto a simple XNOR function, combining all the logic and reducing area.

The technique implements the Tap rule algorithm using case statements. The original A5/1 algorithm determines the shift operation or chip enable for LFSRs based on the majority rule only. As I have introduced a modified Majority rule and an additional Tap rule for shifting LFSRs, I needed another mechanism. Thus, make the final selection of chip enables for R0, R1 and R2 based on the PoliSel signal, which determines whether to output the chip enable signal established by Majority or Tap rule. The PoliSel signal implements this equation: PoliSel = R0[18] XOR R1[21] XOR R2[22].

#### The LFSR Bank

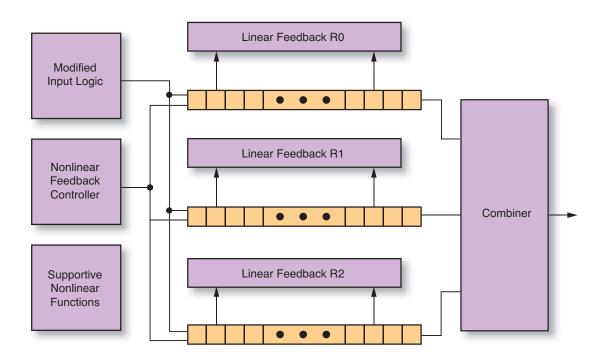

The LFSR bank module houses multiple functions and implementations. This module instantiates a core LFSR with varying parameters for establishing R0, R1 and R2 LFSRs. The width of these LFSRs is 19, 22 and 23 respectively. This module also instantiates an improved linear feedback function from A5/1. Additionally, the LFSR bank implements our novel nonlinear feedback logic. I also implemented in this block the combiner that produces the final output. Figure 2 shows the block diagram for the LFSR bank. Here, the LFSRs are serial-in, parallel-out shift registers. Xilinx Virtex-4 devices allow convenient mapping of these shift registers onto hardware. Using the standard template for LFSRs as shown below, we can infer generic serial registers.

```

module lsr (clk, ce, si, po);

width = 18;

parameter

clk, ce, si;

input

output

[width-1:0]

po;

[width-1:0] shftreg = 0;

rea

always @ (posedge clk)

begin

if (ce) shftreq <=

{shftreg[width-2:0], si};

end

assign po = shftreg;

endmodule

```

With the use of parameters, it becomes easy to instantiate LFSRs at the higher level. By passing the parameters using the "defparam" feature of Verilog, we can infer the required LFSRs of width 19, 22 and 23 bits at the top level. The inference is conveniently done by using the following lines of code:

lsr lfsr19bit (clk, ce19, si19, lfsr19); defparam lfsr19bit.width = 19;

Figure 2 – Logic blocks at the input and output of R0, R1 and R2 in LFSR bank module

Figure 3 – Nonlinear feedback controller and input selection values

(The latter controls the parameter width inside instance lsr.)

As seen from the following code snippet, the input loading path of the LFSRs is welldefined in terms of simple XOR operations.

```

wire frameXor19, keyXor19, si19input;

assign frameXor19 = frame ^ si191fb;

assign keyXor19 = key ^ si191fb;

assign si19input = (frameXor19 ^

keyXor19) ? frameXor19:keyXor19;

```

The existence of asynchronous gates increases the length of the critical path. However, here it is well within tolerable limits, as the critical path in the current case consists of only three XORs and one multiplexer.

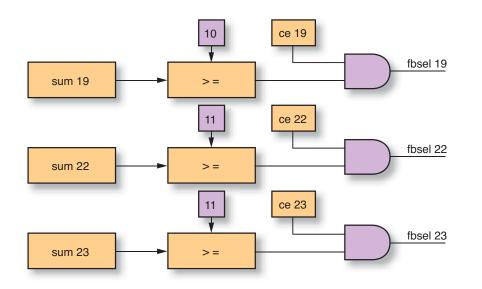

After loading is completed, the feedback path chooses between either linear or nonlinear feedback. The nonlinear feedback controller makes this selection decision. A choice of nonlinear feedback suddenly changes the design specifications and parameters. For instance, the nonlinear feedback function is activated periodically every 11 clock cycles and remains active for 10 clock cycles. To keep the implementation area small, we have implemented counters rather than adders to enforce the periodic behavior of the nonlinear feedback function. The implementation requires separate counters for R0, R1 and R2 for counting the number of 1's. The pseudo algorithm for this implementation is as follows:

- 1. Detect falling edge on ldlfsr signal.

- 2. Start counting for 100 cycles.

- 3. After 100 cycles, for every 10 cycles activate the stream breaker, then deactivate for 10 cycles until 114 clocks elapse.

Stream breaker pseudo code:

- 4. Sum the contents of lfsr 19, 22, 23.5. If count19 > 10, count22 > 11 or

- count23 > 11

- 6. pass 1 into the LFSR

- 7. else

- 8. pass 0 into the LFSR.

Since the decision of inserting 1's or 0's in the input of R0, R1 and R2 needs to be taken every clock cycle, once the nonlinear feedback is activated, the number of counters and adders significantly increases in area and critical path.

The combination of chip enable and input causes the nonlinear feedback path to assume 0 or 1 based on the algorithm of the stream breaker. Figure 3 shows a hardware building block implementing this scheme.

Using counters with defined thresholds assists the implementation of the nonlinear feedback controller. Do not allow the counter to decrement after approaching 0 or to increment after reaching the high value corresponding to R0, R1 and R2, namely 19, 22 and 23 respectively. The following code snippet provides one example implementation of the counter:

```

reg [4:0]

sum19=5'd0;

wire

inc sum19, dec sum19;

assign

inc sum19 = si19 & ce19;

assign dec_sum19 = lfsr19[18] & ce19;

always @ (posedge clk)

begin

case ({inc sum19, dec sum19})

2'b01:

begin

if (sum19 == 5'd0) sum19 <= 5'd0;

else

sum19<=sum19-1:

end

2'b10:

begin

if (sum19 == 5'd18) sum19<=5'd18;

sum19<=sum19+1;

else

end

default: sum19 <= sum19;</pre>

endcase

end

```

This code also shows how the increment and decrement functions are dependent on chip enable signals and not just the value at the input of LFSR on every rising edge of the clock.

It is extremely important to implement tight and secure encryption algorithms for future mobile communication standards. As the bandwidth requirements are rapidly evolving and streamingdata volume is on an exponential rise, it is all the more necessary to be able to implement vary fast and parallel ciphers for data security. A Xilinx Virtex-4 device offers the perfect solution for parallelism, high speed and bandwidth requirements in this application. With low-voltage operations and ultralow power consumption, this platform can easily adapt to the upcoming secure mobile applications. With the small tricks and snippets of code presented here, you can easily map the A5/1 and its future variants onto Xilinx FPGAs. 🔹

XCELLENCE IN NETWORKING

# FPGA Research Design Platform Fuels Network Advances

Xilinx and Stanford University are teaming up to create an FPGA-based reference board and open-source IP repository to seed innovation in the networking space.

> by Michaela Blott Senior Research Engineer Xilinx, Inc. mblott@xilinx.com

Jonathan Ellithorpe PhD Candidate Stanford University

Nick McKeown Professor of Electrical Engineering and Computer Science Stanford University

Kees Vissers Distinguished Engineer Xilinx, Inc.

Hongyi Zeng PhD Candidate Stanford University

Stanford University, together with Xilinx Research Labs, is building a second-generation high-speed networking design platform called the NetFPGA-10G specifically for the research community. The new platform, which is poised for completion this year, uses state-of-the art technology to help researchers quickly build fast, complex prototypes that will solve the next crop of technological problems in the networking domain. As with the first-generation platform, which universities worldwide have eagerly adopted, we hope the new platform will spawn an open-source community that contributes and shares intellectual property, thus accelerating innovation.

# An open-source hardware repository facilitates the sharing of software, IP and design experiences, promoting technological solutions to the next generation of networking problems.

This basic platform will provide everything necessary to get end users off the ground faster, while the open-source community will allow researchers to leverage each other's work. The combination effectively reduces the time spent on the actual implementation of ideas to a minimum, allowing designers to focus their efforts on the creative aspects.

In 2007, we designed the first-generation board, dubbed NetFPGA-1G, around a Xilinx<sup>®</sup> Virtex<sup>®</sup>-II Pro 50, primarily to teach engineering and computer science students about networking hardware. Many EE and CS graduates go on to develop networking products, and we wanted to give them hands-on experience building hardware that runs at line rate, uses an industry-standard design flow and can be placed into an operational network. For these purposes, the original board had to be low in cost. And with generous donations from several semiconductor suppliers, we were able to bring the design in at an end price of under \$500. As a result, universities were quick to adopt the board and today about 2,000 NetFPGA-1Gs are in use at 150 schools worldwide.

But the NetFPGA very quickly became more than a teaching vehicle. Increasingly, the research community began to use it too, for experiments and prototypes. For this purpose, the NetFPGA team provided free, open-source reference designs and maintains a repository of about 50 contributed designs. We support new users, run online forums and offer tutorials, summer camps and developers' workshops.

#### Trend Toward Programmability

For more than a decade, networking technology has trended toward more-programmable forwarding paths in switches, routers and other products. This is largely because networking hardware has become more complicated, thanks to the advent of more tunneling formats, quality-of-service schemes, firewall filters, encryption techniques and so on. Coupled with quickly changing standards, those factors have made it desirable to build in programmability, for example using NPUs or FPGAs.

Researchers often want to change some or all of the forwarding pipeline. Recently, there has been lots of interest in entirely new forwarding models, such as OpenFlow. Researchers can try out new network architectures at the national scale at national testbeds like GENI in the United States (*http://geni.net*) and FIRE in the EU (*http://cordis.europa.eu/fp7/ict/ fire/calls\_en.html*).

Increasingly, researchers are embracing the NetFPGA board as a way to prototype new ideas—new forwarding paradigms, scheduling and lookup algorithms, and new deep-packet inspectors—in hardware. One of the most popular reference designs in the NetFPGA canon is a fully functional open-source OpenFlow switch, allowing researchers to play with variations on the standard. Another popular reference design accelerates the built-in routing functions of the host computer by mirroring the kernel routing table in hardware and forwarding all packets at line rate.

#### NetFPGA, Take Two

For the second-generation platform, the so-called NetFPGA-10G, we have expanded our original design goals to also include ease of use, with the aim of supplying end customers with a basic infrastructure that will simplify their design experience. This goal is closely aligned with the objective of Xilinx's mainstream Targeted Design Platforms, which provide users with tools, IP and reference designs in addition to FPGA silicon so as to speed up the design process.

To realize this vision, we will deliver a board with matching FPGA infrastructure design in the form of both basic and domain-specific IP building blocks to increase ease of use and accelerate development time. We further will develop reference designs, such as a network interface card and an IPv4 reference router, as well as basic infrastructure that assists with building, simulating and debugging designs. The idea is to allow users to truly focus their development time on their particular area of expertise or interest without having to worry about low-level hardware details.

Unlike the mainstream Targeted Design Platforms, our networking platform targets a different end-user group, namely, the larger research community, both academic and commercial. Semiconductor partners are heavily subsidizing this project to assist in the effort to keep the board cost to an absolute minimum so as to encourage broad uptake. Not only Xilinx but other key component manufacturers such as Micron, Cypress Semiconductor and NetLogic Microsystems are donating parts for the academic end user. (Commercial researchers will pay a higher price.)

Part of the project's strength is the fact that this platform is accompanied by a community as well as an open-source hardware repository that facilitates the sharing of software, IP and experiences beyond the initial base package. The result is an ever-growing IP library that we hope will eventually encompass a wide range of reference components, networking IP, software and sophisticated infrastructure thanks to contributions from many well-known universities, research groups and companies. We hope that by providing a carefully designed framework, some lightweight coordination to share expertise and IP

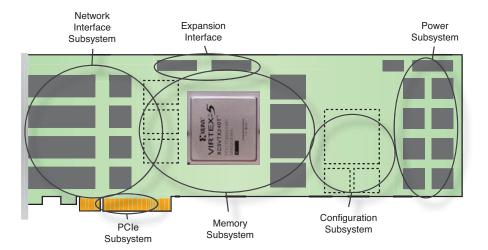

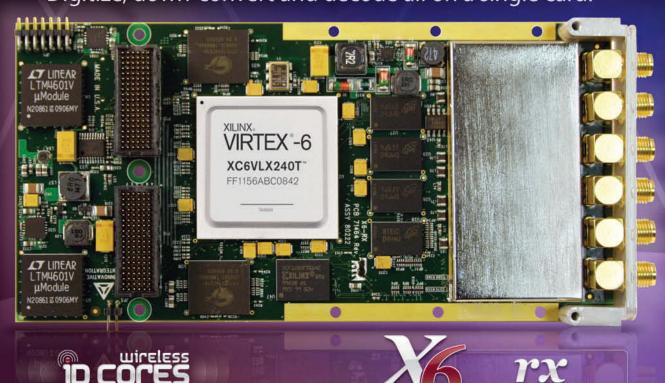

Figure 1 – The NetFPGA-10G board is built around a Virtex-5 FPGA.

in a systematic way, and a well-designed plug-and-play architecture with standardized interfaces, the open-source hardware repository will grow, promoting technological solutions to the next generation of networking problems.

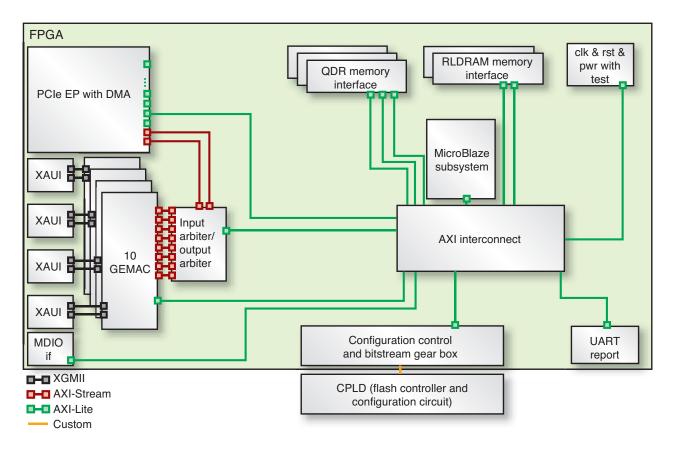

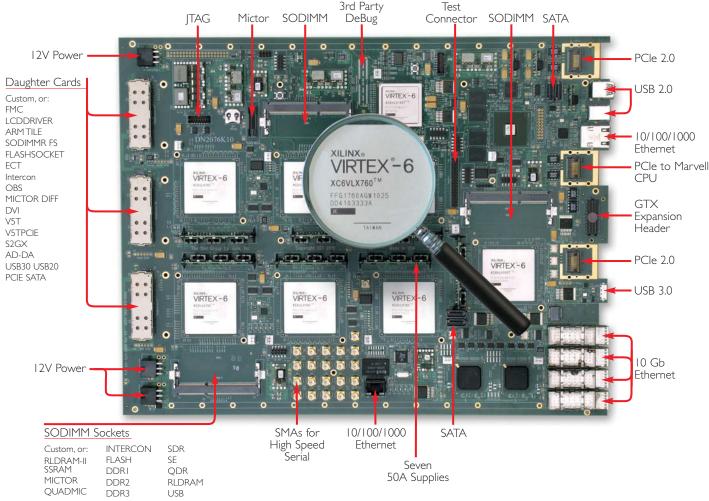

The NetFPGA-10G is a 40-Gbit/second PCI Express<sup>®</sup> adapter card with a large FPGA fabric that could support as many through which the network traffic enters the FPGA. The memory subsystem, for its part, consists of several QDRII and RLDRAMII components. The majority of the I/Os are used for this interface, to maximize the available off-chip bandwidth for functionality such as routing tables or packet buffering. The FPGA also interfaces to the PCIe subsystem.

Figure 2 – The board connects to five subsystems: network interface, PCIe, expansion, memory, configuration and power.

applications as possible. As shown in Figure 1, the board design revolves around a large-scale Xilinx FPGA, namely a Virtex-5 XC5VTX240T-2 device [1].

The FPGA interfaces to five subsystems (see Figure 2). The first of these, the network interface subsystem, hosts four 10-Gbps Ethernet interfaces with PHY devices The fourth subsystem is an expansion interface designed to host a daughter card or to communicate with another board. For that purpose we brought all remaining highspeed serial I/O connections out to two high-speed connectors. Finally, the fifth subsystem is concerned with the configuration of the FPGA. Overall, the board is implemented as a dual-slot, full-size PCIe<sup>®</sup> adapter. Two slots are required for reasons of heat/power and height. Like high-end graphics cards, this board needs to be fed with an additional ATX power supply, since power consumption—given absolute maximum load on the FPGA—could exceed the PCIe singleslot allowance of 50 watts. However, the board can also operate standalone outside a server environment.

#### **Memory Subsystem**

A central focus in our design process was the interface to SRAM and DRAM components. Since the total number of I/Os on the FPGA device limits the overall available off-chip bandwidth, we had to strike a carefully considered compromise to facilitate as many applications as possible. Trying to support applications ranging from network monitoring through security and routing to traffic management imposes greatly varying constraints.

In regard to external memory access, for example, a network monitor would require a large, flow-based statistics table and most likely a flow classification lookup. Both accesses would require short latencies, as the flow classification needs more than one lookup with intradependencies, and the update in a flow statistics table would typically encompass a readmodify-write cycle. Hence, SRAM would be an appropriate device selection. However, a traffic manager would mainly need a large amount of memory for packet buffering, typically implemented through DRAM components due to density requirements. As a final example, consider an IPv4 router that needed a routing-table lookup as well as packet buffering in respect to external memory.

Summing up the requirements from a range of applications, we realized that certain functionality would consume external memory bandwidth, whether it be SRAM or DRAM. Where packet buffering (requiring a large storage space) would point to DRAM, SRAM would be the choice for flow classification search access, routingtable lookup, flow-based data table for statistics or rule-based firewall, memory management tables for packet buffer implementations and header queues.

All of this functionality needs to be carried out on a per-packet basis. Therefore, given the worst case of minimum-size packets of 64 bytes with 20 bytes of overhead, the system needs to service a packet rate of roughly 60 Megapackets per second. Second, we need to differentiate the accesses further. To begin with, many memory components such as QDR SRAM and RLDRAM SIO devices have separate read and write data buses. Since the access patterns cannot be assumed to be symmetrirefined our requirements further as seen in Table 1.

Assuming a clock speed of 300 MHz on the interface, a QDRII interface can service 2\*300 = 600 million accesses/second for read and for write operations. Hence, three QDRII x36-bit interfaces could fulfill all of our requirements.

In regard to DRAM access, we considered mainly the case of packet storage, where each packet is written and read once from memory. This translates into a data access bandwidth of roughly 62 Gbps once you have removed the packet overhead Compared with other 10G transceiver standards such as XENPAK and XFP, SFP+ has significant advantages in terms of power consumption and size. With SFP+ cages, we can support a number of interface standards, including 10GBase-LR, 10GBase-SR, 10GBase-LRM and low-cost direct-attach SFP+ copper cable (Twinax). Furthermore, SFP modules for 1-Gbps operation can be utilized, thereby supporting the 1000Base-T or 1000Base-X physical standards as well.

Each of the four SFP+ cages connects to a NetLogic AEL2005 device via the SFI

|                                            | Data width<br>(bits) | #Reads<br>per packet | #Writes<br>per packet | #Reads<br>per x36 interface | #Writes<br>per x36 interface |

|--------------------------------------------|----------------------|----------------------|-----------------------|-----------------------------|------------------------------|

| Flow classification (5tupel + return key)  | 144                  | 2                    | 0                     | 8                           | 0                            |

| Routing-table lookup (dip + next hop)      | 96                   | 2                    | 0                     | 6                           | 0                            |

| Flow-based information                     | 128                  | 2                    | 0                     | 8                           | 0                            |

| Packet buffer memory management            | 32                   | 2                    | 2                     | 2                           | 2                            |

| Header queues                              | 32                   | 1                    | 1                     | 1                           | 1                            |

| Total number of accesses                   |                      |                      |                       | 25                          | 3                            |

| Total number of accesses per second (MAps) |                      |                      |                       | 1,500                       | 180                          |

#### Table 1 – SRAM bandwidth requirements

cally distributed, we cannot pool the overall access bandwidth, but must consider the operations individually.

What's more, there is a third type of access, namely "searches." Searches can be ideally implemented through TCAMbased devices, which give guaranteed answers with fixed latencies. However, we ruled out this type of device for our board for price and power reasons, along with the fact that TCAMs further constrain the use of the I/O. Searches can also be implemented in many other ways such as decision trees, hash algorithms and decomposition approaches, with or without caching techniques, to name a few [2]. For the purpose of this discussion, we assumed that a search can be approximated through two read accesses on average. Given these facts and making some common assumptions on data widths, we from the originally incoming 2\*40 Gbps. In terms of physical resources, an RLDRAMII access can probably achieve an efficiency of around 97 percent, whereas DDR2 or DDR3 devices would more likely come in at around 40 percent [3], hence requiring significantly more I/O. We therefore chose RLDRAMII or CIO components. Two 64-bit RLDRAMII interfaces at 300 MHz deliver a combined bandwidth that is roughly enough to service the requirement.

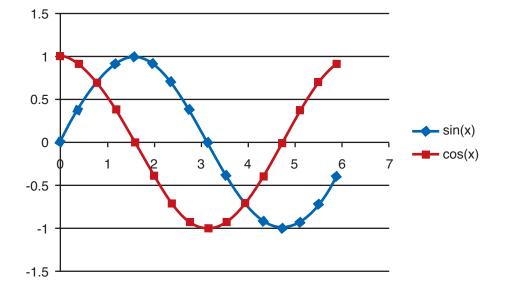

#### **Network Interface**