## DATAPOINT CORPORATION

Product Specification

#### 1.0 General Description

The 9426 Channel Adapter interfaces with an IBM System 360/370 by emulating with hardware and software certain IBM I/O devices found on a byte multiplexor channel -- most commonly unit record devices such as card readers, card punches, and line printers.

The Adapter is compatible with the Datapoint 5500 and 6600 I/O busses. It has 4K of data buffers, organized into 16 pages of 256 bytes per page, plus control memory consisting of 16 pages or buffers of 16 bytes each. A microprocessor controls all data transfer and IBM I/O interface activity; firmware resides in a PROM.

The Adapter monitors IBM Channel sequences and steps the microprocessor through them.

The Channel Adapter is used as part of three different but similar Datapoint software products: DASP<sup>™</sup>, DCIO, and MLCI.

DASP -- Datapoint Attached Support Processor -- is a combination hardware and software product used in conjunction with the Channel Adapter to enable Batch Telecommunications with an IBM System 360, Model 30 (equivalent or above) mainframe. A description of this system product is given in the DASP Product Specification, Document no. 60673.

DCIO -- Direct Channel Interface Option -- is a combined hardware/software product used in conjunction with the Channel Adapter to enable an IBM mainframe to access the resources of a Datapoint ARC<sup>TM</sup> system in a manner analogous to that of a Datapoint Attached Processor. This system product is described in the DCIO Product Specification, Document no. 60674.

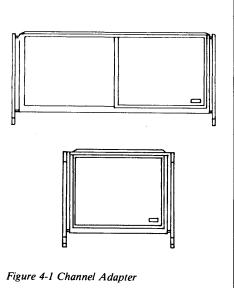

The 9426 Channel Adapter (also available in a console mount.)

# Channel Adapter 9426

August 7, 1979 Document no. 60829

Copyright© 1979 by Datapoint Corporation. Printed in U.S.A.

The "D" Logo and Datapoint are trademarks of Datapoint Corporation, registered in the U.S. Patent Office.

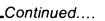

### 3.1.1 Interface I Logic Card

The Interface I Logic Card provides the necessary logic to implement a standard Datapoint I/O interface. It is compatible with the Datapoint 5500 and 6600 I/O Busses. In addition to providing an interface for the Adapter it furnishes the Adapter a built-in Channel sequence Simulator (for test purposes) controlled from the connecting Datapoint Processor.

3.1.2 Interface II Logic Card

The Interface II Logic Card contains the necessary line drivers and receivers for the IBM I/O interface as well as the Power On/Power Off sequence relays. Other major components on the card include the Select Out/Hold Out latch, the Select Out propagation circuitry, and the Power On Reset (POR) circuitry for the Channel Adapter.

3.1.3 Memory Logic Card

The Memory Card provides 4K (4096) bytes of data buffers organized into 16 pages of 256 bytes each, as well as a 64 byte deep Activity queue (a First-In, First-Out memory) and control buffers organized in 16 pages of 16 bytes. It also contains the control logic necessary to provide dual port access (between the microprocessor and the Datapoint 5500/6600) to both the Control and Data Buffers.

#### 3.1.4 Microprocessor Card

The microprocessor and microprogram are the major control components of the Adapter. Through the microprocessor, the microprogram (which resides in the PROM on the card) controls and monitors all data transmissions and IBM I/O interface activity, except for the Control Unit Busy Sequence.

#### 3.1.5 Sequencer Card

The Sequencer Card monitors the IBM Channel sequences and steps the

MLCI -- MULTILINK<sup>™</sup> Channel Interface -- a software product used in conjunction with the Channel Adapter to enable ON-LINE interactive inquiry into the database of an IBM System 360/370 from terminals of a Datapoint DATASHARE<sup>®</sup> system. The MLCI Product Specification, Document no. 60641, describes this system product.

The software component of each of these systems executes in a Datapoint processor connected to the 9426/9427 Channel Adapter. This controlling software is referred to hereafter as the Datapoint processor software program, or software driver.

## 2.0 System Requirements

The Channel Adapter is compatible with the Datapoint 5500 and 6600 I/O interfaces. On the IBM side, the Adapter will be connected to the Byte Multiplexor Channel.

#### 3.0 Technical Description

### 3.1 Channel Adapter Components

The Adapter consists of the following major components:

-Interface I Logic Card (Datapoint Interface and Control Logic

-Memory Logic Card (Control and Data Buffers)

-Microprocessor Logic Card

-Sequencer Logic Card (IBM I/O Interface Control)

-Interface II (IBM compatible Drivers and Receivers)

-Power Supply

(See figure 3-1 for a block diagram of the Adapter.)

microprocessor through them. It also provides address decoding logic for the IBM Channel Interface, and logic for the short Control Unit Busy sequence.

## 3.1.6 Power Supply

The power supply, a switching regulator type similar to the Version III power supply in the Datapoint 6600 processor, is contained in a module located at the rear of the unit. It provides all necessary logic power for Adapter operaton, and the power interlock circuitry.

### 3.2 Operation and Programming Definitions

The Datapoint Channel Adapter together with its associated Datapoint processor and software performs the function of an IBM System 360/370 control unit, accomplishing data transfer through emulation. The devices it emulates may vary with software changes, but the most common ones are unit record type I/O devices (Card Readers, Card Punches, and Line Printers).

The Datapoint hardware and software can also emulate an IBM 1052 Printer-Keyboard, using the Datapoint processor's CRT and keyboard for control of the System 360/370.

## 3.2.1 Structure of IBM Control Units

Nearly all I/O devices which attach to an IBM System 360/370 do so through a control unit, which may be integrated into the device or be a separate, stand-alone item. Such control units are attached to the Channel through a standard I/O interface: a group of connecting lines that carry data and control information between the control unit and the Channel, which is a device that controls the transmission of data between the IBM Central Processing Unit and the I/O devices, or from these components to main storage.

## 3.2.2 Control of the Channel Adapter

Control of the Adapter relies upon a very few external switches and indicators. Most operational control is done by the software program in the Datapoint processor. The user does not need to know how the software program works in order to make it perform.

He need know only how to instruct it, by entering responses at the processor keyboard to questions displayed on the processor screen, to carry out certain built-in functions.

For example, many different devices may be emulated merely by changing selected parameters of the software control program.

# 3.2.3 Operator Controls and Indicators

Operator controls consist of three switches and three indicators located on both the front and rear panels of the Adapter.

Front panel controls are as follows:

- On Indicator Light

- On-Line Indicator Light

- Operate Indicator Light

- Controlled Power On/Off Switch

ON Indicator-The ON indicator lights when power has been applied. The following conditions must be met before this indicator will light or the Channel Adapter will work:

Both the Main Power On/Off switch and the Controlled Power On/Off Switch must be in their "on" positions and the Adapter must sense the +12VDC I/O power available from the connecting Datapoint processor -- which means the processor must also be "on" and its I/O cable connected to the Adapter. The operate/test switch should be in the operate position.

ON-LINE Indicator-The ON-LINE Indicator lights when the Adapter is brought "on-line" to either the IBM System 360/370 Channel or the built-in Channel Simulator. It does not light when the Adapter is "off-line" to either the Channel or the Simulator.

OPERATE Indicator-The Operate indicator

#### Continued...

lights when the Adapter is in the "Operate" mode.

CONTROLLED POWER ON/OFF SWITCH-

A double-throw switch is used to apply power to the Adapter. The switch will apply power only

• when it is moved to its "on" position

• the connecting Datapoint processor is also powered on

Adapter Main Power On/Off Switch is "on," and AC Power present at the Adapter

Note that the Datapoint processor must be powered up before the Adapter is powered up.

Once turned on, the Controlled Power On/Off switch is only active when the following conditions have been met:

• The Adapter is not ON-LINE to either the IBM System 360/370 Channel or to the built-in Simulator.

In other words, when the Adapter is ON-LINE to the Channel or the Simulator, the Controlled Power On/Off Switch cannot be operated. (Note that moving the switch from its "on" to its "off" position while the ON-LINE indicator is lit will not result in powering down the Adapter. The Controlled Power On/Off Switch may, however, be over-ridden by the Main Power On/Off switch (located at the rear of the Adapter) during emergencies.

Rear panel controls consist of two switches:

- Main Power On/Off Switch

- Operate/Test Switch

Main Power ON/OFF Switch-Controls the main AC power into the Adapter and is the main AC circuit breaker, rated at 5.0 AMP. It is independent of all interlocks and, when thrown open, immediately cuts AC power to the Adapter.

Normally this switch should not be used to power off the Adapter, as it may cause disturbances to the System 360/370 I/O interface. However, it should be in the Off position whenever the Adapter is to be serviced.

Should an overload condition open the circuit breaker, always have qualified maintenance personnel investigate and correct the cause of the overload before resetting the circuit breaker by moving the switch to the "ON" position. Otherwise, the same condition may open the breaker again, with possibly disastrous results.

OPERATE/TEST Switch-This switch is used to control the operating mode of the Adapter when it is brought ON-LINE. It should be set

## Channel Adapter 9426

to the Operate position except when the Adapter is being serviced by field maintenance personnel. With the Operate/Test switch in Test position, the Adapter will be brought up ON-LINE to the built-in Simulator; it cannot be brought on-line to the host multiplexor Channel. However, once the Adapter is brought ON-LINE by the driver software, the mode of operation will not be changed by moving the switch. The Operate/Test Switch is only effective when the Adapter is OFF- Line to both the Channel and the built-in Simulator.

## 3.2.4 Datapoint Software Control Definitions

This section sets forth all control sequences, status, and command formats which may be issued by the Datapoint processor to the Channel Adapter.

#### 3.2.4.1 EX ADR

The Adapter is addressed by executing an EX ADR instruction with the correct device address in the processor's A register. The factory-strapped address is an octal 0215. (This address may be changed in the field by modifying the address strapping on the Interface I Logic Card.)

Executing an EX ADR sets status bit 0 of the Adapter status byte and places the Adapter in the status mode.

#### 3.2.4.2 Status Byte

Execution of either an EX ADR or an EX STATUS instruction makes the Adapter status byte in the Status Register available to the software during the subsequent execution of an INPUT instruction. Either an EX ADR or an EX STATUS places the Adapter into its Status mode.

Care should be taken when examining the contents of the Adapter status register because it is only updated after an EX ADR, EX STATUS, or INPUT instruction is executed. To be certain that the current status is being accessed, use an EX STATUS instruction

immediately before an INPUT instruction.

The Adapter status byte has the following format and bit definitions:

#### **B**it

0 - .....Adapter Addressed 1 - .....ON-LINE & Configured 2 - .....Address Available 0 = FIFO Buffer Empty 1 = FIFO Buffer Full 3 - .....Adapter BUSY 4 - .....System RESET 5 - .....Illegal Operation 6 - .....Status Modifier 7 - .....Reserved

Bit 0 - Adapter Address - This bit is a logical 1 whenever the Adapter is addressed by the Datapoint processor.

Bit 1 - On-Line and Configured - This bit is a logical 1 whenever the Adapter is ON-LINE. It is a software duplication of the ON-LINE indicator located on the Adapter's front panel. This bit will remain on until the Adapter has gone OFF-LINE, following an OFF- LINE EX COM1 instruction.

Bit 2 - Address Available - This bit is a logical 1 whenever the Adapter has placed a Logical Buffer Address into the Activity FIFO memory. It remains on until the contents of the FIFO memory have been exhausted by the driver software. That is, the bit is off whenever the FIFO memory is empty.

Bit 3 - Adapter Busy - This bit is a logical 1 whenever the Adapter cannot execute or is executing the previous EX COM1 instruction. It is turned on upon receipt of an EX COM1, and is not reset until the Adapter has either completed execution of the EX COM1 or acknowledged receipt of the EX COM1. (See definitions of EX COM1 instruction.) The driver software should not attempt to execute another EX COM1 instruction until this bit is reset.

Bit 4 - System Reset Received This bit is set upon receipt by the Adapter from the IBM Channel of a System Reset. It is reset when a

## \_Continued....

System Clear is executed by the Adapter in response to a System Clear EX COM1 instruction.

Bit 5 - Illegal Operation on Last EX COM1 This bit is set whenever the last received EX COM1 instruction was detected as an invalid command. It is reset upon receipt of the next valid EX COM1 instruction,

Bit 6 - Status Modifier - This bit is set when the last received EX COM1 instruction was a New Sequence EX COM1, and was detected as an invalid instruction. It is reset upon receipt of the next valid EX COM1 instruction.

## 3.2.4.3 EX COM1

An EX COM1 instruction is the means whereby the driver software responds to Adapter requests for service, or issues instructions to the Adapter. When an EX COM1 instruction is executed by the Datapoint processor, the contents of its A-register are loaded into the COM1 register on the Interface I logic card. In addition, the contents of the COM3 register are loaded into the Auxiliary Logical Address register on the Interface I logic card. Execution of an EX COM1 sets status bit 3. An EX COM1 should not be executed while status bit 3 is set.

The EX COM1 instruction byte has the following bit definitions:

0 - ......Master Clear

1 - .....Configure System

2 - .....System Clear

3 - .....On-Line

4 - .....Off-Line

5 - .....Initiate Sequence

6 - ....Send Asynchronous Status

7 - ....Reserved

Bit 0 - Master Clear - If set True, this resets the sixteen control buffers and the active address RAM to zero. It also clears the Activity FIFO memory and the status register. Upon execution of the Master Clear EX COM1, the Busy bit (bit 3 of status register) will be set until the Adapter has completed execution of the Master Clear.

Bit 1 - Configure System - This commands the microprogram to configure the active address RAM for ON-LINE operation. The microprogram scans the control buffers for a Active Bit being set, indicating that the control

buffer is to be an active logical buffer and that byte zero of the buffer contains the Channel Address to be used in configuring the active address RAM. Both the Active Bit and the Channel Address must be set up in the control buffers by the software before issuing the Configure System command. The Busy bit (status bit 3) is set until the Adapter acknowledges receipt of the command.

Bit 2 - System Clear - This resets the sixteen control buffers, except byte zero and the Active bit of byte seven. It also clears the Activity FIFO memory and the status register. A System Clear instruction should only be issued to the Adapter in response to a System Reset indication when the Adapter is ON-LINE. The Busy bit is set until the Adapter acknowledges receipt of the command.

Bit 3 - On-Line - Setting this bit True commands the Adapter to go ON-LINE to either the IBM Channel or the built-in Simulator -depending on the position of the OPERATE/TEST switch. The ON-LINE EX COM1 instruction should only be issued to the Adapter when bit 1 of the status byte is not set -- that is, the Adapter is OFF-LINE. The busy bit (status bit 3) is set until the Adapter has successfully gone ON-LINE to either the IBM Channel or the built-in Simulator.

Note, however, that this will not happen until a SYSTEM/WAIT transition occurs.

Bit 4 - Off-Line - Setting this bit True commands the Adapter to go OFF- LINE to either the IBM Channel or the built-in Simulator -depending on the position of the OPERATE/TEST switch. An Off-Line EX COM1 instruction should only be issued when the Adapter is in the ON-LINE state (Status bit 1 is set). The Busy bit (status bit 3) is set upon receipt of the command and remains set until the Adapter has acknowledged receipt of the instruction. Note that this command may not result in immediate execution, depending upon the current state of the Adapter. The Adapter must be completely idle before its microprogram will allow it to go off-line.

If an OFF-LINE EX COM1 is issued when the Adapter is not in an idle state, the microprogram will "store" it until the Adapter can successfully execute it. Once the Adapter has achieved the off-line state, bit 1 of the status byte is set low (logical zero). The idle state is defined as:

- No current outstanding Channel commands are awaiting completion.

The Adapter is not currently engaged in receiving a new incoming command.

The Adapter is not engaged in sending Asynchronous Status.

Until the above conditions exist, the Adapter will continue to function as if the OFF-LINE command had not been sent.

*Bit 5 - Initiate Sequence* - Setting this bit True commands the Adapter to begin execution of a new sequence as specified in byte three of the control buffer (see control buffer definitions). The address of the specific control buffer (logical buffer address - LBA) is loaded into the Adapter's COM3 register before the execution of the EX COM1. (Upon receipt of an EX COM1 the Adapter loads the LBA into its Auxiliary Logical Address Register.)

Status bit 3 (Busy) will be set upon receipt of the Initiate Sequence command and will remain set until the Adapter's microprogram acknowledges the receipt of the command.

The Initiate Sequence instruction is only sent to the Adapter in response to a service request made by the Adapter through the Activity FIFO memory and the control buffers. The Adapter has asked the software for futher instructions to complete execution of a Channel command for a particular logical buffer address (LBA). The instructions are loaded into control buffer byte 3 and the Initiate Sequence EX COM1 is sent to notify the Adapter that the instructions are available in the control buffer of the particular LBA.

Bit 6 - Send Asynchronous Status - This COM1 instruction commands the Adapter to begin an asynchronous status transfer to the Channel, to the LBA set in the COM3 Register. The status to be sent to the Channel must have been previously loaded into byte 8 of the specified LBA's control buffer before the EX COM1 instruction is sent to the Adapter. Again, the LBA must be available in the COM3 Register before the instruction is sent. The Busy bit (bit 3) of the Adapter's status register will remain set until the Adapter's microprogram acknowledges receipt of the instruction.

The asynchronous status transfer is conditional, i.e., the status may or may not be sent, depending upon Channel activity with the specified LBA. If the LBA (device) was idle (no Channel command execution pending), the status will be sent and the software notified of the fact through the Status Transfer Complete mechanism. If the status could not be sent because of an incoming Channel command, the software will be notified though the use of the Activity FIFO memory and the control buffer.

*NOTE:* Asynchronous status should not be sent when software is working on completion of a Channel command. A command execution is not considered to have been completed until Device End status has been sent to and accepted by the Channel and indicated to the software through a Status Transfer Complete with the Activity FIFO memory.

## 3.2.4.4 EX COM2

Execution of an EX COM2 instruction to the

...Continued...

Adapter causes the next logical buffer address in the Activity FIFO memory to be available in the COM2 Register for reading by the software with a subsequent INPUT instruction. Execution of an EX COM2 instruction is under the control of status bit 2 (Address Available). If the FIFO memory has any logical buffer address stored, bit 2 of the status register will be set. Once the contents of the Activity FIFO memory are exhausted, the Address Available bit is reset.

Additional logical buffer addresses (if available as indicated by status bit 2) may be read from the Activity FIFO memory by issuing additional INPUT instructions to the Adapter.

The contents of the COM2 register are updated after each INPUT instruction. That is, each subsequent INPUT instruction will load the next Logical Buffer Address from the FIFO memory into the COM2 register.

Bit 2 of the status register and the Activity FIFO memory provide a means for the Adapter microprogram to signal the Datapoint processor driver software that activity has occurred with the Channel which requires its attention. (The Status bit indicates that the activity occurred, while the contents of the Activity FIFO memory indicate which logical buffer requires attention.)

The Logical Buffer Address has the following format:

3 2 1 0 ... specifies one of the 16 logical buffers within the Adapter

6 5 4 .....reserved for buffer expansion

7 .....used to indicate completion of a

status transfer

(when set to 1)

3.2.4.5 EX COM3

Execution of an EX COM3 instruction to the Adapter causes the information on the A-OUT bus to be loaded into the COM3 register. This has two purposes: to specify which logical buffer is to be used for buffer reads and writes, and which Logical Buffer Address an EX COM1 Initiate Sequence or Send Asynchronous Status command is directed to.

When used for buffer access, the content of the COM3 register has the following format:

- 3 2 1 0 ..... Logical Buffer Address

- 6 5 4 .....Reserved for Address Expansion

- 7 .....Which Buffer 0 = Data Buffer

- 0 = Data Buffer1 = Control Buffer

When used in conjunction with an EX COM1, bit 7 is not significant.

## Channel Adapter 9426

# 3.2.4.6 Auxiliary Logical Address Register

This eight-bit register stores Logical Buffer Addresses for access by the microprogam. It is loaded from the contents of the COM3 register upon execution of any EX COM1. Note that the contents of the Auxiliary Logical Address Register are used by the microprogram only if the EX COM1 instruction was an Initiate Sequence or a Send Asynchronous Status command. For all other EX COM1 instructions, the microprogram ignores the contents of this register.

## 3.2.4.7 EX COM4

The COM4 register stores the byte address, within a logical buffer, for use during buffer reads and writes. Execution of an EX COM4 instruction loads the COM4 register with the information on the A-OUT bus. If the Adapter is in Data mode (see 3.2.4.9), execution of an EX COM4 instruction also causes a buffer read; COM3 register contents specify which buffer is to be read.

The Adapter uses only the first four low-order bits of the COM4 register for control buffer access. (The control buffers are sixteen bytes deep.) It uses all eight bits of the register for addressing byte locations within a buffer. (The data buffers are 256 bytes deep.)

## 3.2.4.8 EX WRITE

If the Adapter is not in Data mode, an EX WRITE instruction causes the information on the A-OUT bus to be written into a buffer location (as specified by the contents of the COM3 and COM4 registers). An EX WRITE does not change the existing Status/Data mode of the Adapter. Data to be written into a buffer must be loaded into the A register (of the Datapoint processor) before execution of the EX WRITE.

## 3.2.4.9 EX DATA

An EX DATA instruction places the Adapter in its Data mode, in which execution of an EX COM4 instruction will cause a buffer read to occur (buffer and byte address specified by the contents of the COM3 and COM4 registers). Thus the "Data" mode allows the Datapoint processor driver software to read from one of the sixteen control buffers or one of the sixteen data buffers. Execution of an EX ADR, EX STATUS, or EX COM2 changes the Adapter's mode from Data to either the Status mode (EX ADR and EX STATUS) or the FIFO memory mode (EX COM2).

## 3.2.4.10 EX STATUS

An EX STATUS instruction places the Adapter in Status mode, as will execution of an EX ADR instruction with proper address and parity on the AOUT bus, making the contents of the status register available during subsequent execution of an INPUT instruction. Execution of an EX DATA or an EX COM2 will change the Adapter mode from Status to either Data mode or FIFO memory mode.

3.3 Control and Data Buffer Format

The Adapter has sixteen control buffers and sixteen data buffers. Each logical buffer address (LBA) has both a control and a data buffer associated with it. There are sixteen logical buffer addresses (000-017) corresponding to the sixteen control and sixteen data buffers. In addition, each LBA may be associated with a device address used by the IBM Channel.

The control buffers contain status and control information required for communication between the microprogram and the adapterdriver software. The data buffers are used to buffer data to or from the Channel.

Data stored in the data buffer may be in IBM EBCDIC code or be binary; data for transmission via the I/O interface is normally EBCDIC. The driver software must provide a translation process for converting EBCDIC coded data to ASCII coded data for use within the Datapoint system. Data to be transferred to the IBM System 360/370 must be translated by the driver software from ASCII code to IBM EBCDIC code.

9426

\_Continued....

3.3.1 Control Buffer Format

3.3.1.1 Byte 0 - Channel Address

This byte contains the eight-bit IBM device address assigned to the logical buffer during system configuration. The Channel uses it to address one of the Adapter's logical buffers.

3.3.1.2 Byte 1 - Channel Command

This byte contains the command received from the Channel during an initial selection sequence. Bit 0 of byte 5 is set (Command Received), when a command is stored. All commands with valid parity are stored, except for the Test I/O and No-Operational Control commands. Command decoding is done by the adapter-driver software.

3.3.1.3 Byte 2 - Initial Selection Byte

This byte contains the eight-bit status that is returned to the Channel during an initial selection sequence. The status byte has the following format:

- Bit 0 =Unit Exception

- Bit 1 =Unit Check

- Bit 2 = Device End

- Bit 3 = Channel End

- Bit 4 = Busy

- Bit 5 = Control Unit End Bit 6 = Status Modifier

- Bit 6 =Status Modif Bit 7 =Attention

When a device goes from Ready to Not Ready state, the driver software sets the Unit Check bit (Bit 1) before ending status is sent. This is the only case in which the adapter-driver software will write to the initial selection status byte.

### 3.3.1.4 Byte 3 - Datapoint Control

This byte contains the Adapter control information by which adapter-driver software controls the Adapter. It has the following format:

Bit 0 = Reserved Bit 1 = Execute Read Data Transfer Bit 2 = Execute Write Data Transfer Bit 3 = Excute Ending Procedure Bit 4 = Selective Reset Acknowledged Bit 5 = Reserved Bit 6 -7 = Reserved These control bits have the following effects on the Adapter when an Initiate Sequence COM1 instruction is issued to it:

Bit 1 - Execute Read Data Transfer - Causes the Adapter to initiate a read data transfer with the Channel, in response to either a sense or read command from the Channel during initial selection. Data from the data buffer is sent to the Channel until either the number of data bytes transferred to the Channel equals the count in byte 4 of the control buffer or the Channel halts data transfer by one of the following means: Stop data transfer, Halt I/O, Selective Reset, or a System Reset.

Bit 2 - Execute Write Data Transfer - Causes the Adapter to initiate a write data transfer with the Channel, in response to a write command from the Channel during an initial selection. Data from the Channel is written into the data buffer until either the number of data bytes transferred equals the count in byte 4 of the control buffer or the Channel stops data transfer by one of the following means: stop data transfer, Halt I/O, Selective Reset, or a System Reset.

*Bit 3 - Execute Ending Procedure -* Causes the Adapter to initiate an ending status transfer to the Channel, in response to one of the following conditions:

- 1 Control Command Received from the Channel.

- 2 Normal End on Read/Write.

- 3 Halt I/O Received.

- 4 Stop Received on Read/Write.

- 5 Channel Parity Error/Command Received.

- 6 Status Transfer Complete (Only if Device End status was not presented in the previous ending procedure.)

The Adapter uses the status byte from byte 8 of the control buffer. Before issuing an ending procedure command to the Adapter, the adapter-driver software must write the proper ending status into byte 8 of the control buffer. Upon successful transfer of the status byte, the Adapter will signal "Status Transfer Completed" by using the Activity FIFO memory. The logical address of the control buffer will be placed into the FIFO memory with the high order bit (bit 7) set.

Bit 4 - Selective Reset Acknowledged - Causes the Adapter to complete the selective reset procedure on a selected device. This command is used for interlocking purposes. It is issued to the Adapter in response to a selective reset indication.

Bit 5 - Reserved - This bit is reserved.

## 3.3.1.5 Byte 4 - Initial Byte Count

This byte of the control buffer contains the number of bytes (1-256, where 0 represents 256), to be transferred to or from the Channel in response to a read, sense, or write command. The byte count must be written into the control buffer by the driver software before an Initiate Sequence EX COM1, specifying a read or write data transfer (see Datapoint Control), is sent to the Channel Adapter.

## 3.3.1.6 Byte 5 - IBM Control

This byte contains control information for the driver software. It specifies the type of activity that has occurred with the logical buffer. Whenever information in the IBM Control byte changes (due to activity with the Channel), the adapter-driver software is flagged through the activity FIFO memory. (The address of the logical buffer is placed into the FIFO memory. This causes the Address Available status bit to be set.) The IBM Control Byte has the following format:

Bit 0 = Command Received Bit 1 = Halt I/O Received Bit 2 = Selective Reset Bit 3 = Normal End on Read/Write Bit 4 = Stop Received on Read/Write Bit 5 = Reserved Bit 6 = Reserved Bit 7 = Channel Parity Error

Note that bit 7 may be set in combination with the bits 0 - 4. Bits 0 - - 4 will only have one bit set at a time.

The control bits have the following meaning:

*Bit 0* - Command Received - This bit is set after the Adapter has received a command from the Channel other than a Test I/O or No-Operational Control command. The command that was sent during the initial selection is available in byte 6 of the control buffer.

*Bit 1* - Halt I/O Received - This bit is set after the Adapter has received a Halt I/O (Interface Disconnect) indication from the Channel. If a data transfer was in progress at the time of the Halt I/O indication, the actual number of bytes transferred is contained in byte 6 of the control buffer.

*Bit 2* - Selective Reset - This bit is set after the Adapter has received a Selective Reset indication from the Channel. The logical buffer will appear as a busy I/O device to the Channel until the adapter-driver software responds with a Selective Reset Acknowledged, Initiate Sequence EX COM1.

*Bit 3* - Normal End on Read/Write - This bit is set when the Adapter is transferring data and the number of bytes transferred reaches the initial byte count (byte 4 of the control buffer). The ending byte count in byte 6 is stored and is equal to the initial byte count in byte 4.

Bit 4 - Stop Received on Read/Write - This is set after the Adapter has received a stop indication from the Channel during a data transfer. The actual number of bytes transferred is stored in the ending byte count (Byte 6).

Bit 5 - This bit is reserved.

*Bit 7* - Channel Parity Error - This bit is set whenever the Adapter has detected invalid parity on Bus Out. If the parity error was detected during a data transfer, the error will not be indicated until the transfer is terminated. Whenever the Channel Parity Error bit is set, the adapter-driver software should respond with a Unit Check status ending procedure.

3.3.1.7 Byte 6 - Ending Byte Count

This byte specifies the actual number of bytes (1 to 256), where 0 represents 256 bytes transferred during a data transfer. If the data transfer ends normally, the ending count will equal the initial byte count in byte 4. If a Stop or Halt I/O was received, the ending count will be less than the initial count.

### 3.3.1.8 Byte 7 - Device Flag Word

This byte contains internal flags for the microprogram. Only bit 7 of the Device Flag is used for communication between the microprogram and the adapter-driver software. Bit 7 is set by the driver software, before system configuration, if the logical buffer is to be used. Once system configuration has been performed, the contents of the Device Flag Word should be ignored by the adapter-driver software.

#### 3.3.1.9 Byte 8 - Ending and Asynchronous Status Byte

This byte contains the eight-bit status that is sent to the Channel during either an ending procedure, or during an asynchronous status transfer, as specified by an EX COM1 instruction and the contents of byte 3 of the control buffer. The status byte has the following format:

- Bit 0 = Unit Exception

- Bit 1 = Unit Check

- Bit 2 = Device End

- Bit 3 = Channel End

- Bit 4 = Busy

- Bit 5 = Control Unit End

- Bit 6 = Status Modifier

- Bit 7 = Attention

## Channel Adapter 9426

### 3.3.1.10 Bytes 9 through 15

Bytes 9 through 15 of the control buffer are reserved for use by the microprogram.

3.3.2 Data Buffer Format

There are sixteen data buffers in the Channel Adapter. Each data buffer is associated with a control buffer that has the same logical buffer address. The data buffers are used to store data during read and write data transfers.

#### 3.4 Off-line Procedures

Before the Channel Adapter can communicate with the IBM Byte Multiplexor Channel, it must be initialized and brought on line, a procedure in which both the driver software in the Datapoint processor and the microprogram in the Channel Adapter take part.

Initialization consists of clearing Adapter control buffers and then configuring them with the device addresses to be used by the Channel to identify these buffers.

#### 3.4.1 Power-up Procedure

Turn on power to the Datapoint processor first, because even though the Channel Adapter has an independent On/Off switch, it does nothing unless I/O power from the Datapoint processor is present.

After the Datapoint processor is on, turn on the Main Power On/Off Switch located on the rear of the Channel Adapter. This switch should be left on unless the Adapter is being serviced.

Now, use the Controlled Power On/Off Switch on the Adapter's front panel to turn on its power; the Adapter will immediately execute an automatic power-on reset cycle during which all Adapter logic -- except for the control buffers, data buffers, and the active address RAM -- is brought to its initial state, and the Adapter status registers and activity FIFO buffer are cleared. Also, the IBM interface logic is switched from bypassing the Select Out signal to logically propagating it.

#### 3.4.2 Power-down Procedure

Normally, use the Adapter Controlled Power On/Off Switch to power down, because this sequence, too, is under microprogram control which will not allow the Adapter to power down until it has been taken off-line to the IBM Channel by the driver software in the Datapoint processor.

Once the Adapter is off-line to the Channel, the power down sequence switches the IBM interface logic from propagating the Select Out signal to bypassing it; cuts off the output signals from the Adapter to both the Datapoint and IBM interfaces.

In an emergency, power down the Adapter by turning off the Main Power On/Off Switch on the rear panel, but understand that such an action ignores all control interlocks and will almost certainly cause unpredictable errors on the IBM Channel.

#### 3.4.3 System configuration

Three system configuration tasks must be done to make the Adapter operational, in this sequence:

•Master Clear •Configure System •Go ON-LINE

3.4.3.1 Master Clear

Master Clear, initiated by the Datapoint processor driver software and performed by the Adapter microprogram, clears all sixteen control buffers in the Adapter. The driver software initiates Master Clear by addressing the Adapter and issuing a Master Clear EX COM1.

When this has been done, the busy bit of the Adapter's status byte will be set and remain set until the microprogram completes the Master Clear, at which time it will be reset.

\_Continued....

9426

## 3.4.3.2 Configure System

Upon completion of the Master Clear, the Adapter microprogram resets its busy bit and the Datapoint processor adapter-driver software configures the Adapter control buffers for on line usage, by placing the address to be used by the IBM Byte Multiplexor Channel in byte 0 of each control buffer that is required to be active.

Each logical buffer corresponds to one IBM I/O device address, thus each address assigned to a control buffer must be uniquely different than all other addresses used by other control buffers and other control units on the Channel.

See IBM System 360 and System 370 1/O Interface Channel to Control Unit Original Equipment Manufacturers' Information, GA22-6974-4, or Principles of Operation Manual for further addressing restrictions in relationship to the IBM System.

As each desired address is written into byte 0 of a control buffer, the Datapoint processor driver software must set the high-order bit (bit 7) of the control buffer byte 7 (Device Flag Word).

This bit serves as a flag to the Adapter microprogram; when set (to a logical 1), the control buffer is considered to be an active buffer. The bit is set by writing an octal 0200 to byte 7 of the desired control buffer.

Special Note: All models of the IBM System 360/370 carry I/O device addressing restrictions. To avoid possible Channel errors, users should consult the IBM Functional Characteristics manual for the particular model number of System 360/370 and the Principles of Operation manual in use before assigning device addresses to Adapter logical buffers.

After it has configured the Adapter control buffers, the Datapoint processor driver software issues a Configure System EX COM1 to the Adapter, causing the Adapter microprogram to branch to a configuration routine in which it scans all the control buffers, checking each control buffer's Device Flag Word (byte 7) for the status of its high-order bit.

If the high-order bit is not set, the microprogram moves on to scan the next

buffer; if the bit is set, it reads the device address from buffer byte 0, and uses it to access the active address RAM on the sequencer logic card. At that address location in the RAM the microprogram writes the logical address of the control buffer together with an active indication bit.

(Recall that active address RAM locations were cleared to all zero values during Master Clear execution.)

After placing the logical buffer address into the RAM location specified by the device address, the Adapter microprogram continues to scan any remaining control buffers. The Adapter microprogram follows acknowledgement of receipt of the Configure System EX COM1 by resetting the busy bit in its status register.

## 3.4.4 Going ON-LINE

At completion of Configure System execution, the Adapter is ready to go ON-LINE. Its microprogram will try to place the Adapter online when it receives an ON-LINE EX COM1 from the Datapoint processor driver software.

Before the Adapter can go ON-LINE, however, proper conditions must exist, either on the IBM Channel interface -- if the Adapter is in OPERATE mode -- or on the Adapter's Simulator -- if the Adapter is in TEST mode.

The proper condition on the IBM Channel interface is that the IBM CPU is in the stop or wait state. Refer to the Simulator operation, Section 3.6.10, for comparable conditions in TEST mode.

When the Adapter goes ON-LINE, the ON-LINE and Configured bit (bit 1) of its status byte is set. When the microprogram acknowledges receipt of the ON-LINE EX COM1 instruction, it resets its busy bit. Once ON-LINE, the Adapter is ready to communicate with the IBM Channel; it signals this condition by lighting the ON-LINE indicator.

## 3.4.5 Going OFF-LINE

The Datapoint processor adapter-driver software should issue an OFF-LINE EX COM1 instruction only when the Adapter is ON-LINE, and in an idle state, i.e., no current Channel operations in progress. An interlock in the microprogram manages the asynchronous conditions that exist between the Channel, the Adapter, and the driver software; it prevents the Adapter from going OFF-LINE until all its logical buffers are idle. It is possible, therefore, that the Adapter may not go OFF-LINE immediately after the execution of an OFF-LINE EX COM1, and the driver software must take this possibility into account. The Adapter's microprogram stores the fact that an OFF-LINE command was received, and allows the Adapter to comply with that command as soon as conditions permit.

## 3.5 ON-LINE Operation

Once the Adapter has been configured and brought ON-LINE, various interface sequences take place, in response to requests initiated by either the Datapoint processor or the IBM System 360/370.

### 3.5.1 Channel Sequence Definition

On the IBM Byte Multiplexor Channel data transfer proceeds through three phases: Initial Selection, Data Transfers, and Ending Sequence.

For a more detailed discussion of this operation, refer to IBM System 360 Principles of Operation, G22-6281, IBM System Principles of Operation GA22-7000, IBM System 360 and System 370 Interface Channel to Control Original Equipment Manufacturer Information, GA22-6974-4.

Initial Selection- During Initial Selection the IBM System 360/370 Channel addresses the Adapter and issues a command. A Selective Reset or Halt I/O can also be issued in this way.

Data Transfer- The Adapter requests service from the Channel and after being selected, effects the transfer of data to or from the Channel.

*Ending Sequence-* After the entire data block has been transferred, the Adapter requests service from the Channel and, after being addressed, transfers the status byte to the Channel.

### 3.5.2 Microprogram Polling Scheme

A polling routine in the Adapter microprogram controls all activity between the logical buffers and the Channel, with a view to preventing any one logical buffer from monopolizing the resources of the Adapter, and making all active logical buffers work multiplex fashion.

On a Byte Multiplexor Channel, multiplexing between logical buffers requiring service occurs once for every four data bytes transferred. Multiplexing on this kind of Channel also occurs between initial selection sequences and between ending (status transfer) sequences.

(Note that the hardware may be strapped for either one-byte or four-byte mode of operation.)

When a command is received from the Channel during an initial selection sequence, a logical buffer is placed in a queue. It remains in the queue until either a System Reset occurs or the Adapter presents Device End status to the Channel and the Channel accepts it. ....Continued...

A logical buffer may exist in four states:

• NOT ACTIVE -- not configured during Adapter configuration

• ACTIVE-- configured, but in an idle state

• ACTIVE, SERVICE REQUIRED -- waiting instructions from Adapter driver software

• ACTIVITY OCCURRING -- executing an instruction received from adapter-driver software

When a logical buffer changes from the ACTIVE state to the ACTIVE, SERVICE REQUIRED state the Datapoint processor driver software is informed of the change by use of the Activity FIFO. Bit 2 of the Adapter's status byte is set and the logical buffer's address is placed in the FIFO. Bit 0 of byte 5 of the control buffer is also set. This transition occurs when a new command is received from the Channel.

Transition from the ACTIVE, SERVICE REQUIRED state to the ACTIVITY OC-CURRING state takes place when the Datapoint software control program responds to the service requirements made by the Adapter activity FIFO and control buffer. Response from the software may vary, depending on what the command from the Channel requires of it and the Adapter. In all cases, however, the driver software issues an Initiate Sequence EX COM1 to the Adapter. Additional information required by the Adapter microprogram for execution of the sequence is contained in byte 3 of the control buffer.

Upon completion of the sequence, the Adapter logical buffer may return either to the AC-TIVE, SERVICE REQUIRED state or to the ACTIVE state. Transition is to the ACTIVE state only if the last sequence executed was an Ending Procedure and the Ending Status contained Device End status, or if a System Reset occurred.

3.5.3 Initial Selection Sequence

The IBM System 360/370 initiates I/O operations by the START I/O (SIO) instruction. The operand of the SIO instruction specifies both the Channel and the I/O device for which I/O is required. The Channel specified by the operand fetches the first Channel Command Word (CCW) from main storage using the address stored in the Channel Address Word (CAW), which is always stored in location 72 of the main storage.

The CCW specifies the command to be given to the I/O device, data address, and the number of data bytes to be transferred. It also uses a number of flag bits to modify the I/O operation.

.

## Channel Adapter 9426

To initiate an I/O operation, the Channel places the address from the SIO operand of the desired I/O device on BUS OUT and raises ADDRESS OUT. Each control unit connected to the Channel attempts to' decode the address on the bus, but I/O addresses are uniquely assigned, so only one finds itself addressed. To be acceptable, the address must exhibit correct parity.

The Channel Adapter uses the Active Address RAM on the sequencer logic card for address decoding. The logical buffer addresses for all active device addresses, up to the maximum of sixteen possible, are contained in this RAM.

The Adapter uses the address from the IBM BUS OUT to address the RAM. If the address on BUS OUT matches one of the active addresses assigned to the Adapter -- established during System Configuration while OFF-LINE -the logical buffer address (LBA) assigned to the address will appear on the output of the RAM, and the high-order bit (bit 7) of the LBA will be set, indicating that a match has been made.

The next action of the Channel is to issue a SELECT OUT (along with HOLD OUT). When the incoming SELECT OUT -- or SELECT IN, depending on control unit priority strapping -- appears, the Adapter does not allow it to propagate, and the Adapter microprogram raises the OPERATIONAL IN line.

If the address on BUS OUT did not match an address assigned to the Adapter, the sequencer propagates SELECT OUT (or SELECT IN, as noted above) and the microprogram is not disturbed.

When the IBM Channel senses the rise of OPERATIONAL IN, it responds by dropping ADDRESS OUT. If none of the control units attached to the Channel recognize the address, the Channel will receive the SELECT IN signal and an error will be flagged.

After the Channel drops ADDRESS OUT, the Adapter responds by placing the device address -- taken from control buffer byte zero, using the LBA from the active address RAM -- on BUS IN, and then raises the ADDRESS IN tag line.

For a Byte Multiplex operation the Channel drops HOLD OUT and SELECT OUT at this time. The Channel then compares the address on BUS IN with the address from the SIO operand; if they match, the Channel places the command byte (from the CCW) on BUS OUT and raises the COMMAND OUT tag line.

If the address on BUS IN does not match the one from the SIO operand an error is flagged and the control unit may be released by placing a TEST I/O command on BUS OUT and signalling COMMAND OUT.

When the Channel raises COMMAND OUT, the Adapter takes the command from BUS OUT. Neither a TEST I/O nor a NO-OPERATION control command will be placed in the Adapter control buffer. All other commands are stored in the control buffer (byte one), after which the Adapter signals the Channel by dropping ADDRESS IN, and the Channel responds by allowing COMMAND OUT to fall. When COMMAND OUT falls, the Adapter places status -- obtained from the Initial Status Byte of the control buffer -- on BUS IN.

If the command was a NO-OPERATION control command, the Adapter generates CHANNEL END, DEVICE END status and places it on BUS IN, then raises the STATUS IN tag line.

If the Channel accepts this status condition, it responds with the SERVICE OUT line, which allows STATUS IN to fall, thus completing the initial selection sequence. If SELECT OUT is down at this time, the Adapter drops STATUS IN and then OPERATIONAL IN. Bit one of byte 5 (Command Received bit of the IBM control word) is set and the Datapoint processor adapter-driver software is notified by the placing of the LBA into the activity FIFO, which results in the setting of the ADDRESS AVAILABLE status bit.

If the Adapter raises STATUS IN, a COM-MAND OUT response from the Channel in-

9426

## Continued....

dicates that it cannot currently accept the initial status and the status is stacked, whereupon the Adapter drops STATUS IN and then OPERATIONAL IN (if SELECT OUT is down at this time). The Adapter does not notify the driver software until the initial status byte is accepted by the Channel, either through a reselection or through the use of a TEST I/O command during a Channel-initiated initial selection sequence.

If SELECT OUT is active at the time STATUS IN falls, the driver software is notified by the setting of the SELECT OUT bit along with the COMMAND received bit in the IBM CON-TROL WORD of the selected control buffer. This indicates that the Byte Multiplexor Channel is forcing burst mode.

Note that the Channel will not stack an initial status byte of zero, unless the command presented to the Adapter was a TEST I/O.

## 3.5.4 Control Unit Busy Sequence

If the microprogram cannot currently execute an initial selection sequence because of outstanding housekeeping requirements, the sequencer will execute a short Control Unit Busy Sequence to the Channel. This short sequence is handled entirely by the sequencer hardware, allowing the microprogram to continue its housekeeping uninterrupted.

The control-unit-busy sequence begins when the Channel places the I/O device address on BUS OUT and raises ADDRESS OUT, followed by SELECT OUT. Each control unit attached to the Channel's interface attempts to decode the address on BUS OUT.

When the Channel Adapter detects SELECT OUT -- and only if the address on BUS OUT matches one of the addresses assigned to one of its logical buffers -- the sequencer will not allow propagation of the signal. Instead, it places control unit busy status -- BUSY, STATUS MODIFIER, and CONTROL UNIT END bits set -- on BUS IN, then raises STATUS IN, but does not raise OPERATIONAL IN.

After accepting the status byte, the Channel drops SELECT OUT, to which the Adapter responds by dropping STATUS IN and logically disconnecting from the interface. The Channel keeps ADDRESS OUT up until STATUS IN drops, thus completing the control-unit-busy-sequence. *NOTE:* The short control-unit-busy sequence implies that the Adapter is only temporarily busy. A busy condition may be considered temporary if it lasts less than approximately 2 milliseconds.

### 3.5.5. Address Available Responses

When the Datapoint processor software recognizes the Address Available status from the Adapter, it reads the logical buffer address (LBA) from the Activity FIFO and uses that to point to the control buffer requiring its attention. Control information is contained in byte 5 of the buffer; its source is the IBM Control Word.

If the Channel just performed an Initial Selection Sequence and the command sent to the Adapter was neither a TEST I/O or a NO-OP, the COMMAND RECEIVED bit (bit 0) will be set in the control word. Two other bits may be set along with the COMMAND RECEIVED bit: SELECT OUT (bit 5) or CHANNEL PARITY ERROR (bit 7) or both.

The SELECT OUT bit indicates that the Datapoint processor software should immediately respond to the service request from the LBA, suspending multiplexing on other LBAs currently active. It means that the Byte Multiplexor Channel is forcing burst mode.

If the Multiplexor Channel is forcing burst mode, the Datapoint processor software must respond in less than 500 milliseconds to avoid possible error conditions. The Channel should not indicate a malfunction unless a delay of interface activity exceeds approximately 30 seconds; however, possible data overrun conditions can come to exist on non-buffered I/O devices if the delay is excessive.

Four other bits in the IBM Control Word may be set when an Address Available status indication is given to the driver software:

## 3.5.5.1 HALT I/O RECEIVED (Bit 1)

When the Channel issues a Halt I/O sequence to the Logical Buffer Address this bit is set. In response to it, the Datapoint processor software normally generates an ending status, provided that the LBA was executing a Channel command, i.e., was not in the AC-TIVE ONLY state.

## 3.5.5.2 Selective Reset (Bit 2)

This bit is set when the Channel issues a Selective Reset to the LBA. The driver software should respond to it by setting the SELECTIVE RESET ACKNOWLEDGED bit (bit 4) in the Datapoint Control Word (DPCW, byte 3) of the control buffer, then issuing an Initiate Sequence EX COM1 to the Adapter. A Selective Reset cancels all previous activity required by the LBA. The LBA goes to the ACTIVE ONLY state and all incomplete Channel sequences are halted. A response of INITIATE SEQUENCE causes the Adapter microprogram to clear the control buffer except for the Channel address byte (byte 0) and the Active bit in byte 7.

Because of the asynchronous nature of the Selective Reset, an interlock in the Adapter microprogram prevents any other activity from taking place with a Logical Buffer Address until the Datapoint driver software returns a SELECTIVE RESET ACKNOWLEDGE to the Adapter.

## 3.5.5.3 Normal End on READ/WRITE (Bit 3)

After the Datapoint processor software has instructed the Adapter to execute a READ or WRITE data transfer with the Logical Buffer Address, the setting of this bit indicates that the data transfer has equalled the specified number of bytes to be transferred, i.e., the Ending Byte Count -- Byte 6 of the control buffer -- is equal to the Initial Byte Count in Byte 4.

If the LBA in use is emulating a unit record I/O device such as a card reader or line printer the Initial Byte Count will contain the UNIT RECORD LENGTH -- for example, 80 bytes for a card reader; when NORMAL END occurs the driver software should respond by executing an ending procedure set up. However, if the LBA is emulating a tape control unit, additional data transfers may be necessary, and a data transfer set up should be executed by the driver software.

## 3.5.5.4 Stop Received on READ/WRITE (Bit 4)

If set, this bit indicates the Channel has stopped a data transfer in progress on the LBA by issuing a COMMAND OUT response to the SERVICE IN tag. The Ending Byte Count (Byte 6 of the control buffer) contains the actual number of bytes that were transferred. The driver software should respond with an ending procedure set up.

## 3.5.6 Command Decoding

Following a Channel initiated Initial Selection Sequence, the Adapter notifies the Datapoint processor software control program that a command has been received from the Channel. If there has been no parity error, the driver software must decode this command and take action on it. The Channel command is stored in byte 1 of the control buffer following the initial selection sequence. It will have one of the following formats.

## Continued....

| Command Type:         | B.<br>Data | - | int |   |   | sitio<br>ven |   | on, |

|-----------------------|------------|---|-----|---|---|--------------|---|-----|

|                       | 7          | 6 | 5   | 4 | 3 | 2            | 1 | 0   |

| Test I/O*             | 0          | 0 | 0   | 0 | 0 | 0            | 0 | 0   |

| Sense                 | Μ          | Μ | М   | М | М | 1            | 0 | 0   |

| Read Background       | Μ          | Μ | М   | М | 1 | 1            | 0 | 0   |

| Write                 | Μ          | Μ | Μ   | М | М | М            | 0 | ł   |

| Read                  | Μ          | М | Μ   | М | М | М            | ł | 0   |

| Control               | Μ          | М | Μ   | М | М | Μ            | 1 | 1   |

| Basic Sense           | 0          | 0 | 0   | 0 | 0 | 1            | 0 | 0   |

| No-Operation Control* | 0          | 0 | 0   | 0 | 0 | 0            | 1 | 1   |

#### M = Modifier Bit

\* The Test I/O and No-Operation Control commands are handled by the microprogram and do not require any action from the software control program.

The modifier bits (symbolized by M) are used to modify the basic command codes and make them dependent upon the I/O device type. More information about this feature is available in the IBM System Reference Library publications for specific I/O devices. For command information on the following IBM unit record equipment consult Section 6.0:

IBM 2501 CARD READER IBM 1403 LINE PRINTER IBM 1052 KEYBOARD - PRINTER IBM 2540 CARD - READER PUNCH IBM 1443 LINE PRINTER

#### 3.5.6.1 Command Reject

If the command byte does not match the list of valid commands for the I/O device being emulated, the Datapoint processor software program must reject it.

The Adapter indicates command rejection to the Channel by use of an ending procedure. Unit Check status is placed into the Ending/Asynchronous status byte of the LBA's buffer (byte 8), and an Execute Ending Procedure Datapoint Control Word is then written into byte 3 of the control buffer. Then an Initiate Sequence EX COM 1 is issued to the Adapter.

Note that before the EX COM1 instruction is attempted, the software program must ensure that the proper LBA has been loaded into the Auxiliary Register.

After this, the Adapter will attempt to present the Unit Check status to the Channel by initiating a Control Unit Initial Selection Sequence. The Adapter raises the REQUEST IN tag to the Channel, a signal which will force the Channel to conduct a polling sequence as soon as it is free to do so. The next time SELECT OUT rises at the Adapter and no I/O

## Channel Adapter 9426

selection is being attempted by the Channel (ADDRESS OUT is down), the Adapter will not propagate the SELECT OUT signal but will capture the interface by raising the OPERATIONAL IN tag'.

At that, the Adapter places the device address corresponding to the LBA rejecting the command on BUS IN; when the Channel recognizes the address, it sends COMMAND OUT to the Adapter as a signal to proceed. When it sees COMMAND OUT, the Adapter drops ADDRESS IN; the Channel responds by dropping COMMAND OUT. The Adapter then places the status from byte 8 of the control buffer on BUS IN and raises the STATUS IN tag.

The Channel may accept or reject status. If it accepts the STATUS, the Channel raises SERVICE OUT, which allows the Adapter to drop STATUS IN and OPERATIONAL IN.

After dropping these tags and clearing the interface the Adapter microprogram informs the Datapoint processor driver software that status has been sent to and acknowledged by the Channel during another Control Unit-initiated Initial Selection Sequence, or during a Channel-initiated Initial Selecton Sequence with a Test I/O command.

Once the stacked status has been accepted by the Channel, the Adapter informs the driver software through use of the Activity FIFO and the Ending Procedure Complete bit.

When the Channel receives Unit Check status it will normally respond by issuing a SENSE command to the I/O device that sent Unit Check. The software driver must have SENSE data available for the Channel once a command is rejected. The first six bits of the first sense data byte -- sense byte 0 -- are common to all I/O devices having this type of information; these bits are:

#### IBM Bit

7.....Command Reject

6....Intervention Required

5....Bus-Out Check

4....Equipment Check

3....Data Check

2 1 0....Overrun

Datapoint

Bit

0.....Command Reject 1....Intervention Required 2....But-Out Check 3....Equipment Check 4....Data Check 5 6 7....Overrun

The SENSE command begins like all other Channel-initiated initial selection sequences. At the end of it the COMMAND RECEIVED bit is set and the LBA is placed into the Activity FIFO memory. The software program must then supply the proper sense data (Command Reject Bit set) to the LBA's data buffer. Next, the initial byte count (byte 4) of the control buffer is set to the number of sense bytes that are to be transferred to the Channel. Finally, the Execute Read Data Transfer bit is set in byte 3 (DPCW) of the Control buffer, and an Initiate Sequence EX COM1 is sent to the Adapter.

The software program must always ensure that the proper LBA is loaded into the COM3 register before issuing an Initiate Sequence EX COM1.

The rest of the sense operation resembles a Read Data transfer. Once the sense data has been sent to the Channel the driver software should reset its sense byte to ensure that the same information is not retransmitted at the next sense inquiry.

## 3.5.6.2 Normal Command Procedures

The Channel issues three kinds of "normal" commands to the Adapter: Read, Write, and Control.

## \_Continued....

Unless an error has been detected -- such as Command Reject -- Read and Write commands always result in a Data Transfer sequence. The Sense command is essentially a Read command except that it has a different data source. Control Commands are immediate-type commands, i.e., ending status is immediately presented to the Channel following the initial selection sequence.

The Datapoint software driver responds to both Read and Write commands in similar fashion. It decodes the command and checks for validity. If a Read, data is loaded into the data buffer. Note that the data must first be translated from ASCII to EBCDIC.

For both Read and Write commands, the Initial Byte Count (control buffer byte 4) is set to the desired record length. (An Initial Byte Count of zero is assumed to mean a 256 byte data transfer.)

Next, the correct Datapoint Control Word (DPCW) must be written into control buffer byte 3. If a Read, the Execute Read Data Transfer bit (bit 1) of the DPCW is set; if a Write, the Execute Write Data Transfer bit.

Finally, an Initiate Sequence EX COM1 instruction is sent to the Adapter ending the software response sequence. These activities will cause the Adapter to begin a Control Unit Initiated Sequence.

Note that Read and Write commands may contain control information such as stacker select information for a card reader. This control information may be ignored if the emulated I/O device is not a physical device, i.e., if it is a disk file. Such information usually does not effect the data transfer unless the device is in a state that inhibits total execution of a command.

Control commands require an Ending Procedure response by the software. Ending status -- usually CHANNEL END. DEVICE END -- is written into byte 8 (ENDING/ ASYNCHRONOUS STATUS BYTE) of the control buffer. The Execute Ending Procedure bit is set in the DPCW (byte 3) of the control buffer, and an Initiate Sequence EX COM1 is issued to the Adapter, which in turn begins a Control Unit Initiated Sequence to present the status to the Channel.

## 3.5.6.3 Parity Error on Command Received

If the CHANNEL PARITY ERROR bit in the IBM CONTROL WORD is set with the COMMAND RECEIVED bit, a parity error has occurred during the initial selection sequence. The validity of the command byte in the control buffer is questionable, therefore the Datapoint processor driver software should not attempt to decode it. The error condition must be signalled to the Channel in the same manner as a Command Reject condition.

The software program instructs the Adapter to send a Unit Check status byte to the Channel, using the Ending Procedure sequence. However, the sense data to be retained by the software should reflect the parity error condition by the setting of the BUS OUT check bit. The rest of this procedure is identical to that of the Command Reject procedure.

## 3.5.7 Control-Unit-Initiated Sequence

When the Adapter requires service from the Channel, it raises REQUEST IN to the Channel. Thereafter, the next time SELECT IN rises at the Adapter and no I/O selection is being attempted by the Channel (ADDRESS OUT is down) the Adapter raises OPERATIONAL IN and places the address of the I/O device -- Channel address associated with the LBA requiring service -- on BUS IN.

The Adapter signals ADDRESS IN to inform the Channel that the information on BUS IN is the address; the Channel sends COMMAND OUT to the Adapter to indicate that it should proceed. The Adapter thereupon drops ADDRESS IN, to which the Channel in turn responds by dropping COMMAND OUT.

If the service request is for data, the sequence then proceeds as in DATA TRANSFER. The control-unit-initiated selection for data transfer occurs in Byte Multiplex mode.

If the service request is for status information the sequence proceeds as defined for the status cycle in the ending procedure.

### 3.5.7.1 Data Transfers

To transmit data to the Channel (Read Data Transfer), the Adapter places a data byte on BUS IN and raises SERVICE IN. It maintains the validity of BUS IN until an OUT TAG (see 3.6.6) from the Channel is raised in response.

To request data from the Channel (Write Data Transfer), the Adapter raises SERVICE IN and the Channel places the data byte on BUS OUT and signals by raising SERVICE OUT. The Channel maintains the validity of BUS OUT until the Adapter drops SERVICE IN, after which the Channel responds by dropping SERVICE OUT. Duration of data transfer is controlled by both the Channel and the Adapter. To give the Channel a method of controlling connection duration, a control unit cannot disconnect from the interface before SELECT OUT (or HOLD OUT) falls. However, the Adapter, by holding up OPERATIONAL IN, may preserve its logical connection after the Channel, with SELECT OUT (or HOLD OUT), has permitted it to disconnect. The Adapter may in this way force burst mode.

Either Byte Multiplexor or Burst mode is established by the duration of the connection. These modes are established so the program can schedule concurrent execution of multiple I/O operations.

If OPERATIONAL IN remains up for longer than the byte multiplexing time-out limit of 32 microseconds, selection is in burst mode; selection times less than this limit are in byte multiplex mode.

The Adapter normally transfers data in byte multiplex mode; up to four data bytes during a Data Transfer sequence. It will keep requesting service from the Channel until either the Channel stops the transfer or until the ending byte count -- in byte 6 of the control buffer -- equals the initial byte count in byte 4, transferring four data bytes at a time until the residue count is less than four bytes.

If more than one Logical Buffer Address (I/O device) has data transfer service requirements, the Adapter interleaves data transfer requests, multiplex fashion. Each data transfer sequence begins with a control-unit-initiated sequence and the address of the I/O device is always given to the Channel.

## 3.5.7.2 Burst Mode

The Adapter will force burst mode on the Channel if the FORCE BURST MODE bit in the Datapoint Control Word (DPCW -- control buffer-byte 3) was set when the software driver program issued an Initiate Sequence EX COM1. The Adapter will request service from the Channel with the normal control-unitinitiated sequence, then, once it gains connection to the interface, will keep the OPERATIONAL IN tag up until either the data byte count is exhausted or the Channel stops the transfer.

*NOTE:* This method of data transfer is not recommended, since overrun conditions may occur.

## 3.5.7.3 Ending Data Transfer

One of three situations may exist at the termination of Data Transfer.

1. The Channel recognizes the end of the operation before the Adapter reaches the initial byte count number of data bytes to be

transferred. When the Adapter requires service again, it raises the SERVICE IN line, to which the Channel responds with COM-MAND OUT, indicating STOP. The Adapter thereupon drops SERVICE IN and OPERATIONAL IN (if SELECT OUT is down) and informs the software program of the situation.

2. The Channel and the Adapter recognize the end of an operation at the same time. The number of bytes specified by the Initial Byte Count in the control buffer has been transferred.

3. The Adapter recognizes the end of the operation before the Channel reaches the end of the operation. Again, the specified number of bytes to be transferred has in fact been transferred.

In situations 2 and 3, the Normal End On Read/Write bit is set in the IBM Control Word (Control buffer - byte 5). The Ending Byte Count is equal to the Initial Byte Count and both are available in the control buffer. The Logical Buffer Address of the I/O device is placed into the Activity FIFO and the Address Available status bit is set on the Interface I logic card.

In situation 1, the Stop Received On READ/WRITE bit is set in the IBM Control Word. The Ending Byte count will be less than the Initial Byte Count. The LBA of the I/O device is placed into the Activity FIFO, setting the Address Available status bit.

### 3.5.7.4 Parity Errors During Data Transfers

If a parity error occurs on BUS OUT during a Write Data Transfer the CHANNEL PARITY ERROR bit will be set in the IBM Control Word when data transfer ends. Note that this bit may be on with either the Normal End or Stop Received bits. The Datapoint processor software program should respond with a Unit Check status Ending Procedure and make ready BUS OUT CHECK sense data.

## 3.5.8 Ending Procedure and Asynchronous Status

The Ending Procedure transfers ending status conditions to the Channel at the end of an I/O operation. Ending Procedures may be single or multiple. Note that the Ending Procedure may be used to transfer status to the Channel until Device End status is transferred; after Device End has been sent and accepted any additional status transfers must be made using the Asynchronous status transfer procedure.

Asynchronous status conditions are not related to any commands previously initiated by System 360/370 programs. One of these conditions is ATTENTION, which is generated

## Channel Adapter 9426

by the IBM 1052 console. Another is DEVICE END, generated when the corresponding I/O device goes from a not-ready to a ready state.

### 3.5.8.1 Normal Ending Procedure

An Ending Procedure must be initiated by the software program after one of the following events occurs:

- 1. Normal End On Read/Write

- 2. Stop Received on Read/Write

- Command Received (Control Command)

Command Received (Channel Parity

- Error)\* 5. Command Received (Command Reject)\*

- Command Referred (Command Referred)

Channel Parity Error at Normal End/Stop Received

- Status Transfer Completion (Other than DEVICE END)

\* NOTE: Channel End, Device End Statuss must be sent along with the Unit Check indication.

To initiate an Ending Procedure, the software program places the ending status byte into byte 8 (Ending/Asynchronous Status Byte) of the desired control buffer. Next the Execute Ending Procedure bit is set in the Datapoint Control Word (control buffer byte 3) and an Initiate Sequence EX COM1 instruction is issued to the Adapter.

When the turn of that Logical Buffer Address comes up in the queue, the Adapter will attempt a Control-Unit-Initiated sequence. Once the Adapter has been selected by the Channel it will present the ending status byte by placing it on BUS IN and raising STATUS IN. If the Channel accepts this status byte it will respond by raising SERVICE OUT, which allows the Adapter to let STATUS IN and OPERATIONAL IN fall, completing the Ending Procedure sequence.

The Channel may also stack the ending status by responding with COMMAND OUT, which also allows STATUS IN and OPERATIONAL IN to fall; in this case the Adapter will hold the stacked status until another opportunity arises to present it. Once the status has been accepted by the Channel, the Adapter signals status transfer completion to the software driver program by placing the Logical Buffer Address into the Activity FIFO with the high-order (bit 7) bit set. The status completion indication allows for Multiple Ending Procedures. The Datapoint processor software should not initiate a second Ending Procedure until the first has completed.

## 3.5.8.2 Asynchronous Status Presentation

The Asynchronous Status Procedure is used to present to the Channel status not associated with any previous command, i.e., the LBA is in the ACTIVE ONLY state. To accomplish this, the software program places the status into byte 8 of the control buffer, then issues an Asynchronous Status EX COM1 instruction. The Adapter will attempt to present this status to the Channel using the Control-Unit-Initiated sequence.

The asynchronous status presentation will be aborted if it is interrupted by a Channelinitiated selection sequence directed to the LBA that is attempting the status transfer. If this happens, the Adapter will accept the command, place it in byte 1 of the control buffer, set the COMMAND RECEIVED bit in the IBM Control Word, and then place the LBA in the Activity FIFO to notify the software program that its status transfer was preempted.

If the asynchronous status is accepted by the Channel, the Adapter will signal status transfer completion to the driver software. If the Channel stacks the status, the Adapter will retry presentation at the first opportunity. Note that once the status has been stacked, any commands from the Channel for the LBA holding status will be rejected by a DEVICE BUSY initial status byte.

### Continued....

### 3.5.9 Device Busy Status

Whenever an I/O device -- identified with a Logical Buffer Address -- cannot accept a command during an Initial Selection sequence the command is rejected by presentation of a BUSY initial status byte. Busy is indicated whenever one of the following conditions exist:

1. A previous command is being executed by the LBA (DEVICE END status has not yet been presented to the Channel).

2. Stacked status is being held by the LBA -except that if the command is a TEST I/O the stacked status will be presented after all.

3. The LBA is waiting on a Selective Reset Acknowledgement from the driver software program.

#### 3.5.10 Attention Status

ATTENTION is generated when some asynchronous condition occurs in the I/O device identified with a Logical Buffer Address which is not associated with the initiation, execution, or termination of any I/O operation. AT-TENTION should only be presented to the Channel through the use of an Asynchronous Status Transfer Sequence.

ATTENTION is used when a Logical Buffer Address is to be identified with, and emulate, an IBM 1052 Printer-Keyboard.

3.5.11 Device End Status

Device End Status occurs for either of two reasons:

1. The completion of an I/O operation at the I/O device identified with an LBA.

Device End Status is presented with the use of an Ending Procedure Sequence, which signals to the Channel that the I/O device (LBA) has completed execution of the command previously issued by it. Each I/O operation causes only one Device End condition; it is generated either simultaneously with the Channel-End condition or later -- in which case Multiple Ending Procedures are required. Once Device End has been accepted by the Channel, the Adapter's microprogram clears bytes 1, 3, and 5 of the control buffer, and resets all bits of byte 7 except for the Active bit (bit 7).

2. The transition of an I/O device (LBA) from not-ready to ready status.