### microNOVA INTEGRATED CIRCUITS DATA MANUAL

Data General Corporation, Westboro, Massachusetts 01581

# microNOVA INTEGRATED CIRCUITS DATA MANUAL

FOR DESIGN ENGINEERS

**SECOND EDITION**

### NOTICE

This manual has been prepared by Data General Corporation (DGC) to serve as a convenient compilation of integrated circuits made by DGC. DGC reserves the right to make changes at any time in order to improve circuit design and method of presentation herein. DGC does not assume any responsibility for its circuits or applications which may be made thereof, and does not guarantee that these circuits or applications thereof are free from patent infringement. DGC shall not be responsible for any damages (including consequential) caused by use of or reliance upon materials presented herein.

NOVA and ECLIPSE are registered trademarks of Data General Corporation, Westboro, Massachusetts. DASHER is a trademark of Data General Corporation, Westboro, Massachusetts.

> Ordering No. 014-000074 © Data General Corporation, 1977 All Rights Reserved Printed in the United States of America Rev. 03, November 1977

# DATA GENERAL DOMESTIC OFFICES

#### SALES AND SERVICE

ALASAMA 90 Bagby Drive Brmingham; Alabama 35209 (205) 942-3730

ARIZONA 1950 E. Watkins

Phoenix, Arizona 85034 (602) 254-6412 4633 E. Broadway Suite 100 Tucson, Arizona 85100

CALIFORNIA

2221 Rosecrans Avenue Suite 204 El Segundo, California 90245 (213) 973-0401 2445 Faber Place Palo Alto, California 94303 (415) 321-8010 15114 Downey Avenue Paramount, California 90723 (213) 633-0805 4031 No. Freeway Blvd. Sacramento, California 95834 (916) 920-3434 4305 Gesner Street San Diego, California 92117 (714) 276-8450 120 Howard Street San Francisco, California 94105 (415) 543-6730 1220 Village Way Suite A Santa Ana, Cakfornia 92705 (714) 558-9421 5276 Hollister Avenue Suite F Santa Barbara, California 93111 (805) 964-8695 7011 Havvenhurst Avenue Suite A Van Nuys. California 91408 (213) 787-8870

COLORADO

Deriver Technological Center Building No. 29 8455 E. Prentice Avenue Englewood, Colorado 80110 (303) 773-2620

CONNECTICUT 50 Shaw Road North Branford, Connecticut 06471 (203) 484-2771

FLORIDA

1001 Northwest 62nd Street Suite 404 Ft Lauderdale, Florida 33309 (305) 771-0784

8880 Lake Ellenor Drive Suite 115 Orlando, Florida 32809 (305) 851-8230 5444 Bay Canter Drive Suite 707 Tampa, Florida 33605 (613) 879-2515

GEORGIA

1639 Tullie Circle Suite 128 Atlanta, Georgia 30329 (404) 325-3181

IDAHO 130 South Cole Road Boise, Idaho 83075 (208) 375-6510

#### ILLINOIS

2524 W Farrelly Avenue SW of Route 150 and Glen Peoria, Illinois 61614 (309) 688-2224 Chicago Office 1111 Plaza Drive Schaumburg, Illinois 60195 (312) 885-0505

INDIANA 2421 Production Drive Suite 202 Indianapolis, Indiana 46241 (317) 248-8306

KENTUCKY 4299 Bardstown Rd Louisville, Kentucky 40218 (502) 491-6595

LOUISIANA 717 S Foster Drive Suite 140 Baton Rouge, Louisiana 70821 (504) 923-0660

MARYLAND Washington D C , Office 1900 Sulphur Spring Road Suite 310 Baltimore, Maryland 21227 (301) 247-8900

MASSACHUSETTS 810 Memorial Drive Cambridge. Massachusetts 02138 (617) 661-7710 1500 Main Street Bay State West Suite 1820 Springfield. Massachusetts 01103 (413) 739-9880 888 Worcester Road Wellestey. Massachusetts 02181 (617) 735-8171 Mechanica Bank Tower Suite 640 Worcester. Massachusetts 01608 (617) 754-3096

MICHIGAN Detroit Office 1 Northland Drive Building Suite 366 16900 West Eight Mile Road Southfield, Michigan 48075 (313) 569-0200

MINNESOTA 2850 Metro Drive Minneapolis, Minnesola 55420 (612) 854-7727

MISSOURI 4520 Madison Avenue Suite 210 Kansas City, Missouri 64111 (616) 531-1326 St Louis Office 11854 Lakiand Rd Crave Couer, Missouri 63141 (314) 726-0811

NEW HAMPSHIRE 491 Amherst Sireet Nashua, New Hampshire 03060 (603) 889-8524

NEW JERSEY 1013 Annapolis Drive Cherry Hill, New Jersey 08003 30 Galesi Drive Wayne, New Jersey 07470 (201) 785-3910 NEVADA

Las Vegas Office 3355 W Spring Mountain Rd. No 54 Las Vegas, Nevada 89103 NEW MEXICO 2801 Wyoming, N E.

Suite A Albuquerque, New Mexico 87112 (505) 294-1418

NEW YORK 3527 Harlem Road Bulfalo, New York 14200 (716) 835-3710 12 Avis Drive Guptill Industrial Park Office Bldg. Latham, New York 12110 (518) 783-3101 150 Broad Hollow Road Third Floor Melville, New York 11746 (516) 427-0311 L141 Meadowbrook Court Newfield, New York 14867 (607) 272-9440 144 Fast 44th Street New York, New York 10017 (212) 557-1122 625 Panorama Trail Rochester, New York 14625 (716) 385-2000 104 Pickard Drive Syracuse, New York 13211 (315) 455-1525 NORTH CAROLINA 2 Fairview Plaza

2 Painteev Faza 5950 Fainteev Road Charlotte, North Carolina 28210 (810) 521-0570 405 Parkway Drive Greensboro, North Carolina 27401 (919) 378-9401 OHIO Columbus Office

Columbus Otto P.O. Box 29292 Columbus, Ohio 43229 (614) 802-1039 1161 Lyons Road Building E Dayton, Ohio 45459 (573) 435-1932 Claveland Office 26250 Euclid Avenue Suite 925 Euclid, Ohio 41132 (216) 289-2660

OKLAHOMA 6161 North May Avenue Suite 39W Oklahoma City, Oklahoma 73112 (405) 840-3891 9726 E 42nd South

Suite 200 Tulsa, Oklahoma 74145 (918) 564-8530

OREGON 4614 S W Kelly Portland, Oregon 97201 (503) 223-7150

PENNSYLVANIA Philadelphia Olfice Dublin Hall, 4th Floor 1777 Walton Road Blue Bell, Pennsylvania 19422 (2151 643-5515 Carnegie Office Park 600 Bell Avenue Building 100 Carnegie, Pennsylvania 15106 (412) 279-3500

#### RHODE ISLAND

225 Newman Avenue Rumford, Rhode Island 02916 (401) 438-0001

#### TENNESSEE

1515 East Magnolia Avenue Mamilton East Building Stuite 130 Knozville Tennessee 37917 (615) 524-1841 1355 Lynnlield Road Suite 221 Bidg B Memphis. Tennessee 38138 (901) 761-3366

#### TEXAS

111 West Anderson Lane Suite 301 Auslin, Texas 78752 (512) 456-4201 4450 Sigma Road Suite 130 Dallas Texas 75240 (214) 233-4496 3101 Fierro El Paso, Texas 70935 4949 W 34th Street Suite 123 Houston, Texas 77092 (713) 688-8641 UTAH 3644 West 2100 South Salt Lake City, Ulah 84120 (601) 972-1338

1757 Old Meadow Road McLean, Virginia 22101 (703) 893-0910 5 Koper Executive Center Suite 202 Norfolk, Virginia 23502 (804) 481-0933 5001 W Broad Street Suite 209 Richmond, Virginia 23230 (804) 288-1675 417 Apersen Road Salem, Virginia 24153 (703) 389-8155

WASHINGTON Seattle Office

Suite 107 10604 N E. 38th Place Ouad 1 North Kirkland, Washington 98033 (206) 827-0503

WISCONSIN N81, W12920 Leon Road Suite 105 Menomonee Falla, Wisconsin 53051 (414) 255-3230

Data General Data General Corporation, Westboro, Massachusetts 01581

# DATA GENERAL INTERNATIONAL OFFICES

#### **INTERNATIONAL OFFICES**

CANADA

415 Horner Road Toronto, Ontario MBW 4W3 (416) 259-4271 610-492-2553 TWX 438 Isebey St. Laurent, Montreel (514) 342-5730 610-421-4758 TWX 210 Gladstone Ave Suite 2003 Ottawa, Onlano K29 OY6 (613) 563-1121 610-562-8536 TWX 1020G Shellbridge Way Richmond V6X 2W7, B C (604) 273-2711 610-923-5080 TWX 5923 3rd Street S.E. Calgary, Alberta (403) 253-8427 610-821-2473 TWX 610 10339 - 124 Street Edmonton, Alberta (403) 482-3443 610-831-1240 TWX

#### AUSTRALIA

Melbourne Office 96 Camberwell Road P.O. Box 447 East Hewthorn, Victoria 3123 (03) 821361 790-33041 TLX Perth Office 43 Ventnor Avenue West Perth, W. Australia 6000 092-215981 790-92093 TLX Sydney Office P.O Box 117 40 Yeo Street Neutral Bay Junction N S W. 2089 (02) 9081366 790-25046 TWX Brisbane Office 67 St Paul's Terrace Springhill, Oueensland 4000 (07) 229-5942 790-40159 TWX

#### NEW ZEALAND

Suite B, Level 13 William City Center Planmer Steps Wellington, New Zestand 723-095 791-31002 TLX

#### **EUROPEAN SUBSIDIARIES**

AUSTRIA Gesellschfat M B H Gottfried Keller Gasse 2 1030 Vienna, Austria (222) 73-4566/53 847-74559 TLX

#### BELGIUM

Data General, SA Vorstlaan 191-197 Bus 111 Boulevard du Souverair Brussels 1160 Brussels, Belgum (02) 660-49-44 61206 TLX

#### FRANCE

15, Rue te Sueur 75116-Paris, France 1-500-06-06-500-98-18 610-289 TLX La Boursidiere, RN 186 Immeuble MB P 78 Route Nationale 186 92350-Le Piessis Robinson, France (1) 830-21-05 200143 TLX 105-107 Rue De Crequi 69006 Lyon, France (78) 5284-21 842-38-130 TLX

#### GERMANY

Data General, GMBH Frankfurter Allee 27 6236 Eschborn W. Germany 6196-48868 841-417434 TLX Niederlassung West 403 Ratingen, Germany Borsigstrasse 12 (2012) 46011/12 8-585-271 TLX Nederlassung Hamburg Kleine Bahnstrasse 10 2 Hamburg 54, West Germany (40) 850-50-26 212448 TLX Prinzregentenstrasse 54/IV 8000-Munich, West Germany 089-223833 841-524079 TLX Talatrasse 172 D-7024 Filderstadt 1 711-702061 ITALY Data General S.P.A Via Morigi, 3/A 20123 Milano, Italy 866-046 843-33243 TLX Data General S.P.A. Via Vincenzo Lissani 90 1-00151 Roma (06) 5236691

Deta General Holland, BV Van Gijnstraat 17 Rejawijk Z.H. The Netherlanda (70) 907-694 844-33545 TLX

NETHERLANDS

#### SWEDEN

Deta General, Sweden AB Industrivagen 20 5-17148 Soina, Stockholm 8-83-4000 854-10089 TLX Doktor Forselius Gata 1 5-42326 Gothenburg 31-81-31-90 Cartsgatan 54 5-211 20 Melmoe 30-10-35-85

#### SWITZERLAND Deta General A.G Badenerstrasse 567 8048-Zurich, Switzerland 1-54-17-82 845-56437 TLX Avenue de Valmont 12 CH 1010 Lausanne, Switzerland 021-33-33-40 r 35

26105 TLX

UNITED KINGDOM London Office Westway House 320 Ruislip Road East Greenford Middlesex, England 1-578-9231 851-935364 TLX Manchester Office Nelson House, Park Road Timperley, NR Altrincham Cheshire, England (61) 969-3935/9 667903 TLX Swan Office Centre 1508/8 Coventry Road Yardley Birmingham, England 8258AD 021-707-3433 851-339392 TLX SCOTLAND Hellenic House, 2nd FL 87-97 Bath Street Glasgow G2 2EE Scolland, UK 41-332-3205 851-779258 TLX SOUTH AMERICA Caixa Postal 673 Sao Paulo 04559, So, Brazil 543-0138 1122336 EVAM BR TLX MIDDLE EAST Data General Greece 260 Syngrou Avenue Athens, Greece 958-0845 21/8708 TLX ARGENTINA

Compucorp Calculadores Y Sistemas, S.A. Bartolome Mirte 2480, Piao 1 Buenos Aires Republica Argenlina 47-0065, 47-0066, 47-2224 CCSSA-BA 2029 AR TLX COLOMBIA

MBB Companhia Lida. Carrera 7 N 81-26 APDO Aereo 90670 Bogata, Colombia 369-565

COSTA RICA Sistemas Analiticos, SA Apartado 6244 San Jose, Costa Rica 22-81-56 2481 TLX FEGOR

ECUADOR Siatemas Andlinos S.A. P.O. Box 4560-A Quilo Ecuador 521-875, 230-593 2393 Bazoas ED TLX

EGYPT T E A. Computers 2 Maarul Street P.O. Box 1901 Cairo, Egypt 55685, 40077 Cable Teamincomp 2478 Teacom Un. TLX

PINLAND & U.S.S.R. Oy Stromberg AB P O Box 118 SF 00101 Helsinki 10, Finland 55-00-45 122960 TLX

#### GREECE

Corais S A. 10 Stadiou Street Athens 133, Greece 32-33714 55-28 TLX

#### HONG KONG

Dataprep (HK), Ltd. 14th Floor, Block B Walson's Estate Hong Kong, B C.C. 5-717-231 780-73184 TLX

#### IRAN

Datiran Corporation No 9 Eleventh Street Miremad Avenue Taknite Tavoos Avenue Tehran 15 Iran 215-308 MOOXIR

ISRAEL TEAM Computers Ltd. 14 Heh Iyar Street Kikar Hamedina Tei Aviv, Israet (03) 256-819, 256-886, 262-580 341491 TLX

#### JAPAN

Nippon Mini-Computer Corporation Trade Dept. Tohyo Bidg. 6-12-20 Jingumae Shibuya, Tokyo (03) 406-451 781-242-5071 TLX

#### KOREA

M-C International (Korea) Ltd. CPO Box 1355 Seoul, Korea 23-410/5 K24228 Emcee Korea Seoul Room 1407 Center Bidg. SO-Kong Dony Seoul, Korea 717 Market St. San Francisco, CA 94103 (415) 397-1455

#### LYBIA

T.E.A. Computers Ben Ahour Street P.O. Box 4494 Tripoly, Lybis 37283 Handiskawi Tripoly Lybis (Cable)

#### MALAYSIA

Dataprep (Malaysia) Sendirlan Berhad 6th Floor, Wisma Keng Soon 120 Jalan Pudu Box 2401 Kuala Lumpur 05-03 Malaysia 3-88795 784-30420 TLX

PERU Digita S A.

Los Negocros 240 Surquillo Lima 34 Peru 45-5773, 47-1111 21083 TLX

#### PHILIPPINES

Detaprep (Philippines), Inc. G & S Building 250 Beundia Avenue Makati, Metro, Marrila, Philippines 86-49-51 722-7496 TLX 3968-DPP-PN TLX

# Data General Data General Data General Corporation, Westboro, Massachusetts 01581

Carro, Egypt S6665, 40077 Cable Teamincomp 2478 Teacom Un TL FINLAND & U.S.S.R.

# DATA GENERAL INTERNATIONAL OFFICES

#### EUROPEAN SUBSIDIARIES

PUERTO RICO

Pan American Computer Corporation 1810 Banco Popular Center Hato Rey Puerto Rico 00918 (809) 767-6524

SAUDI ARABIA

**Rola Trading Corporation** P.O. Box 3172 Rivadh Saudi Arabla

#### SINGAPORE

Dataprep (S) PTE Ltd. 2nd Floor, Marina House, Shanton Way Singapore 1 211311 DPREP 786-21249 TLX

#### SOUTH AFRICA

Perseus Computing & Automation, Ltd. Dejong Centre, 2nd Floor 457 Rodericks Road Lynnwood Pretoria, Republic of South Africa 47-27-82 960-30643 TLX Perseus Computing & Automation, Ltd. P O Box 4898 Johannesburg Republic of South Africa 23-6158

#### SPAIN

Madrid Hispano Electonica Information Commendante Zorita 8 Madrid 20, Spain 2346304 & 2344316 831-22404 TLX Figols 27-29 Barcelona - 14, Spain 3218595 & 3219085 Zabalbide, 42 Bilbao-6 Spain 4238309 & 4238062 Navarro Reverter, 2 Valencia-4 Spain 3731297 Sanchoel Sabio, 28 San Sebastian, Spain 462554 URUGUAY

Lumiere S.A. Rincon 531-ESC. 401 Montevideo, Uruguay 90-4774 546-A/B Quesmar LIV TLX

U.S.S.R. Codeorntec 6263 Variel Drive Woodland Hills, CA 91364 213-348-1719 698474 TLX

### OEM's

MEXICO

Maguinas de Informacion S.A. Insegentes SUV No 1722-202 Mexico 20 D.F. 524-9195 PORTUGAL Equipamentos de Laboratorio, Ltd.

P.O Box 1100 Lisbon, Portugal 976551 832-12702 TLX

SRI LANKA (CEYLON) Maliaraja Organization 7 Braybrooke Place Colombo 2 Sri Lanka Cable 1195 Colombo Rendezvous

# TURKEY

Sisag Company Ltd. CINNAH-CD, No. 5 Ankara, Turkey

#### MANUFACTURING SUBSIDIARIES

HONG KONG Data General Hong Kong, Ltd. Kalser Estates, 5th Floor Man Yue Street Hung Hom Kowloon Hong Kong K-634381-4 THAILAND

Oata General Thalland, Ltd. 2189 New Petchburi Road Bangkok Thailand 916357

•

# microNOVA INTEGRATED CIRCUITS DATA MANUAL INDEX

1 . . . . . .

# INDEX

| Ove   | view of microNOVA Line Integrated Circuits |                    |

|-------|--------------------------------------------|--------------------|

| mN601 | 16-Bit Microprocessor                      | 12                 |

| mN603 | I/O Controller                             | £3                 |

| mN606 | 4K Dynamic Random Access Memory            | 14                 |

| mN50  | 6 Quad Sense Amp/Bus Driver                | 15                 |

| mN62  | 9 CPU I/O Transceiver                      | <b>86</b>          |

| mN63  | 4 Memory Transceiver                       | 17/                |

| mN63  | 6 IOC I/O Transceiver                      | [8]                |

| mN63  | 8 Memory Clock Driver                      | <b>8</b> 9 <b></b> |

| mN64  | 0 CPU/IOC Clock Driver                     | <b>E</b> 10        |

|       | Design Notes                               | <b>E</b> 11        |

|       | Appendices                                 | <b>1</b> 2         |

Data General Corporation, Westboro, Massachusetts 01581

.

# OVERVIEW OF microNOVA LINE INTEGRATED CIRCUITS

----

# **OVERVIEW**

### INTRODUCTION

is data manual describes Data General's full microcomputer chip set. The microcomputer consists of three principal egrated circuits: a 16-bit microprocessor, an I/O controller, and a 4Kx1 dynamic RAM. As part of the set, each integrated cuit is supported by the necessary system buffer elements. The principal chips are fabricated with N-channel, silicon gate, etal oxide semiconductor (NMOS) technology. The system buffer chips are small and medium scale integration, bi-polar cuits.

e chip set is designed to implement high-performance microcomputer or controller systems. It incorporates Data General's werful NOVA line minicomputer instruction set and 16-bit central processing unit (CPU) architecture.

croNOVA line integrated circuits are available on an individual basis as well as in full microcomputer chip sets. In addition, the croNOVA family includes the following supporting hardware.

- CPU boards

- RAM memory boards

- programmable read-only memory boards

- asynchronous interface boards

- general purpose I/O boards

- power supply

- hand-held console

- card cages

- a variety of peripheral devices; such as:

- video displays

- hard copy data terminals

- single and dual diskette sub-systems

- line printers

- paper tape reader

e microNOVA family comes with proven Data General development and runtime software that includes two operating systems, diskette-based Disc Operating System (DOS) and the Real-Time Operating System (RTOS). Software developed for Data neral's NOVA line minicomputers can be easily reassembled for use with microNOVA systems. The operating systems oport two high level language compilers, FORTRAN IV and extended BASIC, as well as various utilities, including: a Command e Interpreter, text editor, macro assembler, relocatable loader, a library file editor, and a symbolic debugger.

croNOVA development software is based on the Disc Operating System. The diskette-based DOS provides a smooth flow ough varying development phases to completed production software. OEMs who need a larger development system can utilize NOVA 3 line of minicomputers. NOVA 3 is software-compatible with microNOVA and supports up to 128K words of memory, a peripheral range, and the Real-time Disc Operating System (RDOS).

ta General's Real-Time Operating System is a DOS-compatible runtime executive. It is compact and memory-resident, and a real-time multitask capability for controlling real-time applications. RTOS provides standard interrupt servicing, device adding and execution scheduling functions.

of these features make the microNOVA family ideal for applications like complex instrumentation, industrial automation, nmunications, and data acquisition, where 16-bit NOVA power and precision are required.

ţ

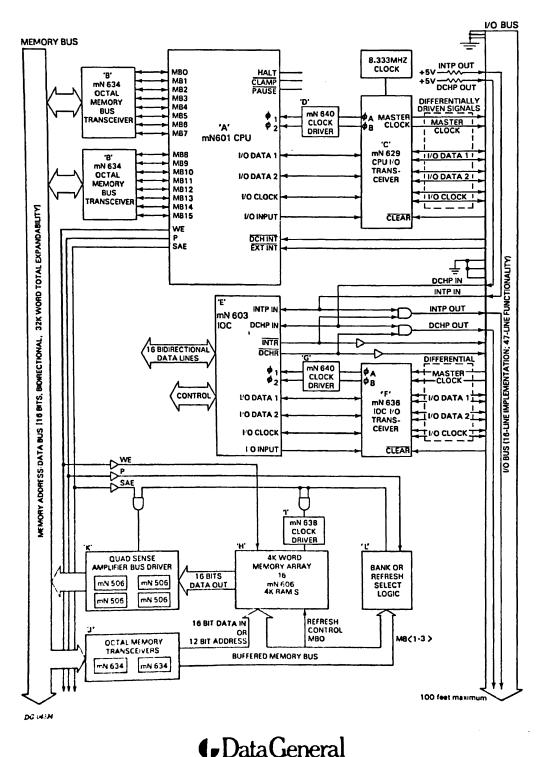

### microNOVA FUNCTIONAL BLOCK DIAGRAM

Data General Corporatant, Westbrary, Massachusetts (858

2

# **OVERVIEW**

.....

### THE CHIP SET

. . . . . . . . . .

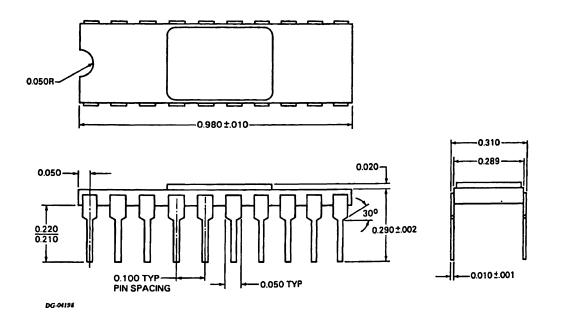

Data General's microcomputer chip set consists of the following dual-in-line packaged (DIP), integrated circuits:

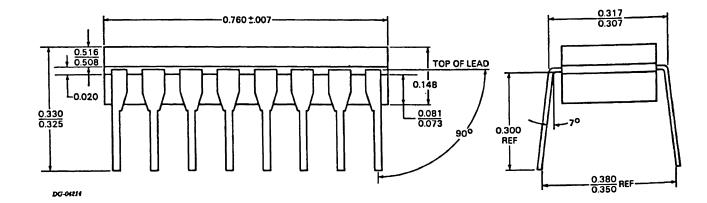

| Integrated Circuit                     | Packaging      |

|----------------------------------------|----------------|

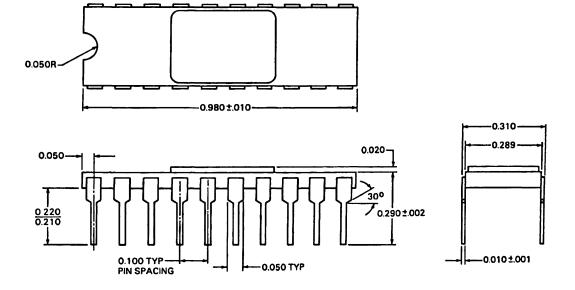

| mN601 16-bit microprocessor            | 40-pin ceramic |

| mN603 I/O controller (IOC)             | 40-pin ceramic |

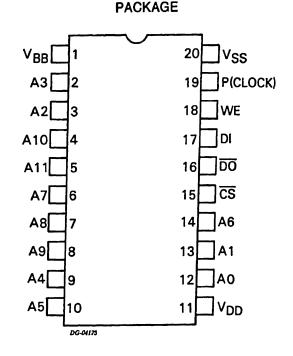

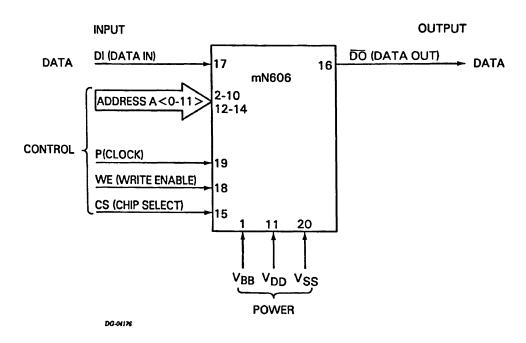

| mN606 4Kx1 dynamic RAM                 | 20-pin plastic |

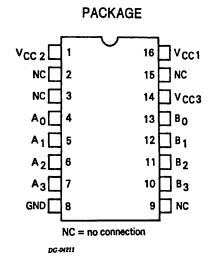

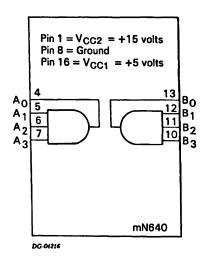

| mN640 CPU and I/O clock driver         | 16-pin cerdip  |

| mN638 memory clock driver              | 16-pin cerdip  |

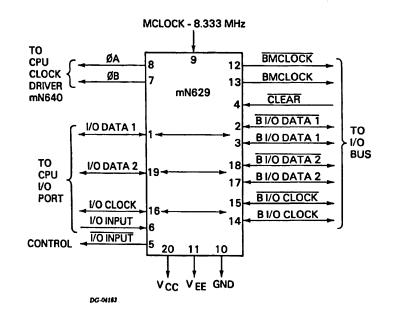

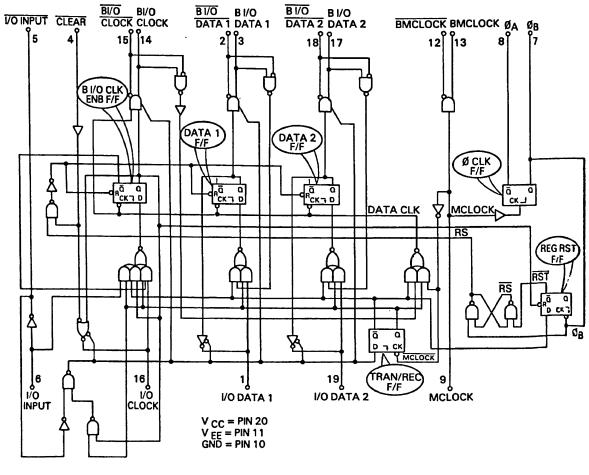

| mN629 CPU I/O transceiver              | 20-pin ceramic |

| mN636 IOC I/O transceiver              | 20-pin ceramic |

| mN634 octal memory transceiver         | 20-pin ceramic |

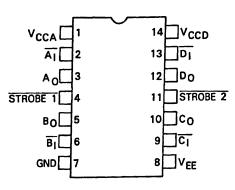

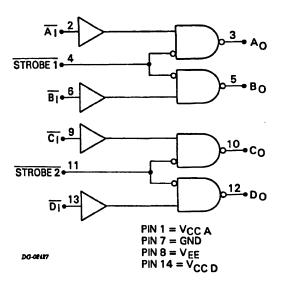

| mN506 quad sense amp/memory bus driver | 14-pin cerdip  |

#### THE MICROCOMPUTER

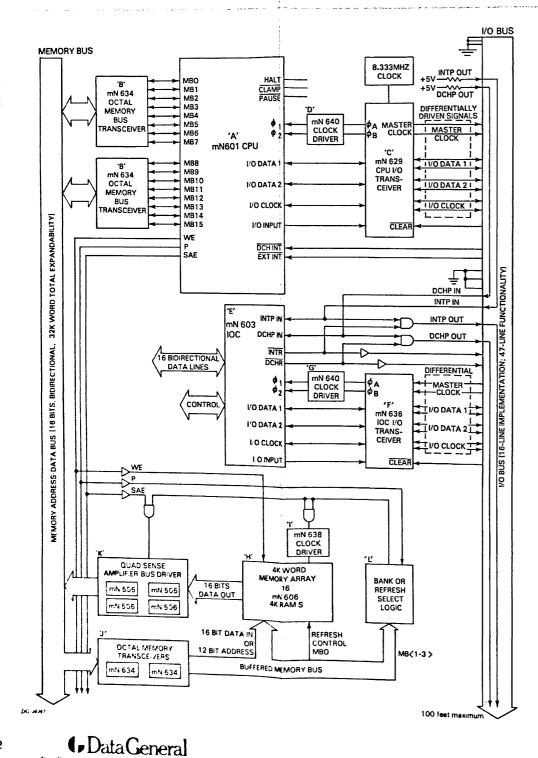

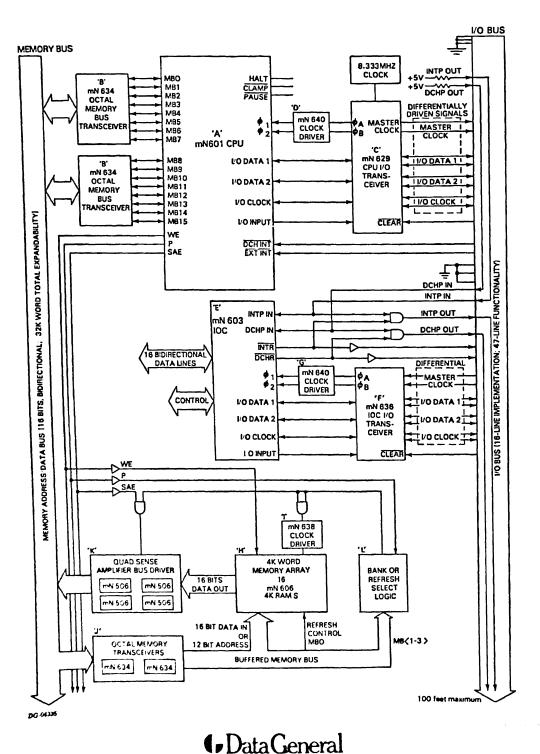

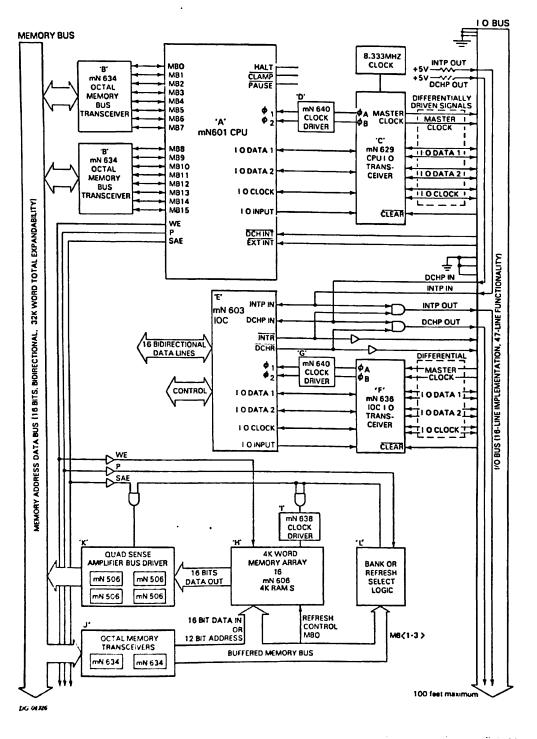

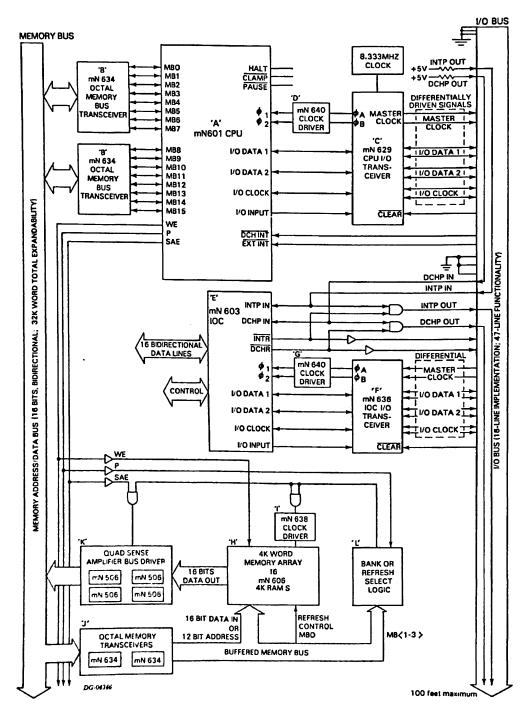

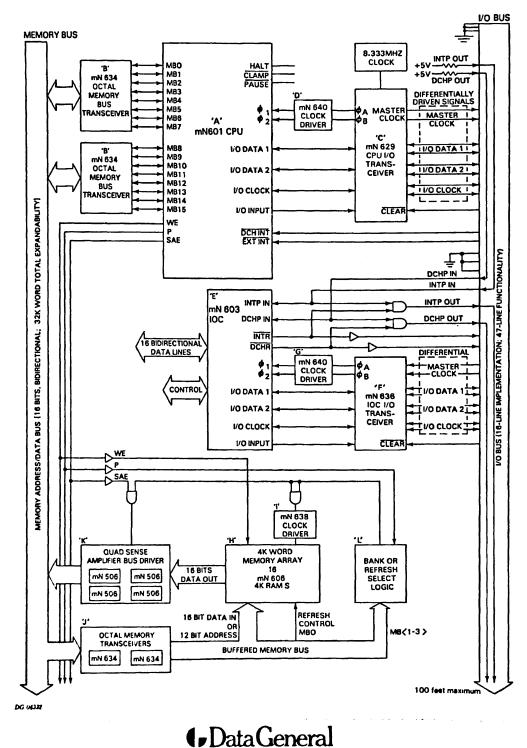

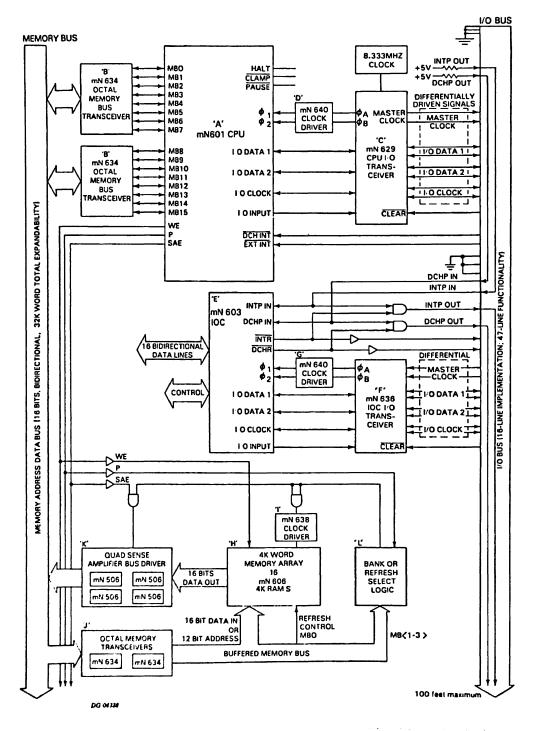

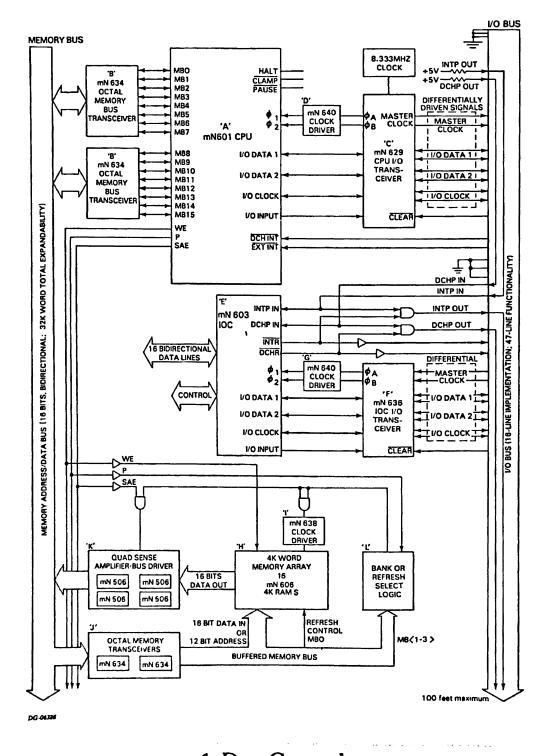

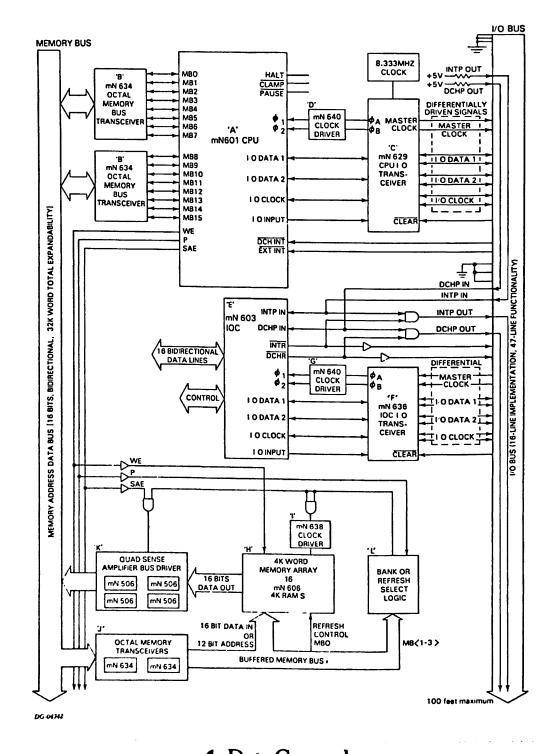

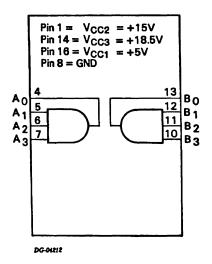

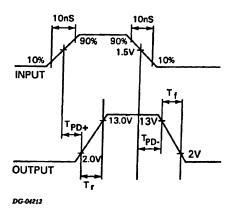

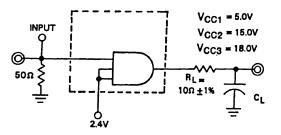

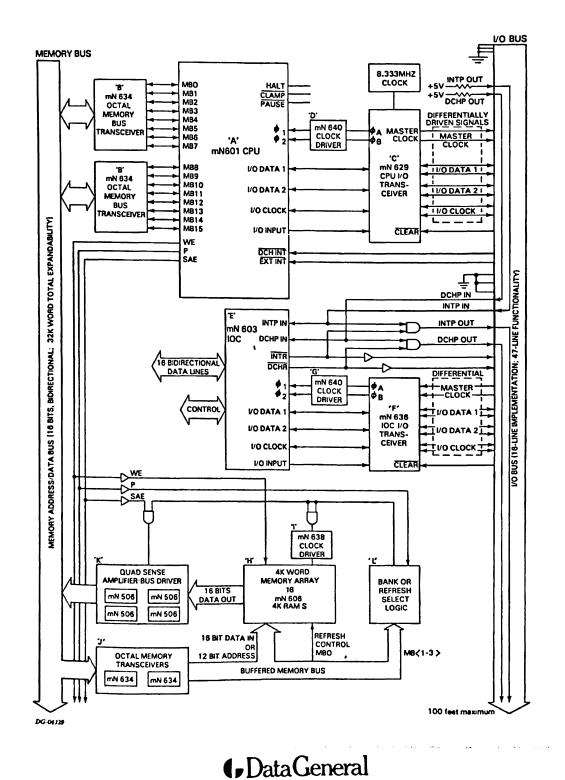

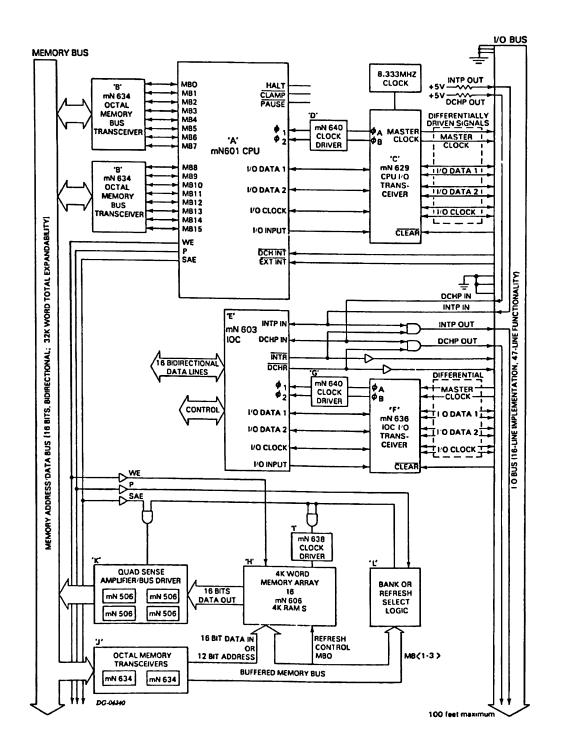

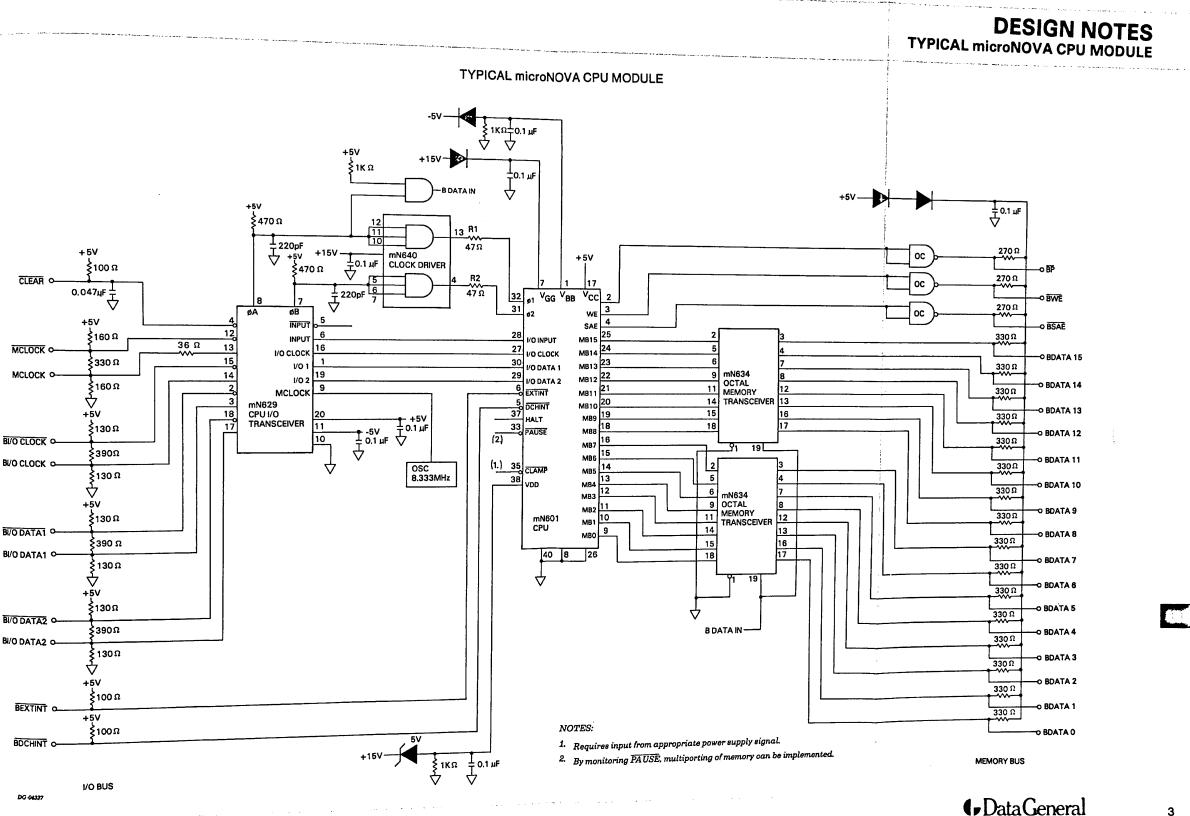

The block diagram on the opposite page shows a recommended microcomputer chip set configuration. It is organized around two data buses: memory and I/O (see diagram).

#### microNOVA MEMORY BUS

Memory addresses and data are passed between the mN601 microprocessor and an array of mN606 RAMs via the microNOVA memory bus. This is a 16-bit parallel, bidirectional, high-speed bus.

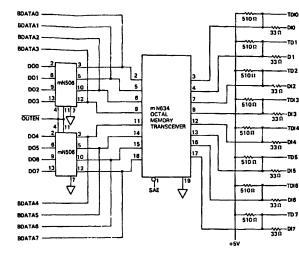

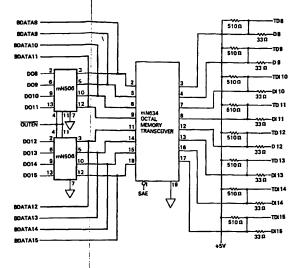

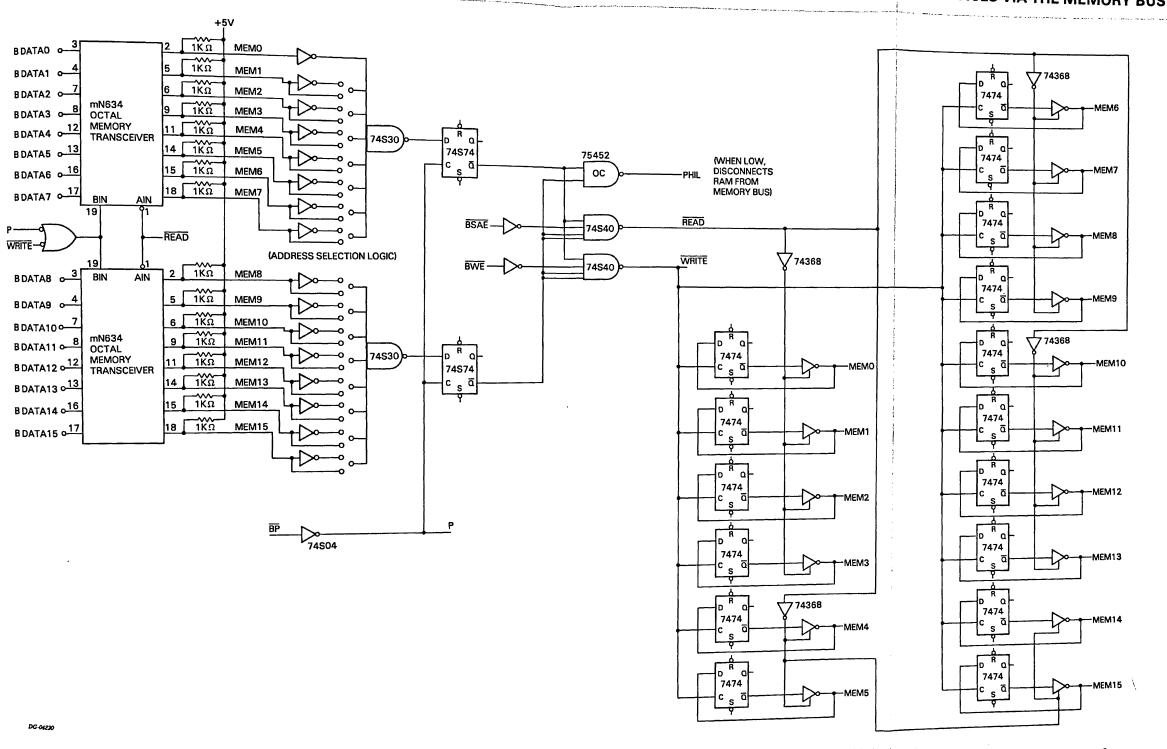

The microprocessor is interfaced to the bus via two mN634 octal memory transceivers. These transceivers drive data between the CPU's memory address/data lines and the memory bus.

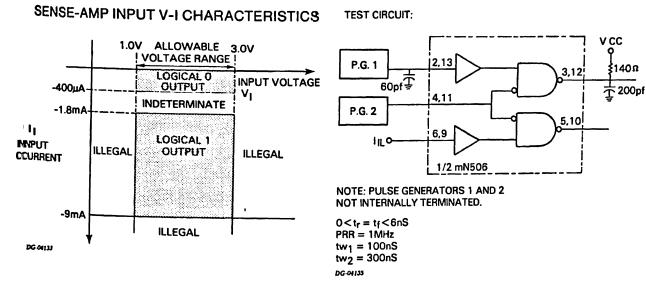

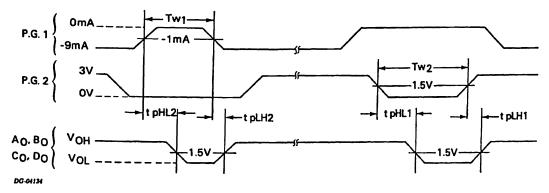

A RAM grouping is interfaced to the bus via two mN634 octal memory transceivers and four mN506 quad sense amp/bus drivers. The memory transceivers drive both addresses and data sent to memory via the bus onto the RAM input lines while the sense amp/bus drivers drivers drive data from the RAM output lines onto the bus.

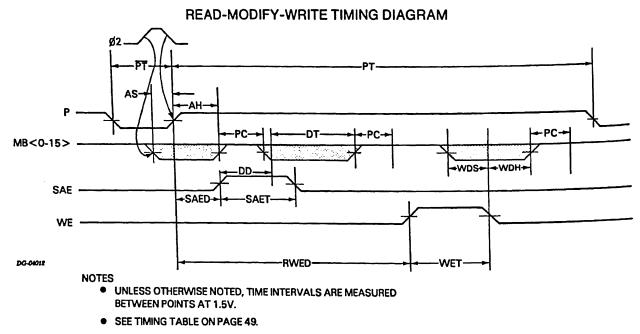

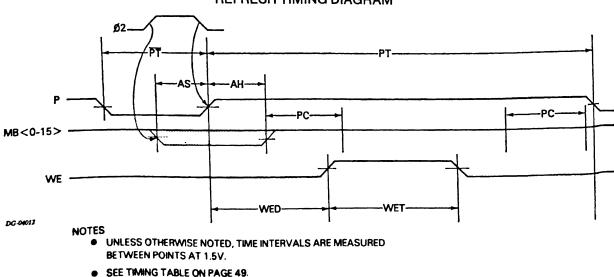

Three memory control lines, P, SAE and WE, allow the microprocessor to perform four kinds of memory operations: read, write, read-modify-write and refresh.

#### microNOVA I/O BUS

• • • ·

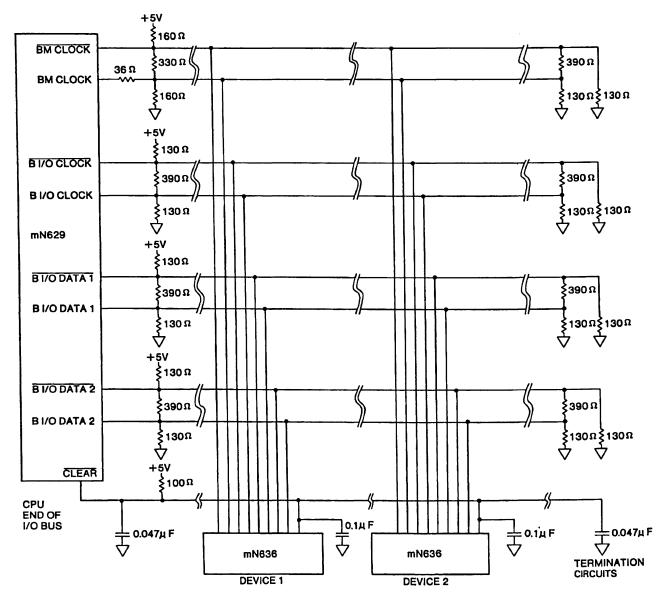

Information is passed between the mN601 microprocessor and mN603 I/O controllers via the bidirectional, microNOVA I/O bus. This bus combines the advantages of high speed with high noise immunity (due to its differential nature, described below), while permitting the use of low cost ribbon cable. The I/O bus can be extended to a maximum distance of 100 feet from the microprocessor.

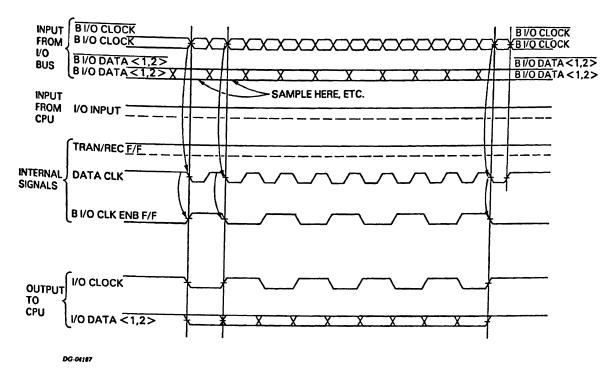

The microNOVA I/O bus contains 16 lines. The most critical lines (two serial data lines and two clock lines) are differentially driven and received by an mN629 CPU I/O transceiver and one mN636 IOC transceiver per mN603 I/O controller.

At the microprocessor end of the bus, the CPU I/O transceiver receives serial data from the CPU and differentially drives it to the IOC I/O transceiver(s). It also receives the differentially driven data signals from the IOC I/O transceiver(s) and passes the data to the CPU. At the I/O controller end of the bus, each IOC I/O transceiver performs a similar function for its I/O controller. Up to twenty IOC I/O transceivers can be interfaced to the microNOVA I/O bus.

# **UVERVIEW**

. . . . . .

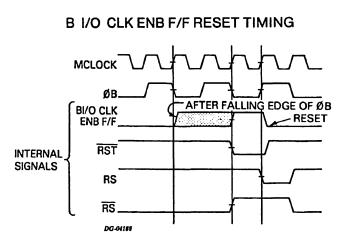

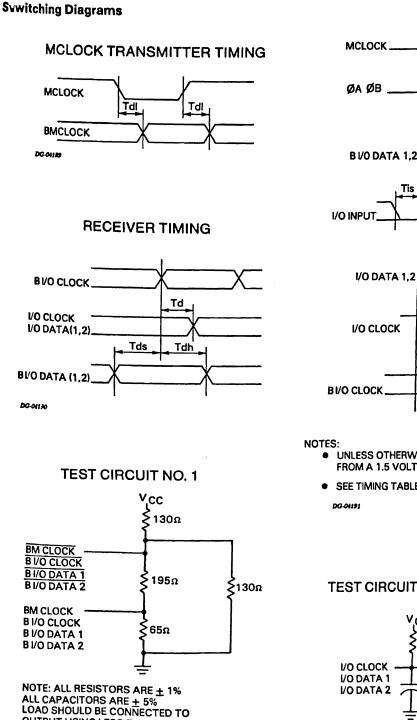

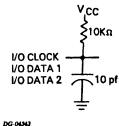

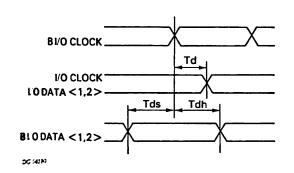

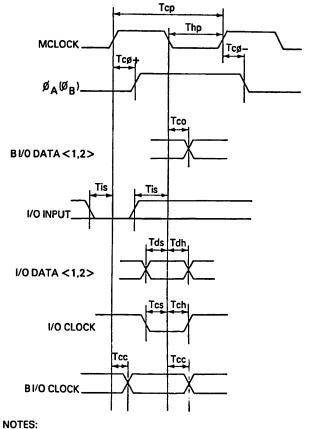

The differentially driven I/O CLOCK (see diagram) is transmitted with the data; it strobes the data into the receiving circuit. The CPU I/O transceiver differentially drives the MASTER CLOCK to all IOC I/O transceivers. Each IOC transceiver passes the MASTER CLOCK to its IOC as two non-overlapping clocks via an mN640 clock driver. The MASTER CLOCK synchronizes the operation of the I/O controllers with the CPU.

للمارية المحمور الإعداد وومعته معتورة لارتقا الورزان والورار والرزار

A system reset line (CLEAR), two device request lines, two types of device priority lines, and three ground lines comprise the remainder of the bus.

The CLEAR line allows the system to be reset by external hardware. When this line is pulled to a low logic level for a period of 10 µsecs,the microcomputer is reset. This time period ensures that the CPU and IOC I/O transceivers are in receive mode; refer to the mN601, mN603, mN629 and mN636 circuit descriptions.

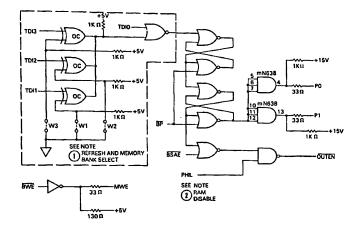

The device request lines (EXTINT and DCHINT) allow I/O devices to request microprocessor service for the purpose of transferring data in either of two modes: programmed I/O or data channel break. These are explained later in the section entitled Data Transfers.

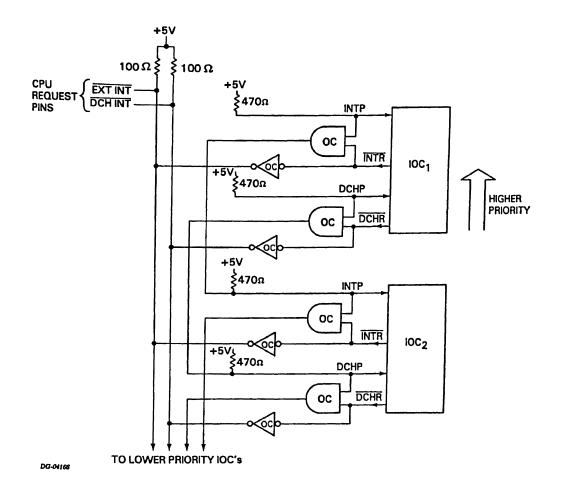

#### Hardware Device Priority Network

The priority lines (INTP OUT, DCHP OUT, INTP IN and DCHP IN) comprise an interdevice daisy chain. When more than one I/O device is requesting service, this network gives priority to the device requesting service that is physically closest on the I/O bus to the microprocessor. The INTP lines control priority between devices requesting interrupt service. Similarly, the DCHP lines control priority between devices.

The manner in which the priority system is implemented is the same for both types of requests. When a device requests service, that device's INTP/DCHP OUT line goes to the low logic level. This removes priority from devices further away from the microprocessor, by pulling their INTP/DCHP IN lines to a low logic level. When the microprocessor acknowledges a request for service, a device can respond only if it is requesting service and its INTP/DCHP IN line is at a high logic level. If it is at a low logic level, it indicates that a higher priority device in the chain is requesting service. The priority lines previously disabled by the service request are reenabled when the responding device clears its request line.

#### mN601 16-BIT MICROPROCESSOR

This is a 16-bit central processing unit (CPU) that incorporates the NOVA architecture. Its internal structure and operations are described in the mN601 section of this manual.

The mN601 is designed to operate with the following system buffer elements: two mN634 octal memory transceivers, an mN629 CPU I/O transceiver and an mN640 clock driver. The primary functions performed by these circuits for the CPU are described below. Detailed information is found in the individual circuit descriptions.

The CPU (designated 'A' in the diagram) has two ports: memory and I/O. Two mN634 octal memory transceivers (designated 'B') drive data between the CPU's memory address/data lines MB(<0-15>) and the microNOVA memory bus. The memory control ignals, P, SAE and WE, allow the CPU to perform four kinds of memory operations: read, write, read-modify-write and refresh.

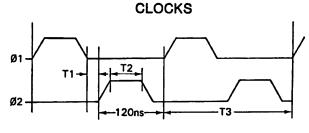

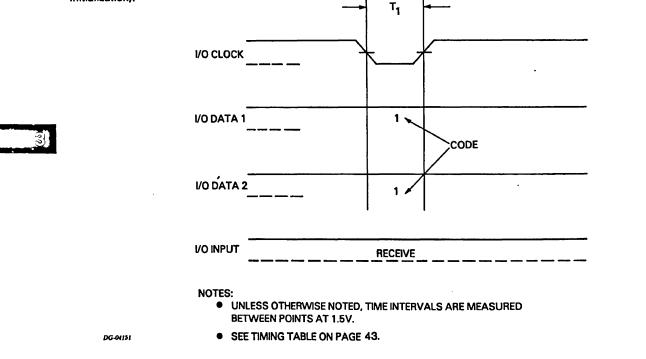

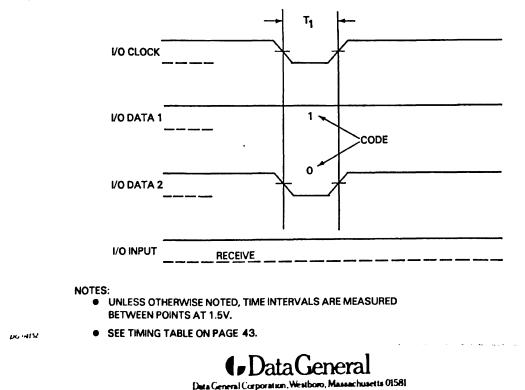

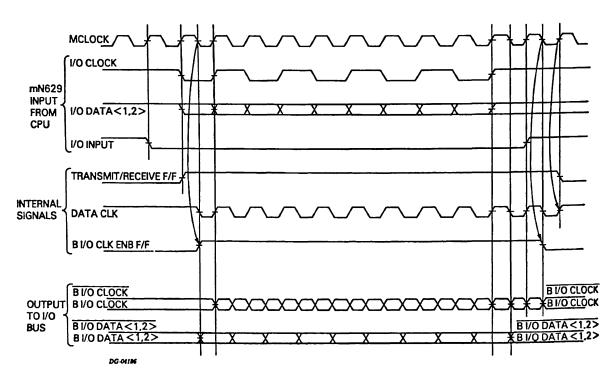

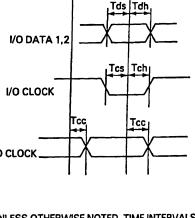

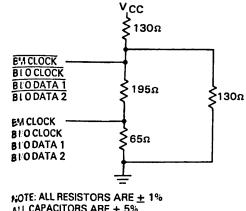

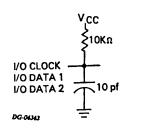

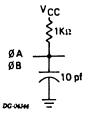

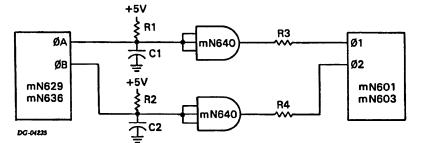

The mN629 CPU I/O transceiver (designated 'C') performs two functions for the CPU. First, it interfaces the CPU's serial data (I/O DATA <1.2>) and data clock (I/O CLOCK) lines with the microNOVA I/O bus. The I/O INPUT signal is used by the CPU to control the transceiver's operating mode, either transmit or receive. Second, the CPU I/O transceiver generates the two non-overlapping system clocks ( $\phi$ A and  $\phi$ B) from a single 8.333MHz clock input.

The  $\phi A$  and  $\phi B$  clocks are shaped by external circuitry (see Design Notes) and the outputs are supplied to the mN640 clock driver (designated 'D'). The clock driver receives these signals and provides signal characteristics that are compatible with the MOS clock input circuits of the CPU,  $\phi 1$  and  $\phi 2$ .

The remaining mN601 pins perform the following functions. The HALT pin reflects the state of the CPU, halted (idling) or performing tasks. The PAUSE pin indicates when the CPU is performing a memory operation. By monitoring the output of this pin, multiporting of memory can be implemented. The CLAMP pin is an input pin used during the power-up and initialization sequence.

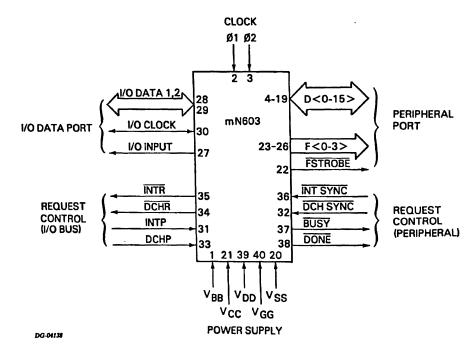

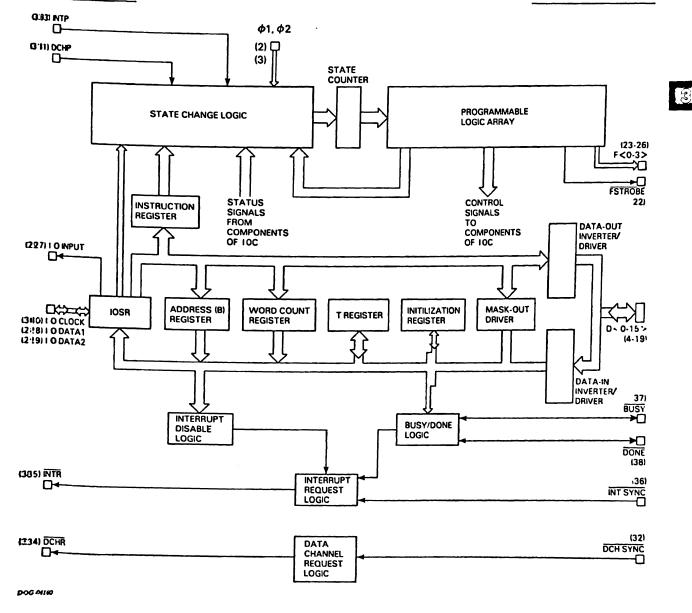

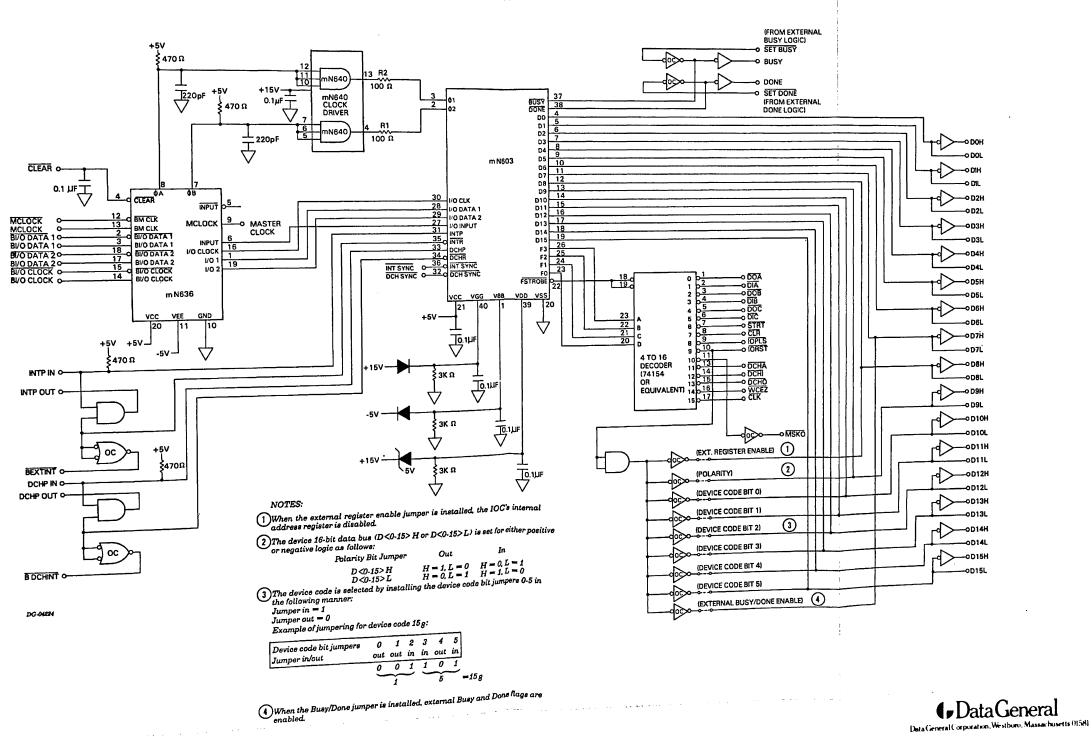

#### mN603 I/O CONTROLLER (IOC)

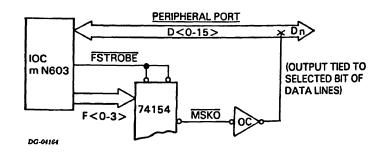

The IOC is the interface between a peripheral device and the microNOVA I/O bus. Details of its internal architecture and operations are contained in the mN603 section of this manual.

It is designed to operate with the following system buffer elements: an mN636 IOC I/O transceiver and an mN640 clock driver. The primary functions performed by these circuits for the IOC are described below. Detailed information is found in the individual circuit descriptions.

The mN603 (designated 'E' in the diagram) has two ports: I/O bus and peripheral.

. .....

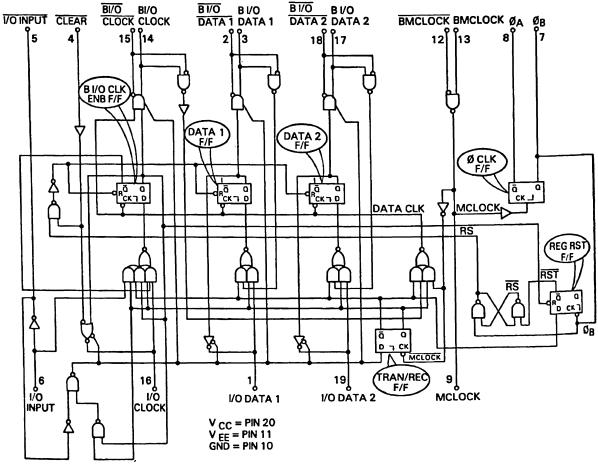

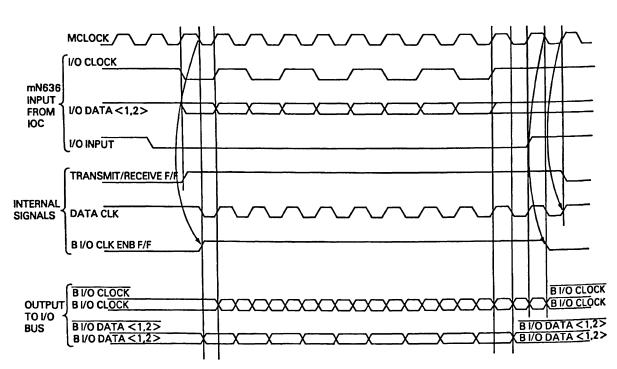

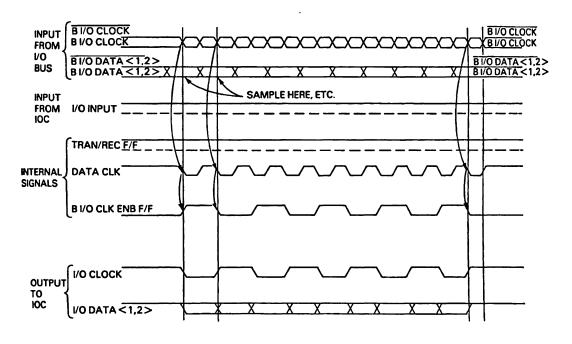

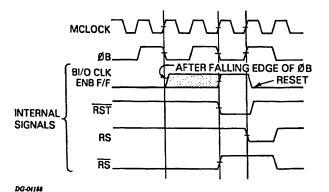

The mN636 IOC I/O transceiver (designated 'F') performs two functions for the IOC. First, it interfaces the IOC's serial data (I/O DATA<1,2>) and data clock (I/O CLOCK) lines with the microNOVA I/O bus. The I/O INPUT signal is used by the IOC to control the transceiver's operating mode, transmit or receive. Second, the mN636 transceiver receives the MASTER CLOCK from the I/O bus and generates two non-overlapping clock signals,  $\phi A$  and  $\phi B$ .

The  $\phi A$  and  $\phi B$  non-overlapping clocks are shaped by external circuitry (see Design Notes) and the outputs are supplied to the mN640 clock driver (designated 'G'). The clock driver receives these signals and provides signal characteristics that are compatible with the MOS clock input circuits of the IOC,  $\phi 1$  and  $\phi 2$ .

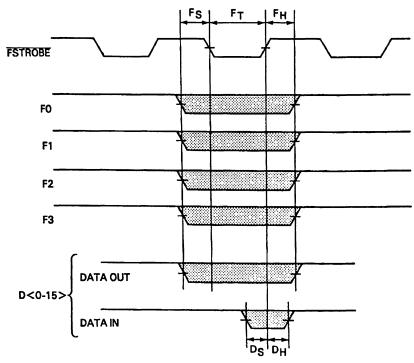

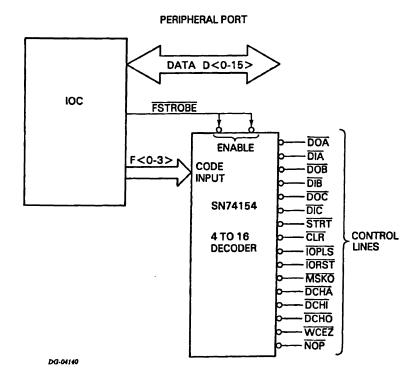

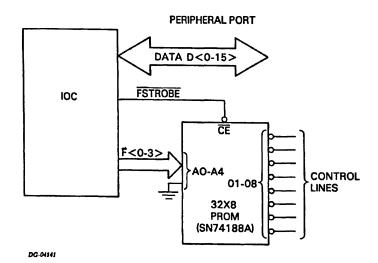

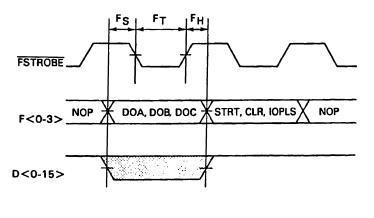

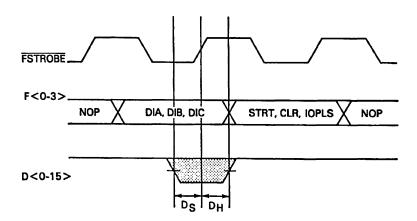

The IOC communicates with the device via a 16-bit parallel data bus and a group of control lines. The data and control lines together create the functional equivalent of the 47-line NOVA I/O bus.

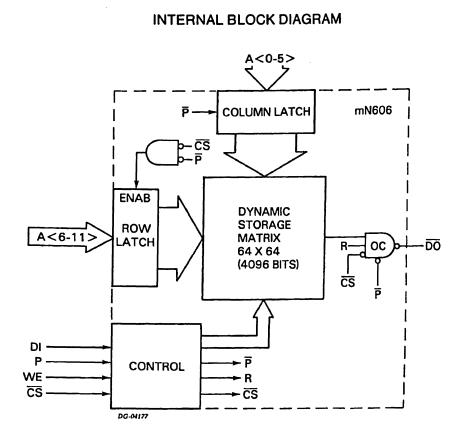

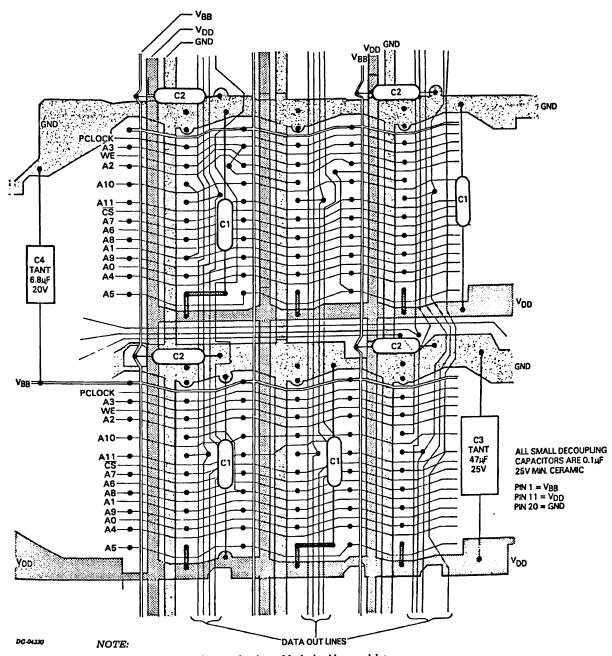

#### mN606 4Kx1 DYNAMIC RAM

This is a 4096 by one bit memory. Details of its internal architecture and operations are contained in the mN606 section of this manual.

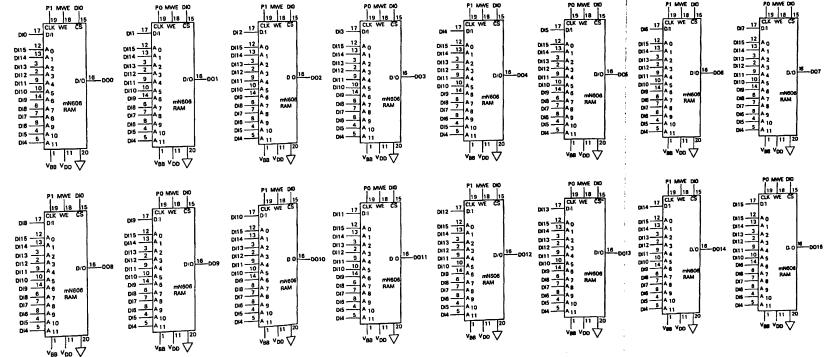

Sixteen mN606 RAMs comprise a 4Kx16-bit memory array. This array is designed to operate with the following system buffer elements: one mN638 clock driver, two mN634 octal memory transceivers and four mN506 quad sense amp/bus drivers. For an 8Kx16-bit array, it is necessary to add only one mN638 clock driver, since the two mN634 transceivers and four mN506 sense amp/bus drivers support 8K of memory. The primary functions performed by these system buffer elements for the mN606 RAMs are described below. Detailed information is found in the individual circuit descriptions.

The 4Kx16-bit dynamic RAM array (designated 'H' in the diagram) has two ports: input (address and data) and output.

The two mN634 octal memory transceivers (designated 'J') drive addresses and data from the microNOVA memory bus onto the RAM address and data input lines. The four mN506 quad sense amp/bus drivers (designated 'K') drive data from the RAM output lines onto the microNOVA memory bus.

The microprocessor addresses up to 32,768 memory locations; thus, eight 4Kx16-bit memory arrays can be interfaced to the microNOVA memory bus. Each 4Kx16-bit array has a 12-bit memory address (MB <4-15>). The external bank select logic (designated 'L') selects the appropriate array from the address appearing on the MB <1-3> lines.

When both the memory control signal P is asserted and the bank select logic is enabled, the mN638 clock driver (designated 'l') provides the signal characteristics required for the MOS clock input circuit of the RAM.

At the beginning of a memory operation, the RAM samples the address and tests the logic level, high or low, of MBO. If MBO is at a high level, the RAM initiates a refresh operation; if it is at a low level, the RAM initiates either a read, write, or read-modify-write operation.

When mN606 dynamic RAMs are used in a microNOVA-based system, the mN601 microprocessor automatically refreshes them without external circuitry.

**OVERVIEW**

# OVERVIEW

### DATA TRANSFERS

.....

and the second second

Addresses and data are transferred between the CPU and memory via the microNOVA memory bus. Control information and data words are transferred between the CPU and 1/O devices via the microNOVA I/O bus.

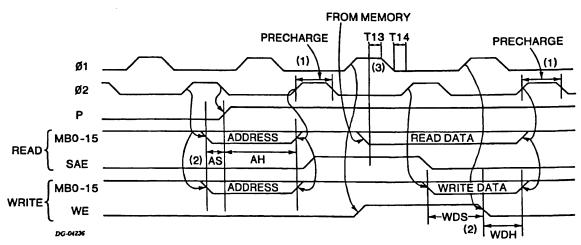

#### MEMORY

The mN601 performs four kinds of memory operations: read, write, read-modify-write and refresh. All memory operations are initiated on the rising edge of P. As described above, the address on the bus is sampled by the memories and the state of MB0 is tested. If this signal is high, a refresh operation is performed; if it is low, either a read, write, or read-modify-write operation is performed. Detailed information is found in the Memory Operations section of the mN601 circuit description.

When non-volatile memory is required, programmable read-only memory (PROM) can be used. Refer to the microNOVA Computer Systems Technical Reference (DGC ordering number 014-000073). At the board level, PROM can overlay RAM, and PROM priority control lines resolve any memory conflicts in favor of the PROM.

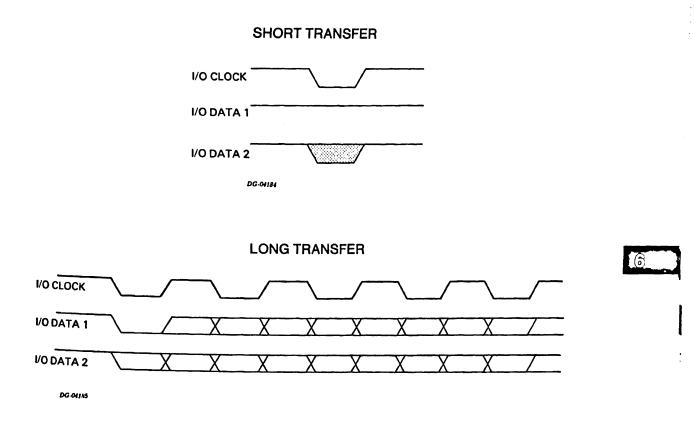

#### **INPUT/OUTPUT**

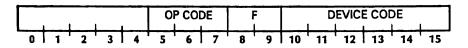

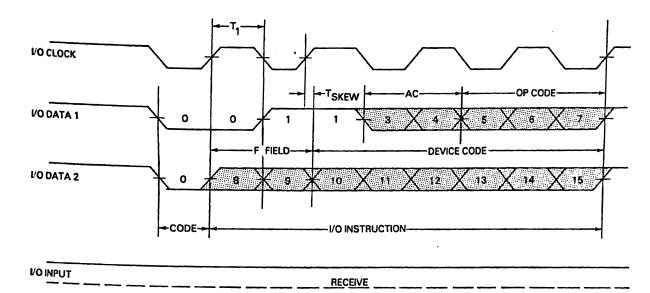

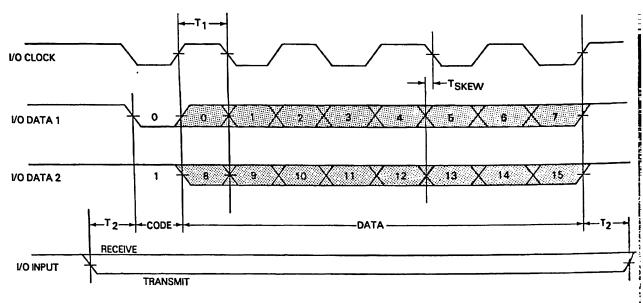

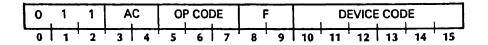

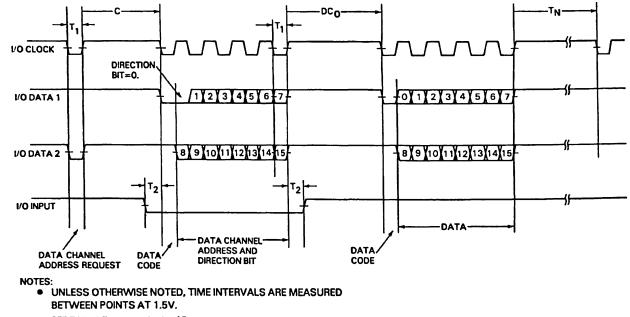

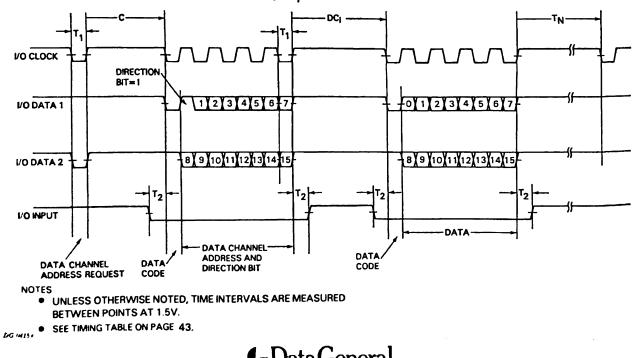

Information is passed between the CPU and I/O controllers via the two serial data lines of the microNOVA I/O bus. The bus connections are made through the appropriate I/O transceivers. The data consists of both control information and 16-bit data words.

The CPU performs I/O data transfers under two operating modes: programmed I/O and data channel break. Under programmed I/O, the CPU moves data between one of its internal registers (namely, accumulators; see mN601 section) and an I/O device. Under data channel break, the CPU moves data between memory and an I/O device. Data channel breaks allow blocks of information to be transferred without altering program flow. In addition, data channel breaks are transparent to the executing program.

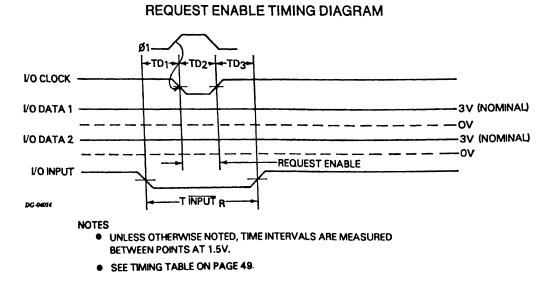

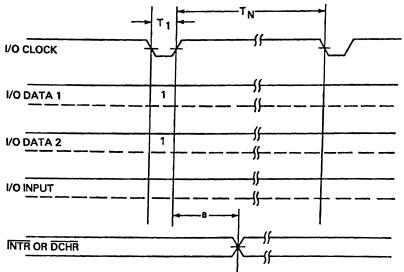

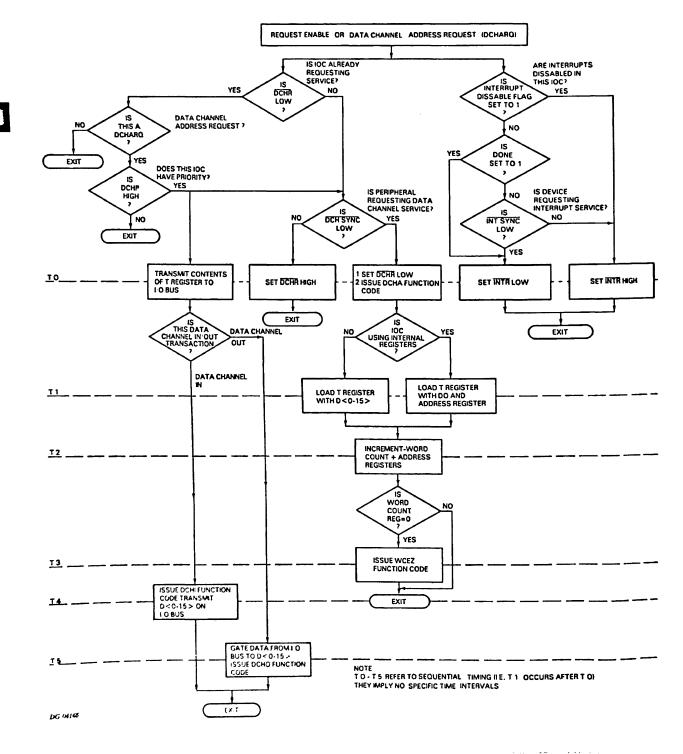

An I/O device requests microprocessor service for the purpose of transferring data by asserting either the program interrupt (EXTINT) or data channel break (DCHINT) device request lines. These requests are synchronized by a CPU-generated signal called Request Enable. It ensures that the device request and priority lines are at a steady state when they are examined by the CPU. Request Enable is sent to all I/O controllers connected to the I/O bus as a two-bit code (11), one bit carried on each serial data line.

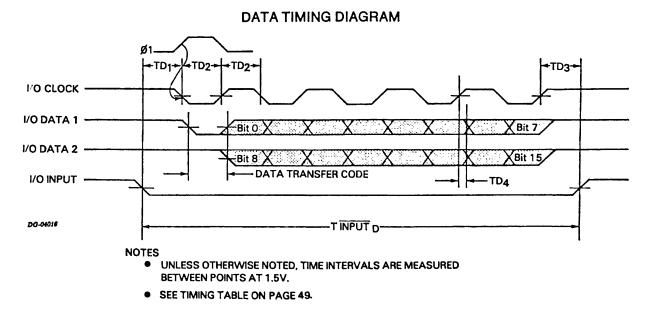

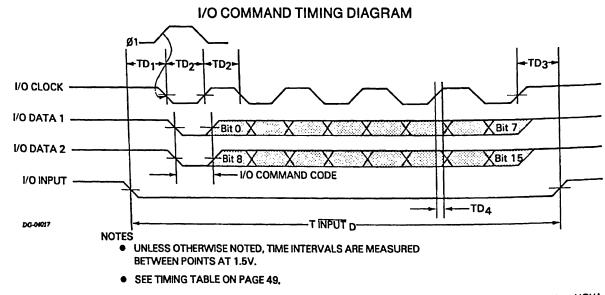

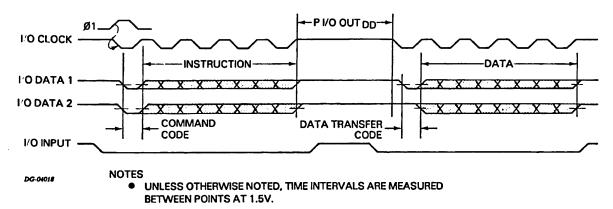

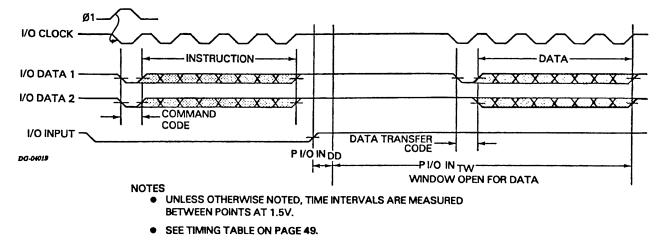

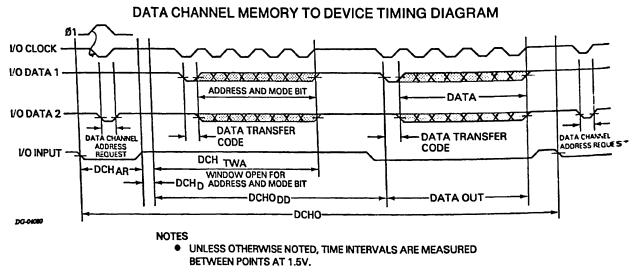

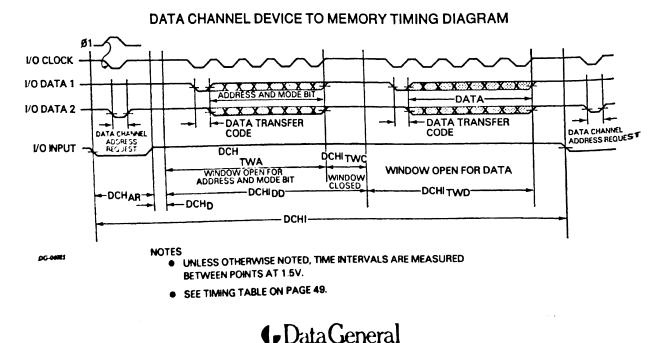

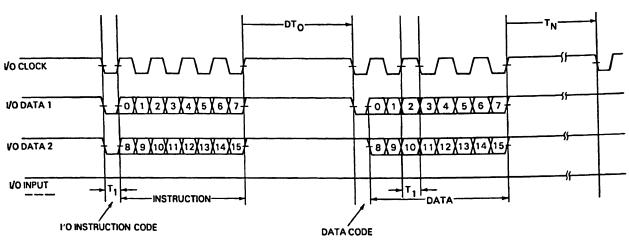

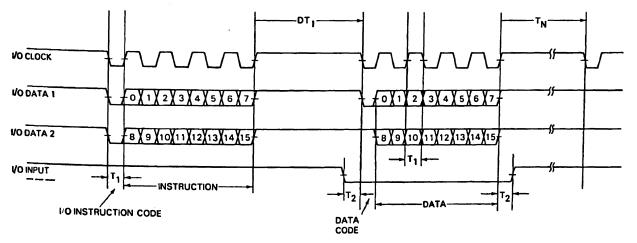

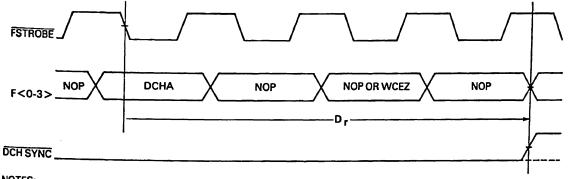

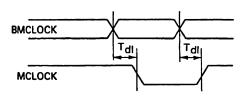

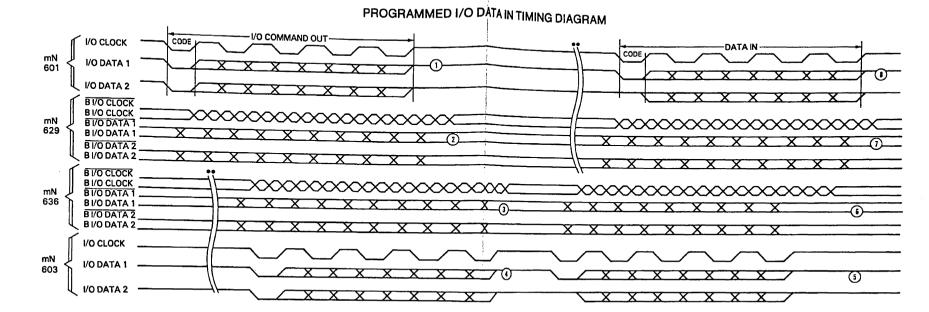

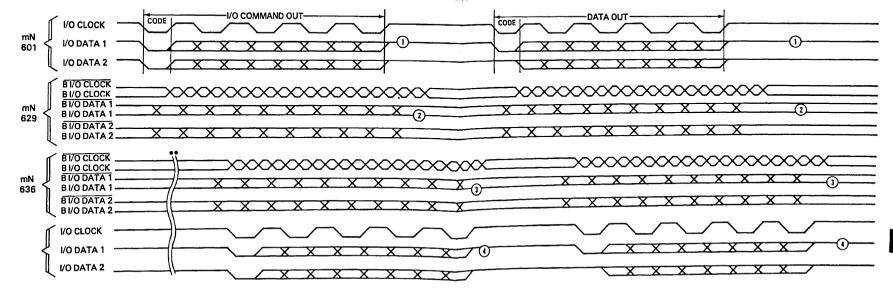

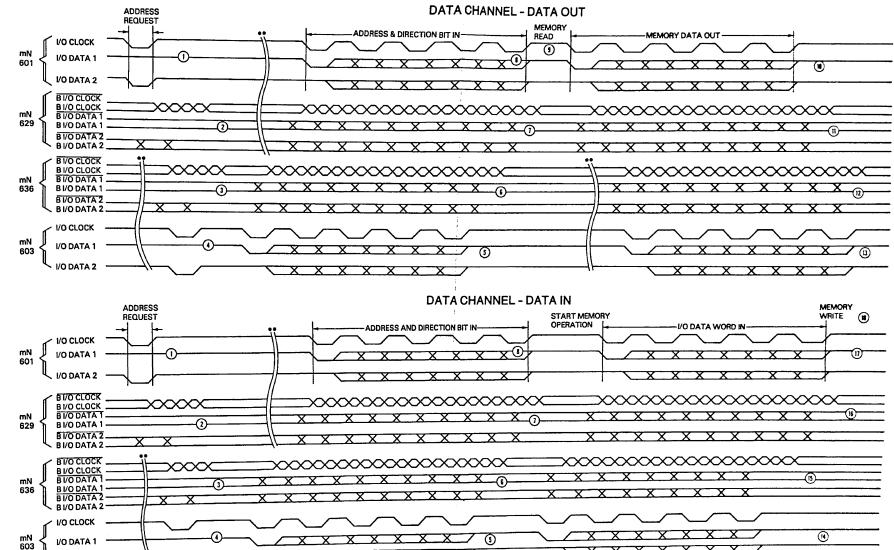

Detailed information concerning I/O data transfers is found in the I/O Operations section of the mN601 circuit description and in the mN603, mN629 and mN636 circuit descriptions. Timing diagrams of I/O bus operations can be seen in Appendix A. These diagrams depict the transmission and reception of control information and data words as they pass between the CPU, the CPU transceiver, the IOC transceiver and the I/O controller, under both programmed I/O and data channel. (The I/O transactions appearing in the diagrams apply when the system is configured as shown in the block diagram at the beginning of this section.)

#### Programmed I/O

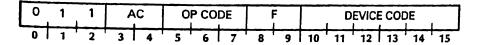

Under programmed I/O, the CPU sends the I/O instruction, exactly as fetched from memory, to all controllers connected to the microNOVA I/O bus. The instruction includes information that identifies the controller to which it is directed. Following the instruction, the CPU performs either a data out operation or a data in operation, as required by the instruction.

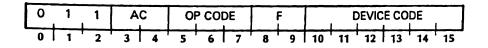

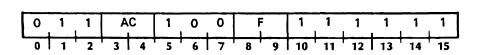

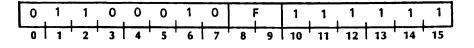

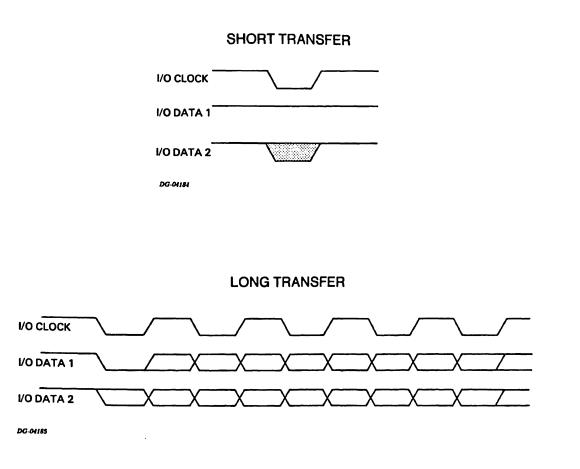

When either data out or data in instructions are performed, both the instruction and the 16-bit data word are transmitted as 18-bits, 9 bits on each line. The first bit on each line comprises a two-bit code that identifies the type of transfer; 00 indicates an I/O command and 01 indicates a data word.

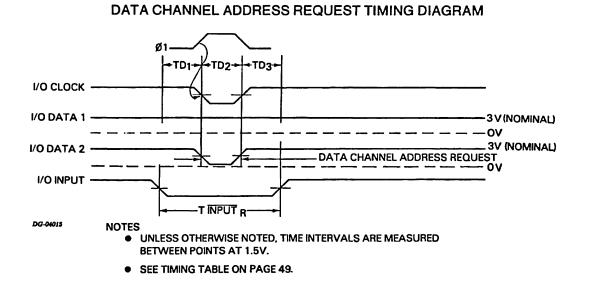

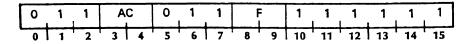

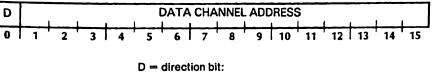

#### **Data Channel Break**

When the CPU performs a data channel break, it sends an address request to the microNOVA I/O bus. This request consists of a two-bit code (10). The highest priority device requesting data channel service responds to this code. The device responds first by sending a 16-bit word (plus the two-bit data word prefix code, 01, described above) containing a 15-bit memory address and a direction of transfer bit (data out or data in) to the CPU. Following the receipt of this information, the CPU initiates a memory operation at the address specified; then, it examines the direction of transfer bit.

If it is set for a data out, the CPU transmits the 16-bit word received during the read portion of the memory operation together with the two-bit data word prefix code. The memory operation is terminated without altering the contents of the addressed location.

If it is set for a data in, the device transmits the 16-bit word to be entered in memory together with the two-bit data word prefix code. After the data word is received by the CPU, it is written into memory during the write portion of the memory operation in progress.

### **RELATED DOCUMENTS**

The following supporting documents are available from Data General Corporation.

|                                  | Ordering No. |

|----------------------------------|--------------|

| microNOVA Programmer's Reference | 015-000050   |

| microNOVA DTOS                   | 015-000059   |

| microNOVA Computer Systems       | 014-000073   |

# mN601 16-BIT MICROPROCESSOR CONTENTS

1

mN601 CONTENTS

. . . . . . . . . .

. . . .

| 1  | FEATURES                                        |

|----|-------------------------------------------------|

| 1  | GENERAL DESCRIPTION                             |

| 2  | PIN DESCRIPTIONS                                |

| 4  | ARCHITECTURE                                    |

| -  |                                                 |

| 6  | INSTRUCTION SET                                 |

| 7  | MEMORY REFERENCE INSTRUCTIONS                   |

| 7  | Addressing Modes                                |

| 8  | INDIRECT ADDRESSING                             |

| 9  | AUTO-INCREMENTING/DECREMENTING                  |

| 11 | No-Accumulator-Effective Address Instructions   |

| 11 | One Accumulator-Effective Address Instructions  |

| 12 | TRAP INSTRUCTION                                |

| 13 | ARITHMETIC/LOGICAL INSTRUCTIONS                 |

| 15 | Two Accumulator-Multiple Operation Instructions |

| 17 | Multiply/Divide Instructions                    |

| 18 | STACK INSTRUCTIONS                              |

| 23 | INPUT/OUTPUT INSTRUCTIONS                       |

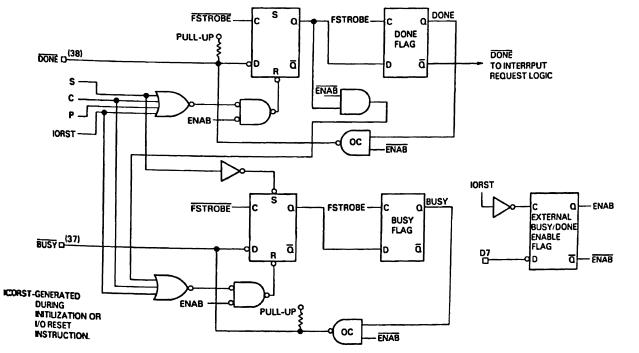

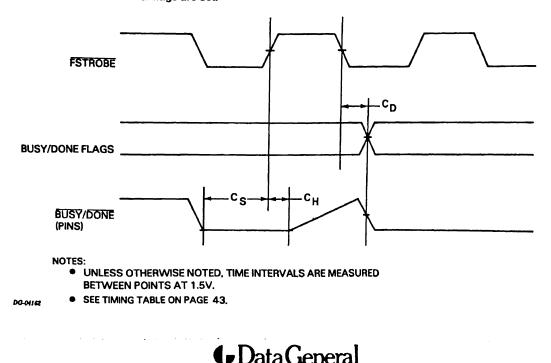

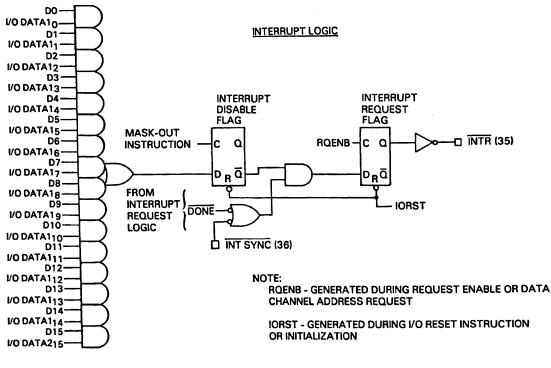

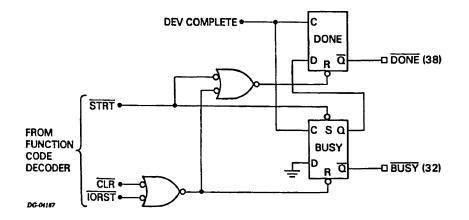

| 23 | Busy and Done Flags                             |

| 23 | Addressing Non-Existent Device Codes            |

| 26 | PROGRAM INTERRUPTS                              |

| 26 | 16-Level Priority Interrupts                    |

| 27 | CPU I/O INSTRUCTIONS                            |

| 32 | OPERATIONS PROTOCOL                             |

| 32 | MEMORY OPERATIONS                               |

| 32 | Address/Data Pins                               |

| 32 | Control                                         |

| 33 | BEAD                                            |

| 33 | WRITE                                           |

|    |                                                 |

34 READ-MODIFY-WRITE

.....

34 REFRESH

Data General Corporation, Westboro, Massachusetta 01581

. . . . . . .

. . . . .

i

- 35 I/O OPERATIONS

- 35 Programmed I/O

- 35 Data Channel Break

- 35 I/O Bus Transfers

- 36 Request Enable

- 37 Data Channel Address Request

- 37 Data

- 38 I/O Command

- **39** I/O Transfer Protocol

- **39** PROGRAMMED I/O DATA OUT

- 39 PROGRAMMED I/O DATA IN

- 40 DATA CHANNEL DATA OUT

- 40 DATA CHANNEL DATA IN

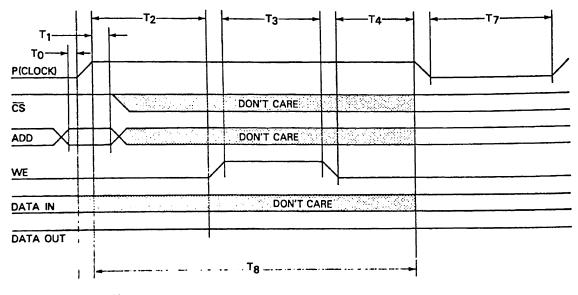

- 41 Timing

- 41 PROGRAMED I/O LATENCY

- 42 DATA CHANNEL LATENCY

- 43 STATUS

- 43 Initialization

- 43 Halt

- 43 Reset

- 44 INSTRUCTION EXECUTION TIMES (IN CPU CYCLES)

.....

water a serie of an example of the second second

### 45 ELECTRICAL SPECIFICATIONS

- 45 ABSOLUTE MAXIMUM RATINGS

- 45 RECOMMENDED OPERATING CONDITIONS

- 45 DC CHARACTERISTICS

- 47 AC CHARACTERISTICS

- 47 Switching Diagrams

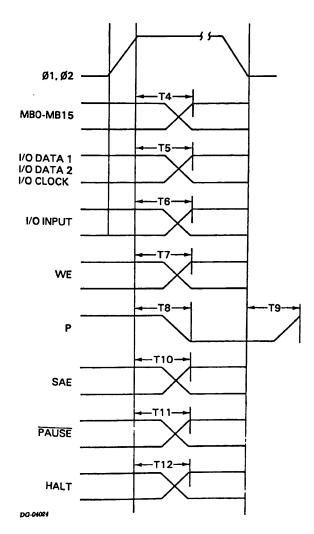

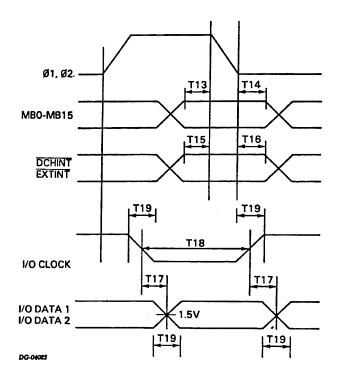

- 48 Transition Timing

- 49 TIMING TABLES

- 49 MEMORY READ/WRITE

- 49 I/O BUS

- 49 HALT

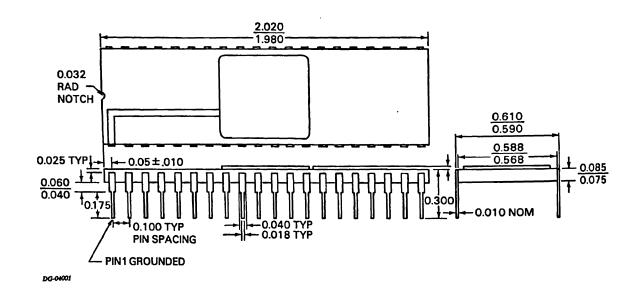

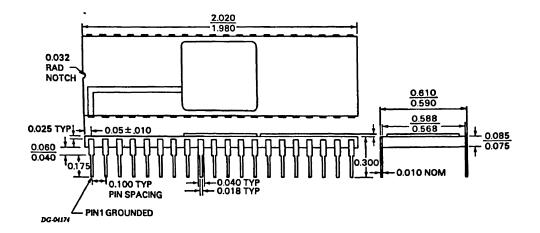

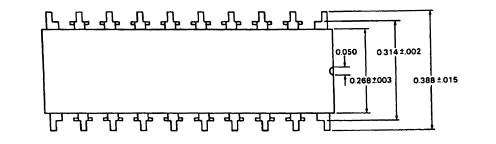

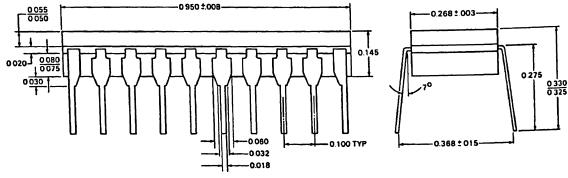

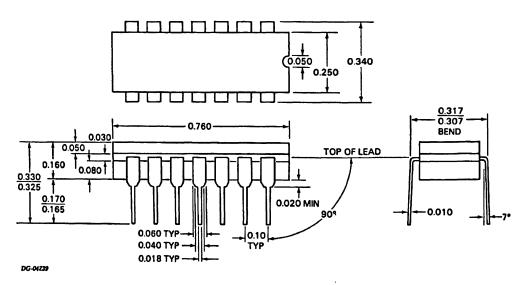

- 50 PACKAGE SPECIFICATIONS

This page intentionally left blank.

ŗ,ŕ

-----

. همی ۲۰۰۰ میکنونون ای مح

.....

. . . . . . .

# mN601 16-BIT MICROPROCESSOR

.

.

Data General Corporation, Westbury, Massachusetts 01581

## **16-BIT MICROPROCESSOR (CPU) NMOS INTEGRATED CIRCUIT**

#### FEATURES

- FULL NOVA 16-BIT ARCHITECTURE AND INSTRUCTION SET IN A SINGLE 40-PIN NMOS SILICON-GATE CHIP

- INTEGRAL DATA CHANNEL, REAL-TIME CLOCK, AND MULTIPLY/DIVIDE

- INTEGRAL HIDDEN REFRESH AND CONTROL LOGIC FOR DYNAMIC RAMs

- COMPREHENSIVE STACK ARCHITECTURE WITH HARDWARE STACK AND FRAME POINTER REGISTERS

- POWERFUL SAVE AND RETURN INSTRUCTIONS FOR SUBROUTINE CALLS

- MULTIPLE ACCUMULATORS

- SYSTEM MEMORY SUPPORT UP TO 32K WORDS OF RAM/PROM

- SINGLE WORD INSTRUCTION FORMAT IN A VARIETY OF ADDRESSING MODES - ABSOLUTE, RELATIVE, INDEXED, DEFERRED AND AUTO-INCREMENT/ DECREMENT

- SEPARATE MEMORY AND I/O BUSES

- I/O BUS PROVIDES FUNCTIONAL EQUIVALENT OF 47-LINE NOVA I/O BUS

- 16-LEVEL PROGRAMMED PRIORITY INTERRUPT

#### PACKAGE

DG-04026

### **GENERAL DESCRIPTION**

The mN601 is a full 16-bit NMOS microprocessor that provides the central processing function for Data General's microNOVA family. The mN601 features NOVA 16-bit architecture, including hardware multiply/divide; multiple addressing modes, including absolute, relative, indexed, deferred, and auto-increment/decrement; multiple accumulators, including two that can be used as index registers; hardware stack and frame pointers with stack overflow protection; programmed priority interrupt to 16 levels; and separate memory and I/O buses.

Data General's microNOVA family of integrated circuits also includes memories, peripheral controllers, and supporting circuits which can be used to develop a complete, high-performance, microcomputer system.

The mN601 is supported by the mN606 4K RAM, the mN603 I/O Controller (IOC), and system buffer elements. The 4096-bit mN606 uses cost- effective dynamic NMOS RAM technology to support microNOVA's large memory orientation. The mN603 IOC delivers the full functional capability of the 47-line NOVA I/O bus, including a parallel 16-bit I/O port. System buffer elements allow microNOVA support up to 32K words of memory and a full complement of peripherals.

7

mN601

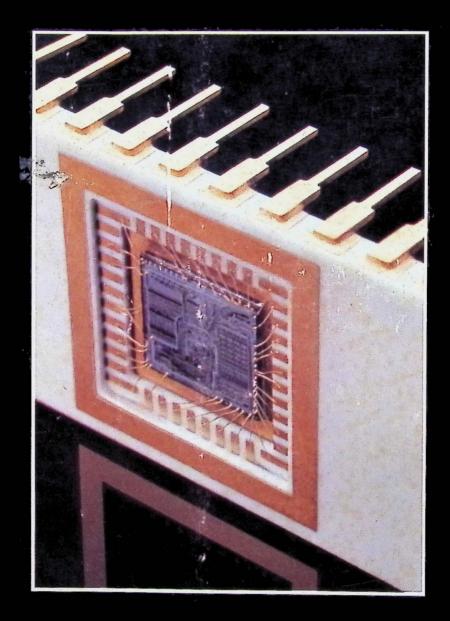

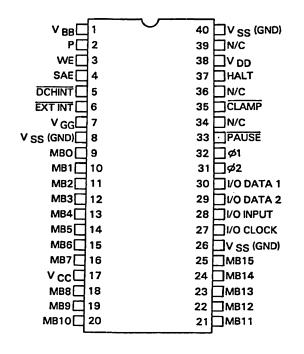

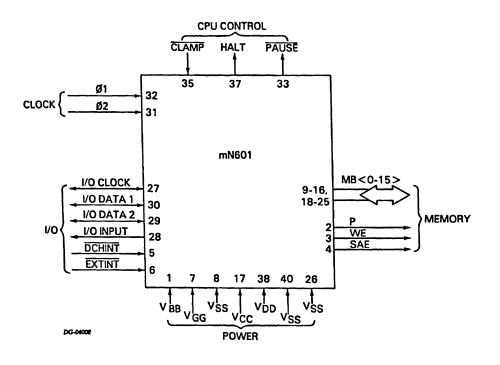

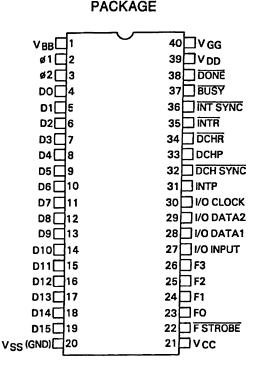

#### FUNCTIONAL PIN CONNECTION DIAGRAM

.....

The following table describes the function of each pln shown in the pin connection diagram.

### **PIN DESCRIPTIONS**

| MNEMONIC | PIN<br>NO.    | I/O      | FUNCTION                                                                                                                                                                                                                                                                                                      |

|----------|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |               |          | CLOCK                                                                                                                                                                                                                                                                                                         |

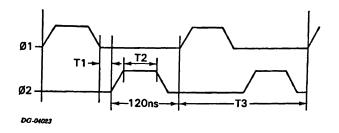

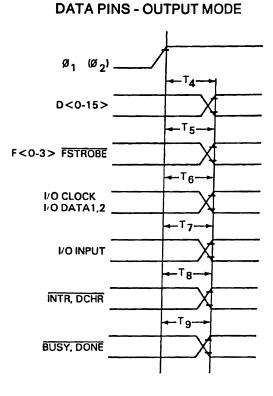

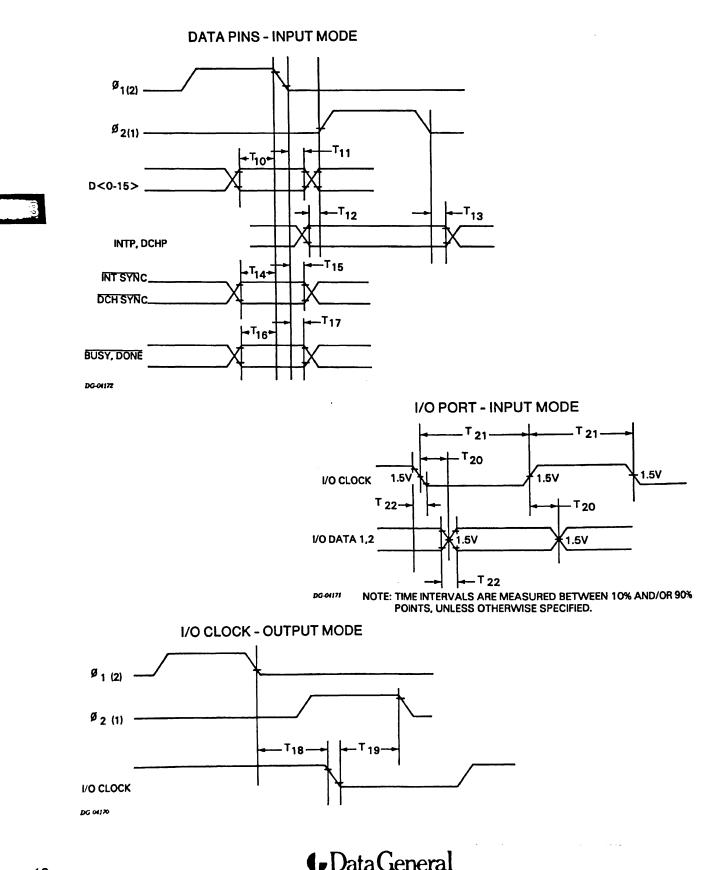

| φ1<br>φ2 | 32<br>31      | IN<br>IN | Two-phase system clock. Operates between 0 and 14V amplitude. Generates 4-phase internal clock, providing internal control timing.                                                                                                                                                                            |

|          |               |          | MEMORY BUS                                                                                                                                                                                                                                                                                                    |

| MB0-MB15 | 9-16<br>18-25 | 1/0      | Bi-directional, data and address bus. When used as a data bus, MBO contains the MSB (most significant bit) and MB15, the LSB (least significant bit). As an address bus, MB<1-15>contains the address and MBO defines the memory operation as either refresh or read/write.                                   |

|          |               |          | This bus is precharged internally by the CPU. It is held high by individual internal pull-up resistors tied to each line. During address or data transfers, each line transmitting a 0 is discharged; each line transmitting a 1 is undischarged. See the Memory Operations Section for detailed information. |

|          |               |          | MEMORY CONTROL                                                                                                                                                                                                                                                                                                |

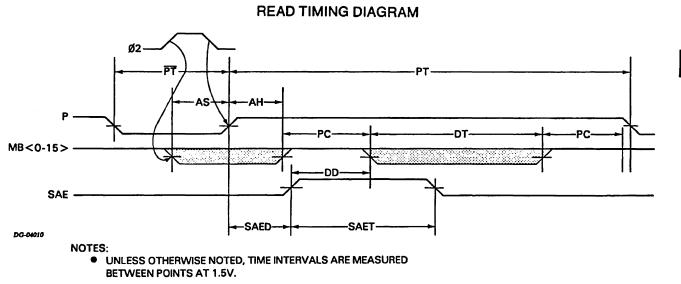

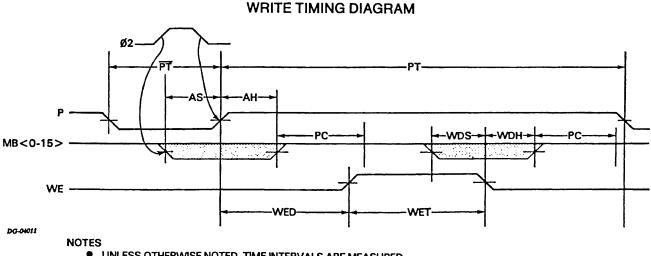

| Р        | 2             | Ουτ      | Active high. Initiates all memory cycles. When P goes high, indicates a valid address is on the memory bus.                                                                                                                                                                                                   |

| SAE      | 4             | ουτ      | Active high. Enables sense amplifier outputs on the memory bus during a read operation.                                                                                                                                                                                                                       |

| WE       | 3             | OUT      | Active high. Enables write operation. On the falling edge of WE, information on the memory bus is written into memory.                                                                                                                                                                                        |

Data General Corporation, Westbraro, Massachusetts 01581

I

mN601 PIN DESCRIPTIONS

. . .

.

. . . . .

. .

## **PIN DESCRIPTIONS (Cont.)**

| MNEMONIC                        | PIN<br>NO.                    | 1/0        | FUNCTION                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|---------------------------------|-------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                 |                               |            | I/O BUS                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| I/O DATA 1<br>I/O DATA 2        | 30<br>29                      | 1/0<br>1/0 | Two-line, bi-directional bus. All data and I/O command information is transmitted serially<br>between the mN601 and I/O devices at the MASTER CLOCK rate. During a 16-bit<br>transfer, I/O DATA1 carries the most significant 8 bits (0-7); I/O DATA2, the least<br>significant bits (8-15). |  |  |  |  |  |  |

| I/O INPUT                       | 28                            | Ουτ        | Indicates direction of I/O transfer. When low, indicates a transfer from the mN601; when high, a transfer to the mN601.                                                                                                                                                                      |  |  |  |  |  |  |

| I/O CLOCK                       | 27                            | 1/0        | Synchronizes all I/O transfers to and from the mN601. Holding I/O CLOCK low for $10\mu$ secs resets the microcomputer. I/O CLOCK should not be pulled low when I/O INPUT is in the low state.                                                                                                |  |  |  |  |  |  |

| EXTINT                          | 6                             | IN         | Active low. When asserted low by a device, initiates a program interrupt, providing CPU<br>Interrupts are enabled.                                                                                                                                                                           |  |  |  |  |  |  |

|                                 |                               |            | When the mN601 is in the HALT state (see below), it is started by generating a program interrupt.                                                                                                                                                                                            |  |  |  |  |  |  |

| DCHINT                          | 5                             | IN         | Active low. When asserted low by a device, the CPU will execute a data channel break.<br>The mN601 responds to data channel break requests while it is in the HALT state as<br>well as during operations.<br>CPU CONTROL                                                                     |  |  |  |  |  |  |

| HALT                            | 37                            | Ουτ        | Active high. When the CPU is halted (idling), as the result of either resetting the CPU by pulling I/O CLOCK low or the execution of a HALT instruction, HALT generates a sequence of .417MHz pulses.                                                                                        |  |  |  |  |  |  |

|                                 |                               |            | In the HALT state, the mN601 performs the following functions:<br>It generates Request Enable signals (see mN601 I/O Operations section) that<br>synchronize program interrupt and data channel requests.                                                                                    |  |  |  |  |  |  |

|                                 |                               |            | It responds to program interrupts and data channel requests. (The normal way to start<br>e mN601 is to generate a program interrupt.)                                                                                                                                                        |  |  |  |  |  |  |

|                                 |                               |            | <ul> <li>It generates dynamic RAM refresh signals to prevent the loss of information stored in<br/>RAM.</li> </ul>                                                                                                                                                                           |  |  |  |  |  |  |

| CLAMP                           | 35                            | IN         | Active low. When the mN601 is first powered up, $\overline{CLAMP}$ should be held low for a minimum of 100 $\mu$ sec. Then, when it goes high, the CPU is properly initialized and enters the HALT state.                                                                                    |  |  |  |  |  |  |

| PAUSE                           | 33                            | Ουτ        | Active low. PAUSE goes to the low level for a period of 240ns when the CPU is not using memory. During this period it is permissible to disable the $\phi 1$ and $\phi 2$ clocks, thus allowing multiporting of memory.                                                                      |  |  |  |  |  |  |

|                                 |                               |            | POWER                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| VBB<br>VCC<br>VDD<br>VGG<br>VSS | 1<br>17<br>38<br>7<br>8,26,40 |            | $-4.25V \pm .5V$<br>+ 5V ± .25V<br>+ 10V ± 1V<br>+ 14V ± 1V<br>Ground                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                                 | 34<br>36<br>39                |            | Reserved for future use<br>Reserved for future use<br>Reserved for future use                                                                                                                                                                                                                |  |  |  |  |  |  |

2

### ARCHITECTURE

The mN601 is a 16-bit parallel word central processing unit which executes the full NOVA line minicomputer instruction set, including an extended instruction set for stack and trap routines.

The instruction set addresses 32,768 words (65,536 bytes) of memory. Each memory address is 15-bits long. Each word is 16-bits long, consisting of two 8-bit bytes. Both words and bytes can be used as operands.

| 111                                                                                                             |  |

|-----------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                 |  |

| in the second |  |

|                                                                                                                 |  |

| Wo              | rd                      |

|-----------------|-------------------------|

| Byte            | Byte                    |

|                 | 011234567               |

| 01234567<br>MSB | 8 9 101112131415<br>LSB |

One word containing two bytes

The mN601 communicates with memory via a bi-directional, 16-bit parallel address and data bus. Three control lines direct the four memory operations: read, write, read-modify-write and refresh.

The mN601 communicates with I/O controller interfaces via two, bi-directional, serial lines that carry data and I/O commands. One control line indicates the direction of transfer, to or from the CPU, and a clock line synchronizes the transfer of information. Two interrupt lines, programmed I/O and data channel, allow I/O interfaces to request processor time.

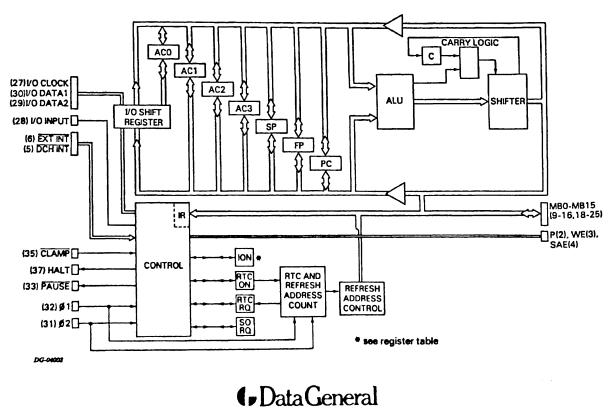

The Expanded Block Diagram shows the internal architecture of the mN601, together with the memory bus, the I/O bus, and their respective control lines.

#### EXPANDED BLOCK DIAGRAM

Data General Corporation, Westbury, Massachusetts 01581

Within the mN601, information is stored in the thirteen registers listed below.

| REGISTERS                                                                                                                                                                                                                                                                                                                         | USER<br>ACCESSIBLE                                                            | SIZE                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| accumulator 0<br>accumulator 1<br>accumulator 1<br>accumulator 2<br>accumulator 3<br>program counter<br>stack pointer<br>frame pointer<br>carry bit<br>interrupt enable bit (ION)<br>real-time-clock enable bit (RTC ON)<br>real-time-clock request bit (RTC RQ)<br>stack overflow request bit (SO RQ)<br>refresh address counter | yes<br>yes<br>yes<br>yes<br>yes<br>yes<br>yes<br>yes<br>yes<br>no<br>no<br>no | 16 bits<br>16 bits<br>16 bits<br>15 bits<br>15 bits<br>15 bits<br>15 bits<br>1 bit<br>1 bit<br>1 bit<br>1 bit<br>1 bit<br>1 bit<br>6 bits |

- The four accumulators provide scratchpad memory, or work space, during program execution.

- The program counter contains a 15-bit memory address that is used by the processor when fetching the next instruction from memory during program execution. When the instruction is completed, the program counter is either automatically incremented by one or is modified by the program, before the next instruction is fetched.

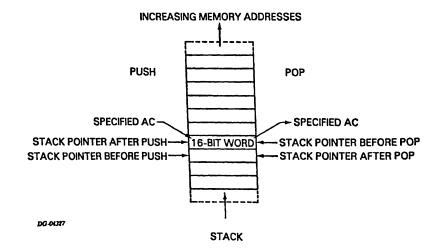

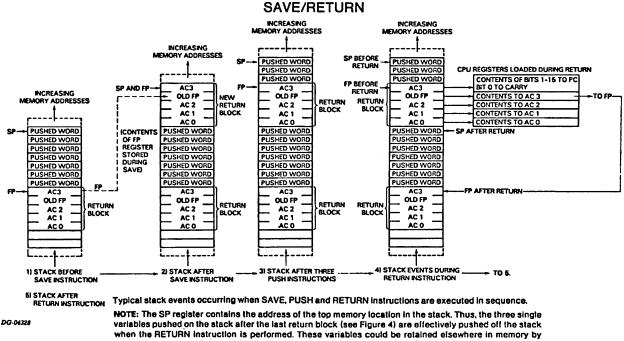

- The stack pointer contains the memory address of the highest location in memory used by the stack. As information is pushed onto the stack, this address is appropriately incremented; as information is popped off the stack, the address is decremented.

- The frame pointer contains the memory address of a location within the stack. When a RETURN instruction is executed, this address is used as a reference for retrieving information from the stack.

- The carry bit reflects the results of certain arithmetic computations performed by the arithmetic logic unit (ALU), e.g., addition overflow.

- The interrupt enable bit can be controlled by the program. When enabled (set to 1), the processor responds to program interrupt requests.

- The real-time-clock enable bit is set by the program. When enabled (set to 1), the real-time clock contained in the processor generates an interrupt at 1.8432ms intervals.

- The real-time-clock request bit generates a program interrupt at fixed intervals of 1.8432ms when both the real-time clock and interrupts are enabled.

- The stack overflow request bit generates a program interrupt when the stack overflows a 256-word memory address boundary, e.g., 377<sub>8</sub> to 400<sub>8</sub>.

- The refresh address counter generates a 6-bit address specifying 64 numbers used to address 1/64 of all the available memory to be refreshed. All 32,768 RAM memory locations are refreshed at least once every 1.8432ms.

# mN601 INSTRUCTION SET

### **INSTRUCTION SET**

المراجعة فتصفيتها فتنتز فارتقا بط

-----

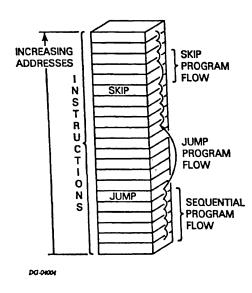

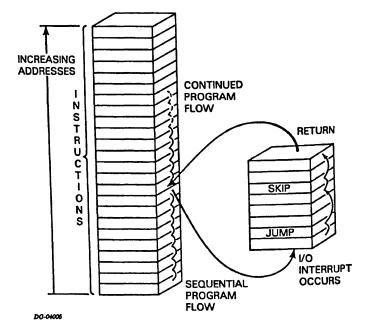

Each mN601 (microNOVA) instruction is contained in one 16-bit word. Programs for the mN601 consist of sequences of instructions which are stored in external memory. The order in which these instructions are executed depends on the 15-bit memory address in the program counter register. During program execution, the processor sends this address to memory and fetches the contents of the specified memory location, via its memory address/data pins. During the execution of an instruction, information is moved between the processor's internal registers, memory or I/O data pins. When the instruction is completed, the program counter is updated. The CPU uses the contents of the program counter to address the next location.

Sequential operation can be altered by a jump or conditional skip instruction or by an interrupt. Jump instructions load a new address in the program counter; conditional skip instructions increment the program counter address by two if a specified test is true. In both cases, sequential operation is resumed from the updated address in the program counter. When the program is interrupted (e.g., I/O external interrupts, real-time clock interrupts, fault conditions of various kinds), the interrupt facility stores the next sequential program address in a specified location in memory so that the interrupt handler can return control to the interrupted program at the proper entry point. Then, the program counter is loaded with the memory address of the interrupt handler program and sequential operation resumes.

### mN601 MEMORY REFERENCE INSTRUCTIONS

The microNOVA (mN601) instruction set can be divided into five groups of operations:

- Memory reference

- Fixed point arithmetic and logical operations

- Stack manipulation

- I/O functions

- CPU I/O functions

Each instruction is formatted in a 16-bit (one word) field. In the instruction descriptions that follow, the mnemonics are those recognized by Data General's Assembler. See the microNOVA Programmer's Reference (DGC No. 015-000050) for detailed programming information, including the use of instruction set options, such as conditional skips and flag commands.

**NOTE:** When the instructions described below are executed, the mN601 pins follow the protocol specified by the instructions. It is assumed that the mN601 is interfaced with mN603 I/O controllers and some amount of memory.

#### **MEMORY REFERENCE INSTRUCTIONS**

This instruction group moves data between accumulators and memory, modifies the contents of memory, and alters the program flow.

Locations in memory are sequentially numbered from 00000 through 777778, so that each memory address is 15 bits long.

#### **Addressing Modes**

Memory reference instructions provide a variety of addressing modes for accessing 32,768 memory loctions: absolute, PC relative, and indexed (via accumulator 2 or 3). In addition, the processor supports eight levels of conventional indirect (deferred) addressing and five levels of indirect addressing through auto-incrementing/decrementing locations.

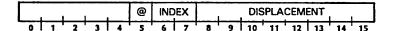

When instructions that reference memory are executed, the processor calculates an effective 15-bit address using bits 5 through 15 of the memory reference instruction field shown below.

#### MEMORY REFERENCE INSTRUCTION FORMAT

Bit 5 = Indirect bit; Bits 6 and 7 = Address mode: 00 = Absolute

01 = PC relative 10 = AC2 indexed 11 = AC3 indexed

In all but the absolute mode, the displacement is a signed number within the range -128 through +127. Signed numbers utilize the two's complement representation for negatives.

. . . . . . .

. . .

#### EFFECTIVE ADDRESS CALCULATION

| Absolute    | Displacement is an unsigned number within the range 00000-003778 that addresses one of the first 256 locations in memory, referred to as Page Zero. If the indirect bit is 0, the displacement is the effective address; if it is 1, the displacement is an indirect address (see the description of indirect addressing below). |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC relative | Displacement is a signed number that is added to the contents of the program counter. If the indirect bit is 0, the results of the addition are the effective address; if it is 1, the results are an indirect address.                                                                                                          |

| AC2 indexed | Displacement is a signed number that is added to the contents of accumulator 2. If the indirect bit is 0, the results of the addition are the effective address; if it is 1, the results are an indirect address.                                                                                                                |

| AC3 indexed | Displacement is a signed number that is added to the contents of accumulator 3. If the indirect bit is 0, the results of the addition are the effective address; if it is 1, the results are an indirect address.                                                                                                                |

NOTE: A memory address is always 15 bits long. When the results of an addition overflow 15 bits, the overflow is ignored.

Example: Program Counter =  $77774_8$ Displacement =  $\pm 012_8$

Result = 000006 8; not 100006 8

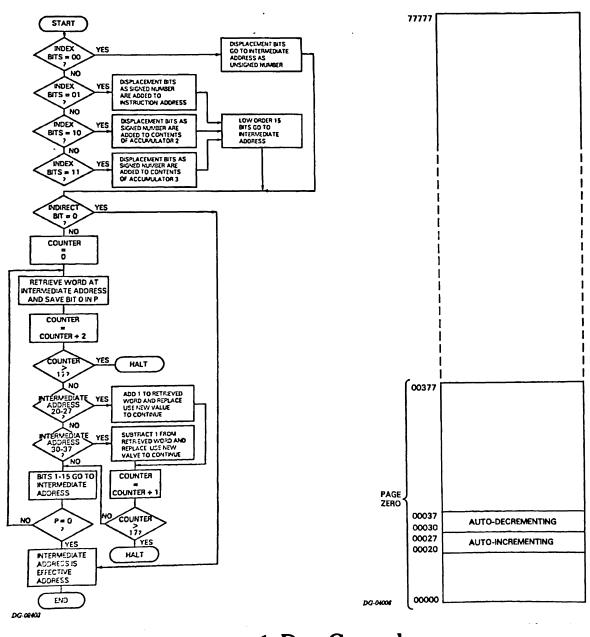

#### Indirect Addressing

When the indirect bit (bit 5) contains a 1, the calculated address is an intermediate (indirect) address that points to an effective address stored in memory. In this case, the processor fetches the contents of the calculated address and tests bit 0 (indirect sign bit when stored in memory). If it is 0, bits 1 through 15 of the contents of the indirect address are used as the effective address; if it is 1, bits 1 through 15 are used as an indirect address. In the latter case, the indirection chain continues until the processor either fetches a word in which bit 0 equals 0 (in this case, the processor has the effective address) or has executed eight levels of indirection (or five levels if the indirection chain accesses auto-incrementing/decrementing locations, explained below).

An internal counter is used to control the number of indirect addresses through which the processor searches for an effective address. This counter is initialized when the indirect bit is set to 1. Each time a word in the indirection chain is retrieved from memory the counter is incremented by two (or by three if an auto-increment or decrement location is indirectly addressed). If the counter becomes greater than 17 before an effective address is retrieved, the processor halts.

Corporation, Westboro, Massechusetta 01581

### mN601 MEMORY REFERENCE INSTRUCTIONS

#### Auto-Incrementing/Decrementing

Memory locations with addresses within the range  $020_8$  through  $027_8$  are called auto-incrementing locations. When one of these locations is indirectly addressed, the processor automatically increments bits 0 through 15 of the contents of the indirect address before using these bits as either an effective or indirect address. The updated contents are written back into the auto-incrementing location.

Memory locations with addresses within the range 030  $_8$  through 037  $_8$  are called auto-decrementing locations. When one of these locations is indirectly addressed, the processor automatically decrements bits 0 through 15 of the contents of the indirect address before using these bits as either an effective or indirect address. The updated contents are written back into the auto-decrementing location.

**NOTE 1:** When referencing auto-increment/decrement locations, the state of bit 0 before the increment or decrement is the condition upon which the continuation of the indirection chain is based. For example: if an auto-increment location contains 17777<sub>8</sub> and the location is referenced as part of an indirection chain, location 0 will be the next indirect address in the chain; not the effective address.

NOTE 2: When a non-existing memory address is specified in a memory reference instruction, the contents will appear as all ones.

. . . . .

| MODE        | INDEX<br>BITS | MEMORY ADDRESSING<br>CAPABILITY (OCTAL) |  |  |  |  |

|-------------|---------------|-----------------------------------------|--|--|--|--|

| Absolute    | 00            | 00000-00377                             |  |  |  |  |

| PC Relative | 01            | 00000-77777                             |  |  |  |  |

| AC2 Indexed | 10            | 00000-77777                             |  |  |  |  |

| AC3 Indexed | 11            | 00000-77777                             |  |  |  |  |

#### MEMORY ADDRESSING

and a second second

MEMORY

### ADDRESS CALCULATION

Jata General

Data General Corporation, Westboro, Massachusetts 01581

### 2

#### **No Accumulator-Effective Address Instructions**

| 0 | ) | 0 | 0 | OP C | P CODE @ |   | INE | NDEX |   | DISPLACEMENT |    |    |    | ,  |    |    |

|---|---|---|---|------|----------|---|-----|------|---|--------------|----|----|----|----|----|----|

| 0 |   | 1 | 2 | 3    | 4        | 5 | 6   | 7    | 8 | 9            | 10 | 11 | 12 | 13 | 14 | 15 |

NOTE: The letter E in the function descriptions below denotes effective address; AC denotes accumulator.

| MNEMONIC | MEANING                          | FUNCTION                                                                                                                                                                           | INSTRUCTION FORMAT                                                      |

|----------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| JMP      | Jump                             | Compute (E) and load E into PC.                                                                                                                                                    | 0 0 0 0 @ INDEX DISPLACEMENT<br>0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15   |

| JSR      | Jump To<br>Subroutine            | Compute E. Store contents<br>of PC+1 in bits 1-15 of AC3<br>and set bit 0 to 0; then, load<br>E into PC.                                                                           | 0 0 0 1 @ INDEX DISPLACEMENT<br>0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15   |

| ISZ      | Increment<br>And Skip<br>If Zero | Compute E. Increment<br>contents of location E and<br>write results back into<br>location E. If results equal<br>000000, increment PC by<br>two; otherwise increment<br>PC by one. | 0 0 1 0 @ INDEX DISPLACEMENT<br>0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15   |

| DSZ      | Decrement<br>And Skip<br>If Zero | Compute E. Decrement<br>contents of location E and<br>write results back into<br>location E. If results equal<br>000000, increment PC by<br>two; otherwise increment<br>PC by one. | 0 0 0 1 1 @ INDEX DISPLACEMENT<br>0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

#### **One Accumulator-Effective Address Instructions**

. . . . . . . .

| AC  | Bits 3 | 4 |

|-----|--------|---|

| ACO | 0      | 0 |

| AC1 | 0      | 1 |

| AC2 | 1      | 0 |

| AC3 | 1      | 1 |

| MNEMONIC | MEANING              | FUNCTION                                                        | INSTRUCTION FORMAT                                                     |  |  |  |  |

|----------|----------------------|-----------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|

| LDA      | Load<br>Accumulator  | Compute E. Load specified<br>AC with contents of location<br>E. | 0 0 1 AC @ INDEX DISPLACEMENT<br>0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |  |  |  |  |

| STA      | Store<br>Accumulator | Compute E. Store contents<br>of specified AC in location<br>E.  | 0 1 0 AC @ INDEX DISPLACEMENT<br>0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |  |  |  |  |

Data General Data General Corporation, Westboro, Massachusetts 01581

**..** .. .**.** .. ..

### **TRAP INSTRUCTION**

-----

This instruction can be used as a single word call to subroutines containing extended instructions not implemented by the mN601. The format of the TRAP instruction is shown below.

. .....

| MNEMONIC | MEANING | FUNCTION                                                                                                                                                                                                                                            | INSTRUCTION FORMAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRAP     | Тгар    | The address of this instruction is placed in memory location $46_8$ and bit 0 of that location is set to 0. Then, the processor performs a jump indirect through memory location $47_8$ The contents of ACS and ACD do not affect this instruction. | 1         ACS         ACD         TRAP NUMBER         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 |

.

#### **ARITHMETIC/LOGICAL INSTRUCTIONS**

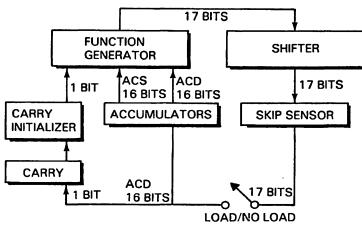

This instruction group performs arithmetic and logical operations on the contents of one or two accumulators. In some cases, it changes the value of the carry bit and, if specified, manipulates and/or tests the results of the operations.

The logical organization of the mN601's internal arithmetic logic unit (ALU) is shown below.

DG-00927

#### **TWO ACCUMULATOR-MULTIPLE OPERATION**

| 1 | A | S | A | D | OF | CO | DE | S | Η | (  | <u></u> | #  |    | SKIP |    |

|---|---|---|---|---|----|----|----|---|---|----|---------|----|----|------|----|

| 0 | 1 | 2 | 3 | 4 | 5  | 6  | 7  | 8 | 9 | 10 | 11      | 12 | 13 | 14   | 15 |

| AC – accumulator              | ACS ACD<br>Bits 1 2 3 4 |

|-------------------------------|-------------------------|

| ACS = source accumulator      | AC0 0 0 0 0             |

| ACD - destination accumulator | AC1 0 1 0 1             |

|                               | AC2 1 0 1 0             |

|                               | AC3 1 1 1 1             |

Each instruction specifies two accumulators, source and destination, that supply the function generator with operands. The function generator performs the operation specified by the operation code, e.g., add, subtract, and produces a carry bit whose value depends on three quantities: an initial value specified by the instruction, the inputs, and the function performed. The initial value can be derived either from the previous value of the carry bit or a new value specified by the instruction.

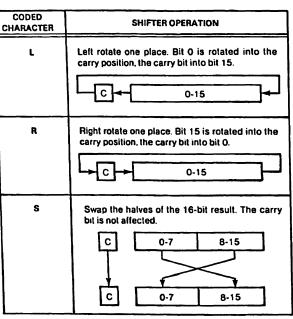

The 17-bit (16 bits plus the carry bit) result of the function generator goes to the shifter. Depending upon the shift operation specified, the results are either passed undisturbed through the shifter or they are manipulated in one of the following ways; the 17-bit result is rotated one bit position, either left or right; or, the two 8-bit halves are swapped without affecting the carry bit.

# mN601 ARITHMETIC/LOGICAL INSTRUCTIONS

وبورا يترو بتبتيها المار المبتد بالالالا مالو بمنتد

DG-04123

The 17-bit output of the shifter can be tested for a conditional skip. The skip sensor tests either, or both, the carry bit or the 16-bit result of the shifter, depending upon the instruction, to determine if either, or both, is equal or not equal to zero.

After the skip sensor has tested the output of the shifter, the 17- bit result of the shifter is either loaded or not loaded, depending upon the instruction, into the destination accumulator and the carry bit.

| CLASS<br>ABBREV. | CODED<br>CHARACTER | RESULT | OPERATION                                                                                   |

|------------------|--------------------|--------|---------------------------------------------------------------------------------------------|

| C                | (option omitted)   | 00     | Do not initialize the carry bit                                                             |

| I                | z                  | 01     | initialize the carry bit to 0                                                               |

|                  | o                  | 10     | Initialize the carry bit to 1                                                               |

|                  | с                  | 11     | Initialize the carry bit to the complement of its<br>present value                          |

| SH               | (option omitted)   | ∞      | Leave the result of the anthmetic or logical<br>operation unalfected                        |

|                  | L                  | 01     | Combine the carry and the 16-bit result into a 17-bit number and rotate it one bit left     |

|                  | R                  | 10     | Combine the carry and the 16-bit result into a<br>17-bit number and rotate it one bit right |

|                  | s                  | 11     | Exchange the two 8-bit halves of the 16-bit result without affecting the carry              |

| #                | (option privited   | » o    | Load the result of the shift operation into ACD                                             |

|                  | #                  | 1      | Do not load the result of the shift operation int<br>ACD                                    |

| CLASS<br>ABBREV. | CODED<br>CHARACTER | RESULT<br>BITS | OPERATION                          |

|------------------|--------------------|----------------|------------------------------------|