# **KEYBOARD PRINTER I/O CONTROLLER MAINTENANCE MANUAL**

Consists of:

Installation Specification Maintenance Specification Schematic 02-123R01A20 02-123R02A2-1 02-123R05D08

C INTERDATA INC., 1969 All Rights Reserved

Printed in U.S.A. March , 1972

#### 1. GENERAL

The Keyboard Printer I/O Controller is a one mother-board interface which adapts the Selector Channel or Multiplexor Channel Bus to either the General Electric Terminet 300 Terminal, the Model 37 Teletype, or the 33/35 Teletype in the Full-Duplex Mode. It is also capable of adapting either the Terminet or Model 37 via a 103A Data Set, or equivalent Data Set, to the Selector Channel or Multiplexor Channel Bus.

2. TERMINET 300 AND MODEL 37 CONNECTIONS

The Controller may be installed in any I/O slot of a main or expansion file. Remove RACK0/TACK0 strap between back panel Terminals 114-0 and 214-0 at the location of controller.

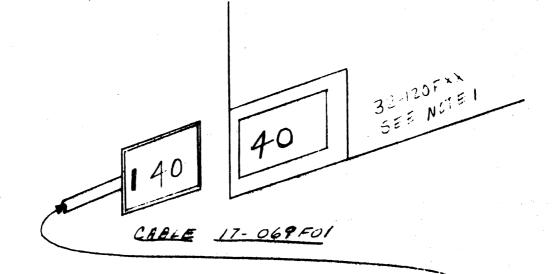

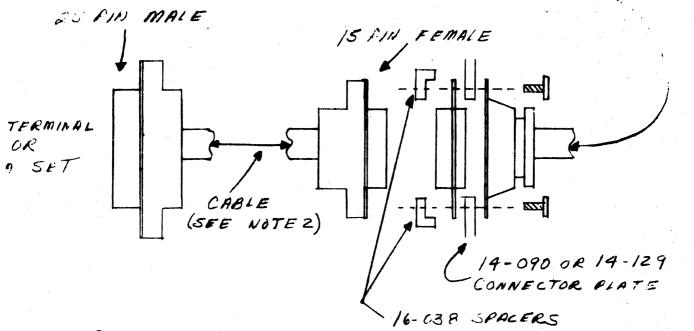

Install 17-069F01 cable between location 40 of Controller and the connector plate (14-090 or 14-127) at the rear of the cabinet. (See Figure 1.) Install 17-082F01 cable between connector and the device (Terminet 300 or Model 37 TTY).

3. 103A DATA SET CONNECTION

Repeat Step 2, except use a 17-050 cable between connector plate and Data Set (see Figure 1).

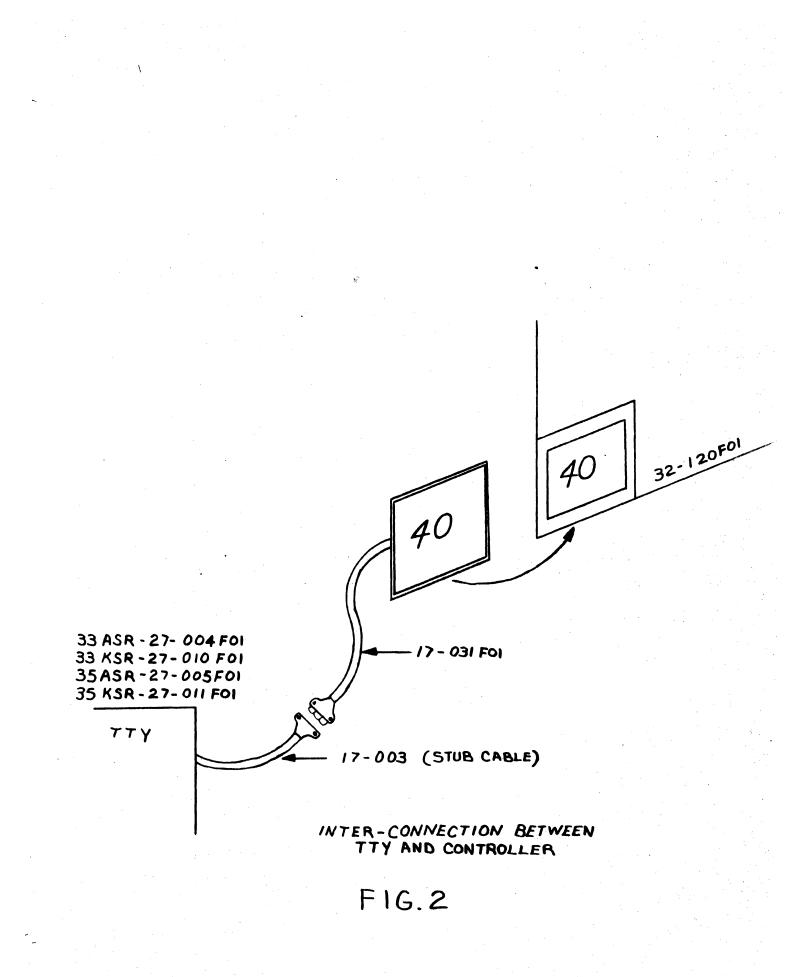

4. 33/35 TELETYPE INSTALLATION (See Figure 2)

The Controller may be installed in any I/O slot of a main or expansion file. Remove RACK0/TACK0 strap between back panel Terminals 114-0 and 214-0 at location of Controller. Install 17-031 cable as shown in Figure 2.

Load and run Test Program 06-083M14 or 06-004M14.

| NAME        | TITLE                                                                                                                                                                                                                               | DATE     | TITLE                  |          |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------|----------|--|

| R. E. Sager | ENGR                                                                                                                                                                                                                                | 11-17-69 | ] INSTALLATION SPECIFI | ICATION  |  |

| D. YOUNG    | SYS TEST                                                                                                                                                                                                                            | 12-4-69  | INPUT TERMINAL CONT    | ROLLER   |  |

| R, E. JONES | MGR                                                                                                                                                                                                                                 | 11-18-69 |                        |          |  |

| C. BOLTON   | PROD,                                                                                                                                                                                                                               | 12-8-69  | I NO. I                | SHEET OF |  |

|             | n en de la desta de la section de la desta de la de<br>La desta de la d | I        | DWG. 02-123R01A20      | 1-3      |  |

EI 32-120FO2 - MODEL 37 TELETYPE 32-120 FO3 - GENERAL ELECTRIC TERMINET 300

CABLE SELECTION DIRECT CONNECTION TO TERMINAL USE 17-082FOI CONNECTION TO DATA SET USE 17-050FOI

CONTROLLER CONNECTIONS FIGURE 1

## **KEYBOARD PRINTER I/O CONTROLLER MAINTENANCE SPECIFICATION**

#### TABLE OF CONTENTS

| 1. | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                     | . 1                                       |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 2. | SCOPE                                                                                                                                                                                                                                                                                                                                                                                                                            | . 1                                       |

| 3. | BLOCK DIAGRAM ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                           | . 1                                       |

| 4. | FUNCTIONAL DESCRIPTION ANALYSIS.                                                                                                                                                                                                                                                                                                                                                                                                 | . 2                                       |

|    | <ul> <li>4.1 Status and Commands</li> <li>4.2 Initialization</li> <li>4.3 Multiplexor Bus Communication</li> <li>4.4 Interrupt Circuit</li> <li>4.5 Write Mode</li> <li>4.6 Read Mode</li> <li>4.6 Read Mode</li> <li>4.7 Timing Circuits</li> <li>4.8 Command, Status, and Data Request Circuits</li> <li>4.9 Coupler Circuits</li> <li>4.10 Line Break, Block, and Unblock Circuits</li> <li>4.11 Optional Features</li> </ul> | 2<br>2<br>2<br>5<br>5<br>5<br>5<br>6<br>6 |

| 5. | TIMING DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                         |

| 6. | MAINTENANCE                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                         |

| 7. | MNEMONICS                                                                                                                                                                                                                                                                                                                                                                                                                        | 8                                         |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |

#### ILLUSTRATIONS

| Figure 1. | Serial ASCII Code U (Even Parity) Ten and Eleven-Bit Code 1 |

|-----------|-------------------------------------------------------------|

| Figure 2. | Read to Write Timing                                        |

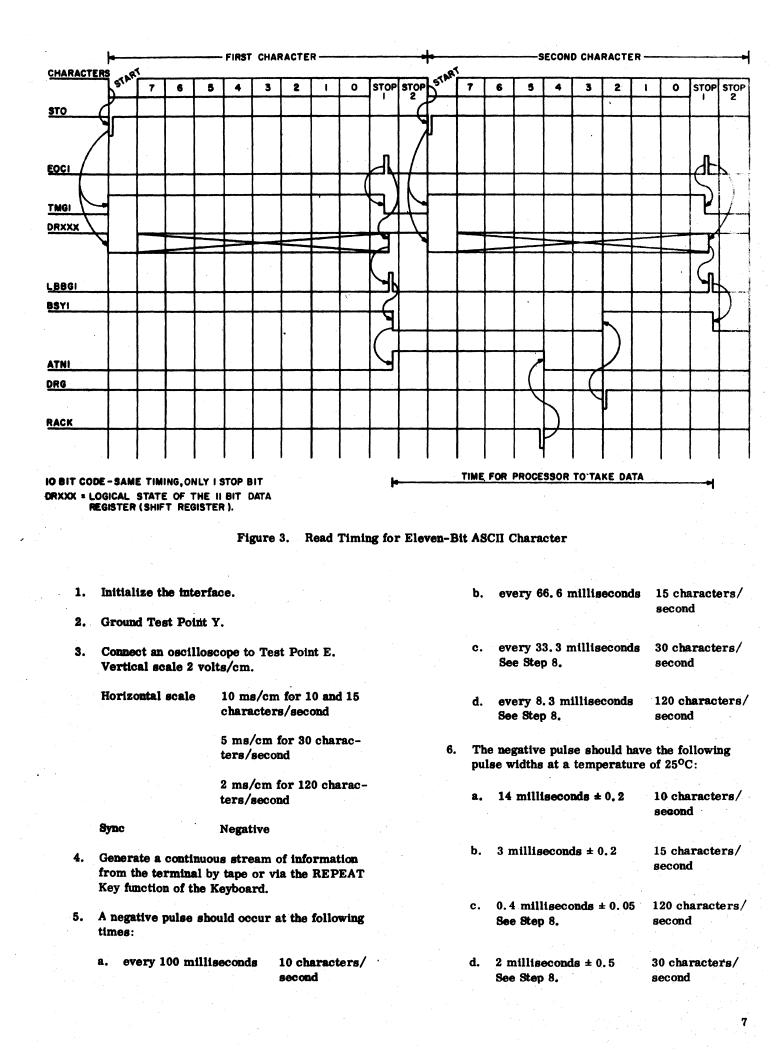

| Figure 3. | Read Timing for Eleven-Bit ASCII Character                  |

| Figure 4. | Character Timer Adjustment                                  |

### **KEYBOARD PRINTER I/O CONTROLLER MAINTENANCE SPECIFICATION**

#### 1. INTRODUCTION

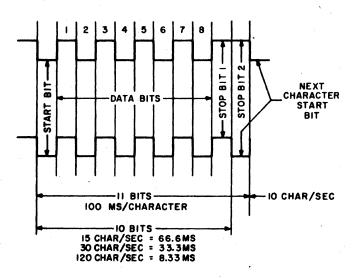

The Keyboard Printer I/O Controller is used to adapt various keyboard printer terminals to an INTERDATA Digital System. It converts serial eight level ASCII code (see Figure 1) to parallel form for processing by the computer.

Figure 1. Serial ASCII Code U (Even Parity) Ten and Eleven-Bit Code

The following list gives several terminals which the Keyboard Printer I/O Controller will adapt to an INTERDATA Digital System.

| 1. | 33 ASR/KSR Teletype              | 10 characters/second |

|----|----------------------------------|----------------------|

| 2. | 35 ASR/KSR Teletype              | 10 characters/second |

| 3. | Model 37 Teletype                | 15 characters/second |

| 4. | General Electric<br>Terminet 300 | 30 characters/second |

Other equivalent type terminals, which operate with the eight level ASCII code, could also be adapted to an INTERDATA Digital System by the K P I/O Controller. All terminals must be equipped for full-duplex operation. In addition to adapting the terminals directly to the computer, the K P I/O Controller can also support the terminals via a 103A Data Set. That is, a terminal may be separated from the Controller by 103A Data Sets. Other optional features are:

- 1. Programmable speed control for Terminet 300 at 30 and 120 characters/second.

- 2. Hardware option to convert the Controller to operate with one Start bit, seven Data bits, and one Stop bit.

#### 2. SCOPE

This Maintenance Specification is provided to describe the Keyboard Printer I/O Controller in sufficient detail to allow a digital technician to troubleshoot and maintain the interface. The following manuals will assist in understanding and maintaining the system as a whole.

29-193 INTERDATA K P I/O Operation and Programming Manual

> Vendor operating and service manuals for the particular terminal being used

#### 3. BLOCK DIAGRAM ANALYSIS

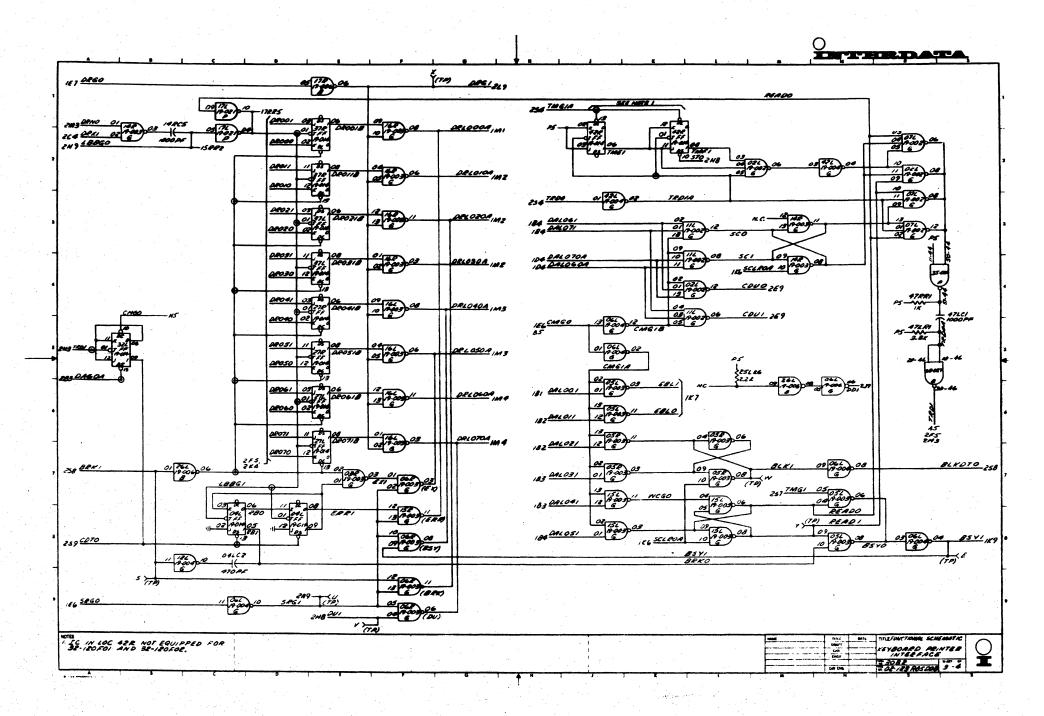

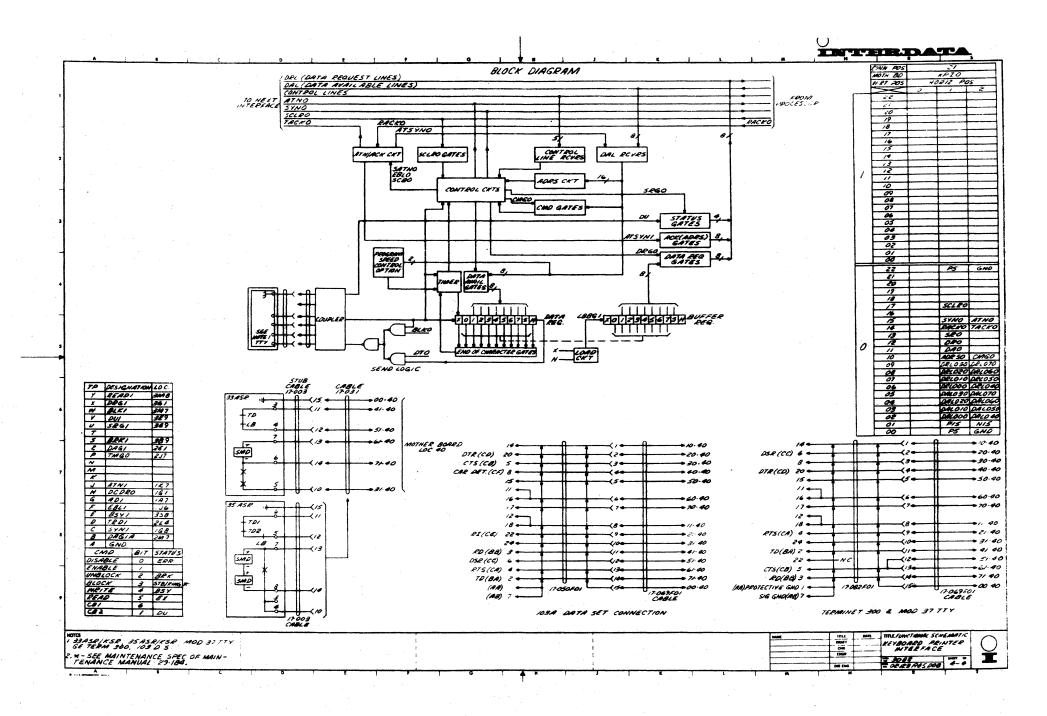

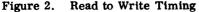

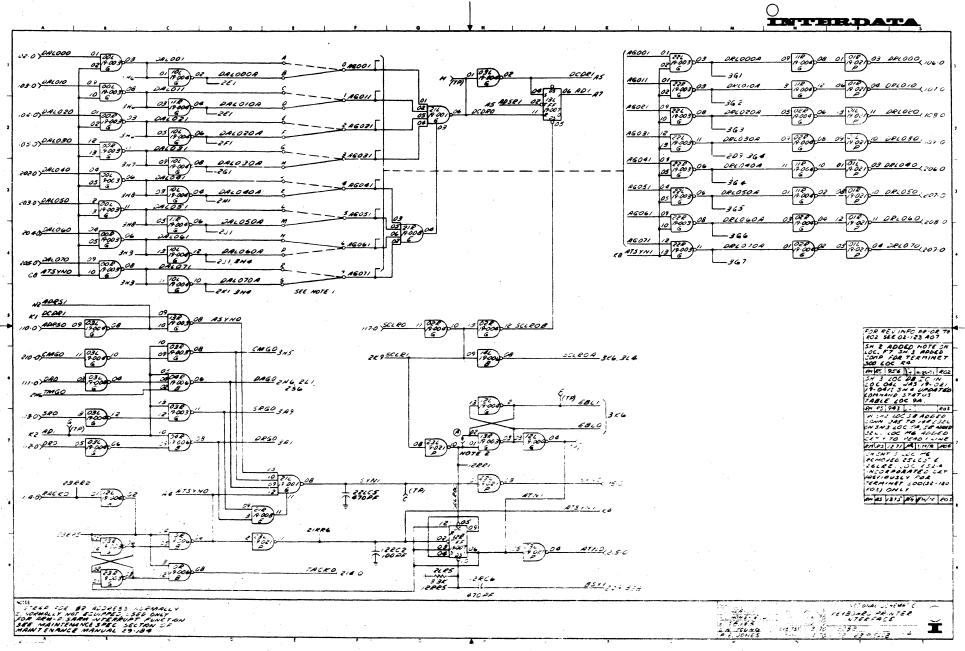

The block diagram of the K P I/O Controller is shown on Sheet 4 of the Functional Schematic 02-123D08.

The circuitry for addressing, interrupt, and DRL line drivers is configured in the same manner as that of the Standard I/O Board. Refer to <u>System Interface Manual</u>, Publication Number 29-003. The DAL RCVRS, Control Line RCVR, SCLR0 gates, ADRS CKT, ACK gates, and the ATN/ACK CKT make up the standard I/O portion of the Controller.

The control circuits consist of Command flip-flops (Read or Write, etc.), circuits to direct the flow of information (Terminal to Processor or Processor to Terminal), and circuits to control the timer when transmitting to or receiving from the terminal.

On receiving from the terminal, the serial information is sampled by the timer and placed in a Data Register (shift register). When the end of character is detected, the information is placed in a byte Buffer Register from which the Processor takes the parallel data. The byte buffer allows the Processor one character time to accept the data.

1

ransmitting to the terminal, the information is placed ectly into the Data Register (shift register) and then t scrially to the terminal under the control of the timer.

#### NOTE

On receiving, the data is taken from bit 0 to 7 of the Data Register; and on transmitting, the data is inserted into bit 1 to 8 of the Data Register.

coupler adapts the Controller to the terminal, i.e. either INTERDATA teletype levels, or to the RS 232 nterface levels.

$\odot$  Status gates place the status of the Controller on the 'X-CH Bus to the Processor. The Data Request gates ce the data on the MPX-CH Bus to the Processor.

tional speed control is available. The two speeds for Terminet 300 are 30 and 120 characters per second. her speeds can be made available by changing the Charer Timer. A four to one speed change can be made her program control.

#### FUNCTIONAL DESCRIPTION ANALYSIS

e functional description of the K P I/O Controller is sed upon the Functional Schematic, 02-123D08.

#### 4.1 Status and Commands

e definitions for the Status and Command bytes for the P I/O Interface are shown in Table 1. Since the interie is both an input and output device, the direction in ich the data is being handled is determined by the Read Write Mode. In the Read Mode, the interface is conioned to receive information from the terminal and ansfer it to the Processor. For transferring informan from the Processor to the terminal, the Write Mode required.

4.2 Initialization

hen the INITIALIZE pushbutton on the Processor is deessed, SCLR0 is applied to the interface to clear any nding interrupt, condition the interface for the Read, ock Mode, and Disable/Disarm the interrupt circuit.

4.3 Multiplexor Bus Communication

ommunication between the Processor and the interface via the standard I/O portion of the Controller, 02-123 )8, Sheet 1. See <u>System Interface Manual</u>, Publication umber 29-003, for a description of the standard I/O eration. 4.4 Interrupt Circuit

The interrupt circuit is normally set up to allow queuing of interrupts in the Device Disable Mode. A hardware option (ARM, DISARM) may be incorporated to inhibit queuing of interrupts. This may be accomplished by strapping SCLR0C to EBL1 and removing the pull-up resistor at 12RR1. (See 02-123D08-1, Note 2.) The Interrupt flip-flop is held in the clear state until the ARM Command is received from the Processor.

4.5 Write Mode

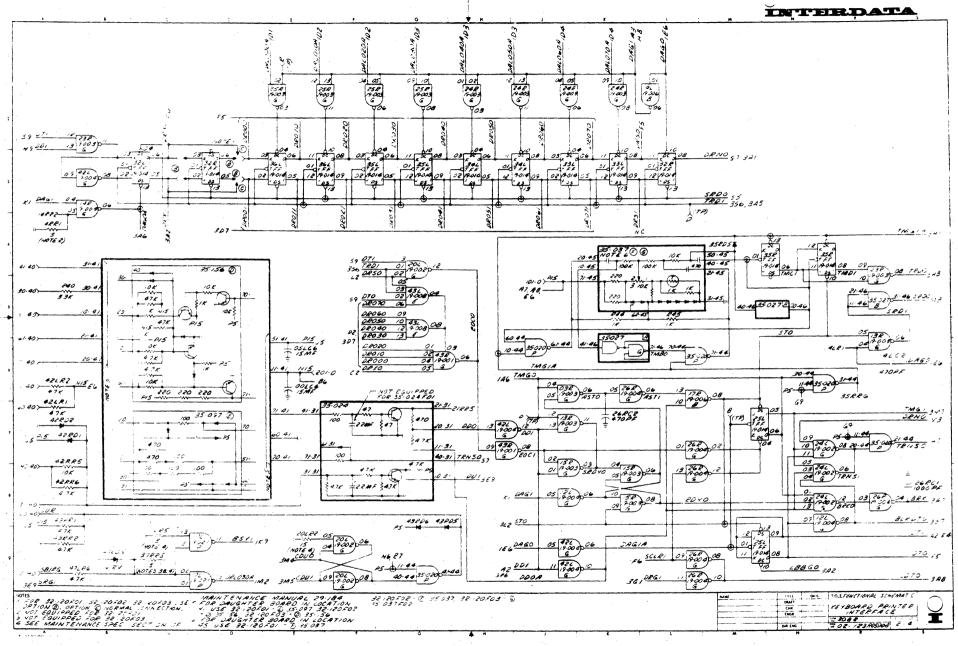

In the Write Mode, the Controller is conditioned for outputting from the Processor to the terminal. The elevenbit Shift Register (02-123D08-2) is used to convert the eight-bit data byte to a ten or eleven-bit serial pulse chain. The register is loaded in the following manner. The leading edge of DAG0 is differentiated to produce SRD0. SRD0 first sets DR00 through DRN0 and clears DRX. The SRD0 pulse is short and disappears before DAG0. On the remaining time of DAG0, data is loaded into register DR01 through DR08 by inserting zeros where they appear on DAL000A through DAL070A, DRN is cleared, and DRX is set for an eleven-bit code or cleared for a ten-bit code. The DT flip-flop is cleared, along with setting the Timing flip-flop, TMG, which starts the timer by DAG1A. With DT1 low, zeros will be shifted into the register and propagated by Shift pulse, TRD1. The serial output from DRN, which is produced by shifting the content of the register, is gated with DT0 and TMG1 to produce TRNS0.

The hardware option of eleven or ten-bit code is obtained by the presence or absence of the fifteen ohm resistor, 14RR1. For an eleven-bit code, resistor 14RR1 is removed to allow DRX to be set for the second Stop bit.

On output, the end of character gate is generated when the content of DRX, DR00 through DR07, is all zeros and TRD1 goes high. The Timing flip-flop, TMG, is cleared by EOC0 which stops the timer. When the timer stops, the last shift pulse is generated and shifts the content of the Shift Register one more time.

The Start bit is contained in DRN and the one or two Stop bits are contained in DRX and/or DR0. One Stop bit for ten-bit code, and two Stop bits for eleven-bit code.

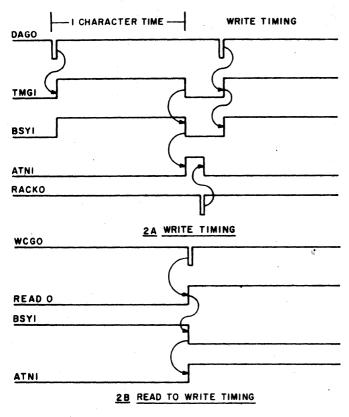

The interface BSY condition goes true in the Write Mode as soon as the timer starts (02-123D08-3). It remains true until the information is shifted from the Data Register. With the detection of End Of Character, the BSY condition goes false and an interrupt is generated by setting the ATN flip-flop (see Figure 2A). When changing from the Read to Write Mode, an interrupt is also generated (see Figure 2B).

#### A-392-1

### TABLE 1.KEYBOARD I/O CONTROLLERSTATUS AND COMMAND BYTE CODING

| BIT<br>NUMBER   | 0        | 1       | 2       | 3             | 4   | 5    | 6    | 7    |

|-----------------|----------|---------|---------|---------------|-----|------|------|------|

| STATUS<br>BYTE  | ERR      |         | BRK     | STBY<br>RING* | BSY | EX   |      | DU   |

| COMMAND<br>BYTE | DISABLE* | ENABLE* | UNBLOCK | BLOCK         | WRT | READ | CB1* | CB2* |

| ERR           |                                        | et when a character is not taken from the controller buffer b<br>e terminal has been assembled. ERR is reset on OC Read, 1<br>ization. |                          |

|---------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| BRK           |                                        | et at the end of one character time when the line is held in the er than a character period.                                           | e space condition        |

| STBY<br>RING* |                                        | used with the General Electric Terminet 300. It is set when<br>he following conditions:                                                | the terminal is on-      |

|               | 1. Manually plac                       | ing terminal in Standby Mode.                                                                                                          |                          |

|               | 2. Issuing an En                       | d Of Transmission character, EOT, to the terminal.                                                                                     | · · ·                    |

|               | 3. When the term                       | ninal is manually placed in the 120 character/second operation                                                                         | n.                       |

|               | When supporting the ON state of the Da | he Terminet 300 via a 103 Data Set, this Status bit indicates t<br>ta Set Ring lead.                                                   | he presence of the       |

| BSY           | Read Mode - The the Processor.         | he Busy bit is normally set and is reset when data is available                                                                        | e for transfer to        |

|               | <u>Write Mode</u> - T<br>terminal.     | he Busy bit is normally reset and is set when data is being tr                                                                         | <b>cansferred</b> to the |

| EX            | The Examine bit is                     | s set when BRK or ERR bits are set.                                                                                                    |                          |

| DU            | The Device Unavai                      | lable bit is set as follows:                                                                                                           |                          |

|               | Terminal                               |                                                                                                                                        |                          |

|               | 33/35 TTY                              | Power off or Local Mode.                                                                                                               |                          |

|               | Mode 37 TTY                            | Power off and when Reader, Punch, and Printer are all off-                                                                             | -line.                   |

|               | Terminet 300                           | Power off or Local Mode.                                                                                                               |                          |

|               | 103A Data Set                          | Carrier lead of the Data Set is in the Off state.                                                                                      |                          |

| DISABLE*      | Disables device int                    | errupts; allows queuing of interrupts.                                                                                                 |                          |

| ENABLE*       | Enables device Inte                    | rrupts.                                                                                                                                |                          |

| UNBLOCK       | Allows Printer to p                    | rint data entered via the keyboard or tape reader.                                                                                     |                          |

| BLOCK         | Disables the UNBLA                     | OCK feature.                                                                                                                           |                          |

3

#### TABLE 1 (Continued)

WRT

The Write Command is used to place the interface in the Write Mode, which allows data to be transferred to the device.

CB1\* CB2\* These two Control bits are decoded to obtain the following interface command.

- CB1 = 0 CB2 = 0

CB1 = 1

This condition is used when operating with the 33/35/37 TTY and to select the 30 character/second rate of the Terminet 300.

CB1 = 1

This condition selects the 120 character/second rate of the

- 2. CB1 = 1This condition selects the 120 character/second rate of the<br/>CB2 = 1CB2 = 1Terminet 300.

- 3. CB1 = 1 This condition places the DUR lead in the ON state. CB2 = 0

- 4. CB1 = 0 This condition places the DUR lead in the OFF state. CB2 = 1

\*See Optional Features (4.11)

#### 4.6 Read Mode

The Controller is placed in the Read Mode by the appropriate Output Command, to transfer information from the terminal to the Processor. The input operation (see 02-123D08, 1 and 2) is initiated when the Start bit of the serial information is received by the input coupling circuits. The Timing flip-flop (TMG) is set when the normal, closed loop, high state of DD1 goes low. The RDY flip-flop has been in the set state, and together with TMG0, will have generated AST0 and AST1. As DD0A goes high, ST0 is generated and sets TMG, DT, TMD, clears RDY, and produces SDR0. SDR0 loads the Shift Register, DR00 through DRN, with all ones. DRX is cleared by SDR0.

Shift pulses (TRD1) are generated which sample the serial data near the center of each bit and insert it, one bit at a time, into the Shift Register. When the Start bit has been shifted through to DR07, the next TRD1 pulse, gated by DRS0 and DT1, generates EOC0. When EOC0 occurs, the timer is stopped and the EOC pulse shifts the Data Register one more time. With the last shift, the Stop bit is contained in DRX.

#### NOTE

On input, the interface is always conditioned for the ten-bit code: One Start, eight Data, and one Stop bit.

The information contained in DR00 through DR07 is transferred to a Byte Buffer Register (02-123D08-3) when the Stop bit is shifted into DRX. When DRX goes high and DRN contains the leading zero, LBBG is generated and gated by READ0 to load the information into the Byte Register (DR001B through DR071B). When the Byte Register is loaded, RB1 goes low, the Controller becomes nonbusy at this time, and an interrupt is generated (see Figure 3). The Controller stays non-busy until the Processor takes the data from the Byte Register. The Byte Register retains the information for one character time.

#### 4.7 Timing Circuits

The timer (02-123D08-2) is a gated oscillator type times and consists of a 35-037 Timing Network, a 35-027 bu Differentiator, and a 35-020 Gated Pulse Inverter. Wroquency of the timer is a function of the 35-037 Timing Network. The following frequencies are used for partacular character rates:

| Option F | 10 characters/second<br>15 characters/second | 440 Hz<br>600 Hz | •             |

|----------|----------------------------------------------|------------------|---------------|

| Option G | 30 characters/second                         | 4800 Hz          | Programmable  |

|          | 120 characters/second                        | 4800 Hz          | Speed Control |

For the ten and fifteen characters/second rate, the basic frequency is divided by four, and the programmable speed control is inhibited by the fifteen ohm resistor, 15RR1. SC1 is forced high, which enables the TRD0A gates for the character rate which requires a division of four. With the resistor 15RR1 removed, the state of the SC flip-flop is under the control of the two control bits, CB1 and CB2. When the SC flip-flop is set (SC1 high), a division of the basic timer frequency is four. A division of sixteen occurs when the SC flip-flop is reset. For the ten and fifteen characters/second rate, the basic frequency is divided by four. The programmable speed control option is not incorporated.

The program speed control option is incorporated by equipping the Controller with the dual JK flip-flop at location 42R (3K2). With the speed control option, the frequency of TRD1 is selected by the state of the SC flip-flop, which is under the control of the two control bits, CB1 and CB2. When the SC flip-flop is set (SC is high), a division of the basic timer frequency is four. A division of sixteen occurs when the SC flip-flop is reset (SC0 is high).

At the 30 and 120 characters/second rates, the basic frequency is divided by four for the 120 characters/second rate, and by sixteen for the 30 characters/second rate.

4.8 Command, Status, and Data Request Circuits

The interface (see 02-123D08-2 and 3) is placed in the different operating modes by an Output Command with the appropriate bit in the byte being set. Bits six and seven of the Command byte are decoded to produce four interface controls.

- 1. Low speed character rate.

- 2. High speed character rate.

- 3. Data Unit Ready (ON).

- 4. Data Unit Ready (OFF).

5

DUR

tional program control of the DUR lead can be incorrated by removing the fifteen ohm resistor, 20LR2. ta Unit Ready has several functions. If the Controller directly connected to a Terminet 300, Model 37 Telebe or equivalent terminal, the DUR lead functions as ta Set Ready ON or OFF. When the above terminals e separated from the Controller by 103A Data Sets, the JR lead serves as Data Terminal Ready ON or OFF. Irmally, this optional feature is not incorporated and be DUR lead is forced in the ON state (DUR = high).

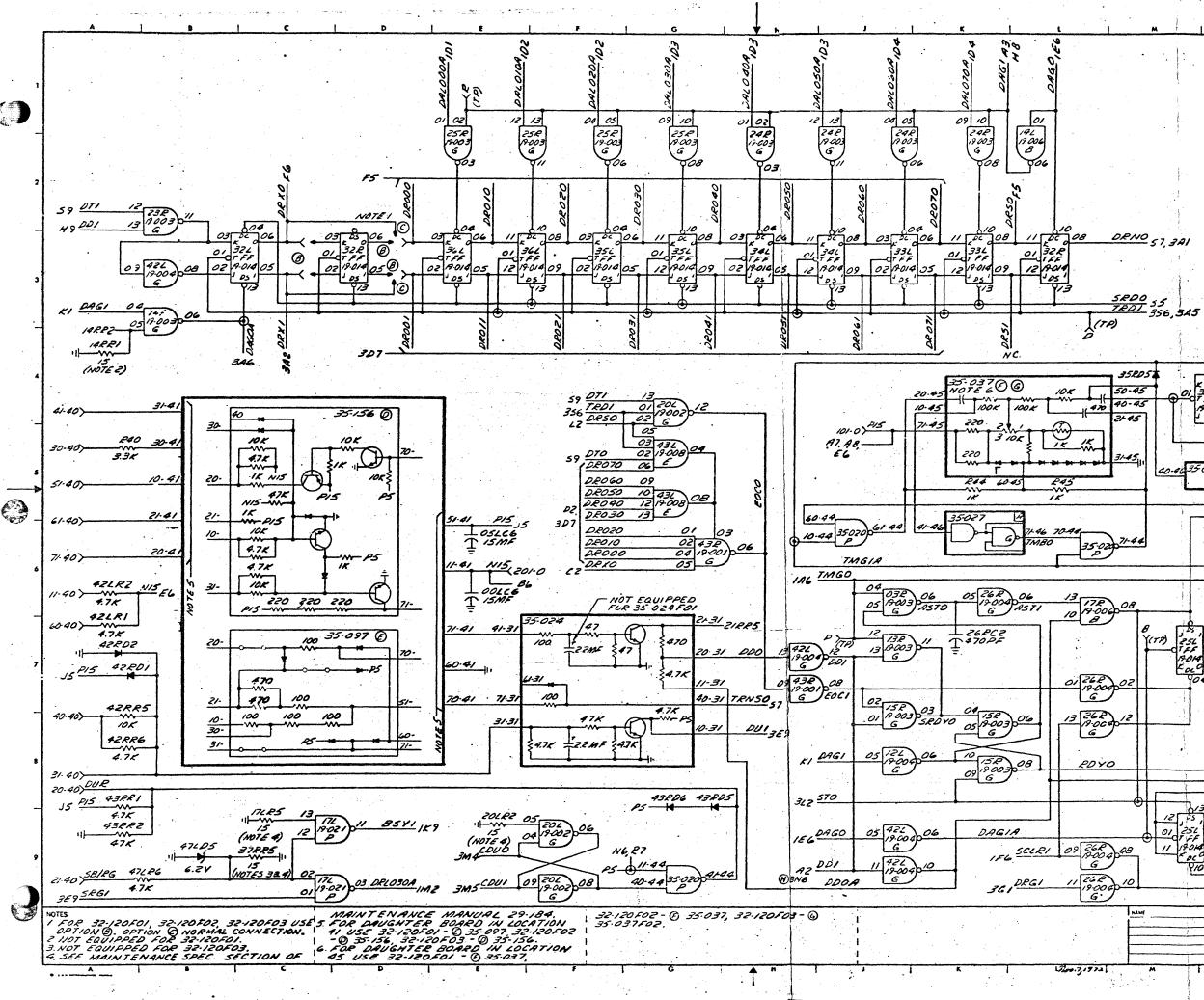

e Status and Data information is returned to the Procesr via DRL000A lines. The Status and Data gates are own on 02-123D08-3.

ne DRG1 pulse gates the true content of the Byte Buffer . gister onto the DRLXX0A lines.

4.9 Coupler Circuits

he coupler circuits (02-123D08-2) adapt the terminals terface to the Controller. Option D (daughter-board i-156) converts the RS 232-B interface levels to levels hich the Controller can accommodate. Option E (daughr-board 35-097) adapts the standard 33/35 TTY to the ontroller.

4.10 Line Break, Block and Unblock Circuits

line break condition is detected if the DD0 (02-123D08-) lead is high (Line condition is spacing) for a period reater than one character time. When the line goes to he spacing condition (DD0 high), the timer starts and uns for one character period, the RDY flip-flop does of get set by the EOC1 pulse because DD1 is still low. This inhibits the setting of the RDY flip-flop. When the mer stops, TMG0, DD0A, and RDY0 are all high and he BRK bit is generated. When BRK1 goes high, the syte Buffer Register is cleared and the BSY bit pulsed by to generate an interrupt. BRK1 remains high as long s the Break condition exists on the line.

n the Write Mode, an incoming line break is detected in similar manner as in the Read Mode. The only differnce is that the RDY flip-flop is reset by DAG1 (02-123 008-2) instead of ST0. If the Controller is idle in the Vrite Mode, the Timing flip-flop is set by ST0 and reset y CTMG0 on detecting the all zeros condition (EOC) in he Shift Register. During the time TMG1 is high (02-23D08-3), the BSY bit is set when TMG1 goes low, BSY oes low and generates an interrupt. If the Controller is ctive and a line break occurs, the BRK bit is set when he timer stops after the character has been transmitted. Iso, at this time, BSY goes low and creates an interrupt.

erial feedback to the printer of the Keyboard/Reader inprmation is controlled by the Block flip-flop (02-123D08-). If the Unblock Command is given to the Controller, the serial output from the receiver (DD0A, 02-123D08-2) is turned around and sent back on the Transmit Line to the terminal. In the Block Mode, the turn-around on the data is inhibited. In the Write Mode, the Block/Unblock function does not affect transmitting to the terminal.

#### 4.11 Optional Features

The following optional features are available:

- 1. Programmable speed control (see Section 4.7, Timing Circuits).

- 2. Programmable control of Data Unit Ready lead (see Section 4.8, Command, Status, and Request Circuits).

- 3. Ten or eleven-bit ASCII code operation (see Section 4.5, Write Mode).

- 4. ARM/DISARM Interrupt service (see Section 4.4, Interrupt Circuit).

- 5. Interrupt or Ring lead going from off to on. Remove fifteen ohm resistor 17LR5. The interface must be in the Read Mode for Ring to generate interrupt.

- Nine-bit operation: one Start, seven Data, and one Stop bit (e.g. 2741 or 1050 terminal). Option B, 02-123D08-2, is normally incorporated for ten or eleven-bit ASCII operation. For ninebit operation, option C is incorporated, which removes the DR00 flip-flop from the Shift Register.

#### 5. TIMING DIAGRAM

Figures 2 and 3 show the timing for the Read and Write Modes of operation for data transfer.

#### 6. MAINTENANCE

**Refer to the vendor** operating and service manuals for maintenance information on the terminal being used. The overall operation of the terminal and interface can be checked by running the appropriate test program (06-004M14 or 06-083M14).

Test points useful for troubleshooting are located on the front edge of the board. See 02-123D08-4.

The only adjustment on the interface is the adjustment of the potentiometer on the timing network 35-037 location 45. A check of the timing can be made as follows:

;

- The width of the negative pulse can be adjusted by the potentiometer on the daughterboard at location 45. To adjust the pulse width, a continuous stream of information is required from the terminal. If an adjustment is required, adjust potentiometer for the time specified in Step 6.

- 8. An alternate method of adjusting the timing is to ground Test Point P instead of Test Point Y, and adjust the potentiometer for the waveform shown in Figure 4.

#### NOTE

The Speed Control (SC) flip flop must be in the proper state when the 30 and 120 characters timing is adjusted.

If the timer cannot be adjusted correctly, check the +15 volts on the interface board.

If still not proper, replace the 35-027 daughter-board in location 46, the 35-037 daughter-board in location 45, and/or the 35-020 daughter-board in location 44 (02-123D08-2).

|      | $\mathbf{v}$                    |

|------|---------------------------------|

|      | IOO MILLISECONDS                |

| - T. | IO CHAR/SEC                     |

| 7."  | F                               |

|      |                                 |

| т    | # 9.09MS IO CHARACTERS/SECOND   |

| ΤI   | = G.GEMS IS CHARACTERS/SECOND   |

| T,   | + 3,35 MS 30 CHARACTERS/SECOND  |

| T    |                                 |

|      | SELEMS IS CHARACTERS/SECOND     |

| Tg   | = 33.3MS 30 CHARACTERS/SECOND   |

|      | = 0.33 MS 120 CHARACTERS/SECOND |

| . 11 | NGO/TP-P(TP) AT GND.            |

Figure 4. Character Timer Adjustment

#### MNEMONIC LIST

he following alphabetical list briefly describes the mnemonics used in the Keyboard Printer I/O Controller. The locaon on 02-123D08 is also provided.

| NEMONIC                            | MEANING                                                                |   | LOCATION                        |

|------------------------------------|------------------------------------------------------------------------|---|---------------------------------|

| D                                  | Address flip-flop.                                                     |   | 1K1                             |

| TN                                 | Attention flip-flop.                                                   | • | 1K8                             |

| TSYN                               | Return Address Strobe.                                                 | · | 1K8                             |

| LK                                 | Block flip-flop.                                                       |   | 3L7                             |

| RK                                 | Line Break Indication.                                                 |   | 2 <b>S</b> 8                    |

| SY                                 | Interface Busy Status.                                                 |   | 388                             |

| L's                                | Control Line                                                           |   |                                 |

| ADRS0<br>DA0<br>DR0<br>SR0<br>CMD0 | Address<br>Data Available<br>Data Request<br>Status Request<br>Command |   | 1A5<br>1A6<br>1A7<br>1A7<br>1A6 |

| DT0                                | Clear on Data Transfer.                                                |   | 2M9                             |

| DU                                 | Control Data Unit.                                                     |   | 3L4                             |

| MG0                                | CMD Signal Gated by AD flip-flop.                                      |   | 1 <b>E</b> 5                    |

| AG0                                | DA Signal Gated by AD flip-flop.                                       |   | 1E6                             |

| AL                                 | Data Available Lines.                                                  |   | 1A1-1A4                         |

| D                                  | Device Data.                                                           |   | 2H7                             |

| R00<br>Irough<br>R07               | Data Register flip-flops.                                              |   | 2E2-2L2                         |

| MNEMONIC    | MEANING                                     |         | e e e e e e e e e e e e e e e e e e e | LOCATION    |

|-------------|---------------------------------------------|---------|---------------------------------------|-------------|

| DRL         | Data Request Lines.                         |         |                                       | 181-184     |

| DRN         | Data Register Contains Start Bit on Output. |         |                                       | 2M3         |

| DRS         | Data Register Contains Start Bit on Input.  |         | •                                     | 2K3         |

| DRX         | Data Register Contains Stop Bit.            |         |                                       | 2C2         |

| DT          | Direction Transfer flip-flop.               |         |                                       | 289         |

| DUR         | Data Unit Ready Lead.                       |         |                                       | 2A8         |

| EBL         | Enable Attention flip-flop                  |         | •                                     | 1K7         |

| EOC         | End Of Character                            | • .     |                                       | 2J7         |

| ERR         | Error                                       |         |                                       | 3E8         |

| EX          | Examine Status Condition.                   | •       |                                       | 3F7         |

| LBBG        | Load Byte Buffer.                           |         |                                       | 3C2         |

| RACK0       | Received ACK Signal.                        |         | • •                                   | 1A8         |

| RDY         | Ready flip-flop.                            |         |                                       | 2K8         |

| SB/RG       | Standby or Ring.                            |         | •                                     | 2A9         |

| SC          | Speed Control.                              |         |                                       | <b>4M</b> 3 |

| SCLR        | System Clear.                               |         |                                       | 1G5         |

| SRD         | Set Data Register.                          |         |                                       | 285         |

| SRG0        | SR Signal Gated by flip-flop.               |         |                                       | 1E6         |

| <b>ST</b> 0 | Start Gate (Read Mode).                     |         |                                       | <b>2J</b> 8 |

| SYN         | System Sync.                                |         |                                       | 1K8         |

| TACK        | Transmitted ACK Signal.                     |         |                                       | 1E9         |

| TMA         | Timer frequency F.                          | · · · · |                                       | 2N5         |

| ТМВ         | Timer frequency F.                          |         |                                       | 2L6         |

| TMC         | Timer Counter F/2.                          |         |                                       | 2N4         |

| TMD         | Timer Counter F/4.                          |         |                                       | 2R4         |

| TME         | Timer Counter F/8.                          |         |                                       | 3K2         |

| TMF         | Timer Counter F/16.                         |         |                                       | 2L2         |

| TMG         | Timer flip-flop.                            |         |                                       | 287         |

| TRD         | Toggle Register Data.                       |         |                                       | 381         |

| TRNS        | Transmit Data to Terminal.                  |         |                                       | 287         |

|             |                                             |         |                                       |             |

•

.

$\bigcirc$ INTERDATA 71D102012 TMGIA 3HI دري د مي 1250 258 7 7 7 TFF 09 23P 11 AOM 08 19-040 06 1. DS TADI OB TROO 3H3 OS TAC 12003 10 21-46 11-46 35.027 31-46 SROOM3 60-46 35027 A 70-40 B SRDI 05/3R 00/700306 570 IALRI. 14LC2 DAGO IEG 470PF 30-94 11.44 35-020 \_\_\_\_\_ 35RRG 69 TMGI 3M7 DRNO M3 23 25L TFF NOMO 69 Earg P5-6 10 24 20 08 20-44 35-020 78 N. 11 G TENSO HT 05 03 242 06 03 19-002 TRN 51 1000 PF 07 02 241 73 6 88800 78 03 26R 04 BRKI 3AT 19-00 G 09/22 19:000 G BLKDTO 357 125 709 DTI 25 -A2,1 01 251 T FF 11 19014 08 070 F5 1 DE 10 LBBGO 3AZ CD 70 -3A8 7/D/020/2 TITLE FUNCTIONAL SCHEMATIC TITLE DATE DRAFT KEYBOARD PRINTER INTERFACE CHK ENGR I 3082 -----2-4 02-123AL 208 DIR LHG