# HP 12825A HDLC Direct Connect Interface Kit installation and service manual

Card Assembly: 5061-3432

Date Code: 2022

# **PRINTING HISTORY**

New editions are complete revisions of the manual. Update packages contain replacement pages or write-in instructions to be merged into the manual by the customer. Manuals will be reprinted as necessary to incorporate all prior updates. A reprinted manual is identical in content (but not in appearance) to the previous edition with all updates incorporated. No information is incorporated into a reprinting unless it appears as a prior update. The edition does not change.

First Edition . . . . . . . . Sept 1980

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

# SAFETY CONSIDERATIONS

**GENERAL** - This product and relation documentation must be reviewed for familiarization with safety markings and instructions before operation.

#### SAFETY SYMBOLS

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect the product against damage.

Indicates hazardous voltages.

Indicates earth (ground) terminal (sometimes used in manual to indicate circuit common connected to grounded chassis).

#### WARNING

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly performed or adhered to, could result in injury. Do not proceed beyond a WARNING sign until the indicated conditions are fully understood and met.

#### **CAUTION**

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, practice, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product. Do not proceed beyond a CAUTION sign until the indicated conditions are fully understood and met.

#### CAUTION

#### STATIC SENSITIVE DEVICES

Some of the semiconductor devices used in this equipment are susceptible to damage by static discharge. Depending on the magnitude of the charge, device substrates can be punctured or destroyed by contact or mere proximity to a static charge. These charges are generated in numerous ways such as simple contact, separation of materials, and normal motions of persons working with static sensitive devices.

When handling or servicing equipment containing static sensitive devices, adequate precautions must be taken to prevent device damage or destruction. Only those who are thoroughly familiar with industry accepted techniques for handling static sensitive devices should attempt to service the cards with these devices. In all instances, measures must be taken to prevent static charge buildup on work surfaces and persons handling the devices. Cautions are included through this manual where handling and maintenance involve static sensitive devices.

SAFETY EARTH GROUND - This is a safety class I product and is provided with a protective earthing terminal. An uninterruptible safety earth ground must be provided from the main power source to the product input wiring terminals, power cord, or supplied power cord set. Whenever it is likely that the protection has been impaired, the product must be made inoperative and be secured against any unintended operation.

**BEFORE APPLYING POWER** - Verify that the product is configured to match the available main power source per the input power configuration instructions provided in this manual.

If this product is to be energized via an auto-transformer (for voltage reduction) make sure the common terminal is connected to the earth terminal of the main power source.

#### **SERVICING**

#### WARNING

Any servicing, adjustment, maintenance, or repair of this product must be performed only by qualified personnel.

Adjustments described in this manual may be performed with power supplied to the product while protective covers are removed. Energy available at many points may, if contacted, result in personal injury.

Capacitors inside this product may still be charged even when disconnected from its power source.

To avoid a fire hazard, only fuses with the required current rating and of the specified type (normal blow, time delay, etc.) are to be used for replacement.

#### WARNING

#### **EYE HAZARD**

Eye protection must be worn when removing or inserting integrated circuits held in place with retaining clips.

# **Definition of Terms**

The following terms are defined as they are used in this manual.

- asynchronous transmission No timing signals are sent with the data. Start and stop bits serve to define transmitted words.

- buffer A segment of contiguous random-access memory locations used for temporary storage of input/output messages.

- card The interface PCA (Printed Circuit Assembly).

- CRC-16 (Cyclic Redundancy Check) An error detection scheme used in data communications.

- DIP (Dual In-line Package) A type of integrated circuit package.

- driver In a hardware sense, a driver refers to a circuit which is capable of supplying specific current and voltage requirements. In a software sense, a driver is a program that is capable of controlling a specific input/output device.

- DS (Distributed System) A term used to refer to networks using Hewlett-Packard Distributed Systems hardware and software products.

- firmware Software code packaged in read-only memory (ROM).

- frame A transmitted message that is formatted according to HDLC protocol.

- full-duplex Communications systems or equipment capable of simultaneous two-way data communication.

- half-duplex Communications system or equipment capable of transmission in either direction, but not both directions simultaneously.

- handshaking The alternating exchange of predetermined signals between two communicating devices for purposes of control.

- host The computer housing the communication card.

- interface A device providing electrical and mechanical compatibility between two communicating devices. The HP 12007A also provides other control features for the associated communication link.

- LED (Light Emitting Diode) A component used on many printed circuit assemblies to provide a visual indication of desired information.

- link Communication lines, modems, and other equipment which permit the transmission of information in data format between two or more devices.

- modem (modulator-demodulator) Equipment capable of digital-to-analog and analog-to-digital signal conversion for transmission and reception via common carrier telephone lines.

- PCA (Printed Circuit Assembly) Interface cards are commonly referred to as PCAs.

- primary The portion of the interface responsible for transmission

processes.

- Primary System A preconfigured operating system included with all HP 1000 Computer systems. It can be reconfigured to meet specific system 1/0 and memory requirements.

- receiver Any device capable of reception of electrically tansmitted

signals.

- secondary The portion of the interface responsible for reception processes.

- synchronous transmission Timing signals are transmitted with the data. No start and stop bits are used. Defined protocol characters must be used to define message blocks or frames.

# **Table of Contents**

| Section I<br>GENERAL INFORMATION    | Page |

|-------------------------------------|------|

| Introduction                        | 1-1  |

| Description                         |      |

| Equipment Supplied                  |      |

| Identification                      |      |

| The Product                         |      |

| The Circuit Card                    |      |

| Installation and Service Manual     |      |

| Specifications                      |      |

| Section II                          |      |

| INSTALLATION                        |      |

| Introduction                        | 2-1  |

| Unpacking and Inspection            |      |

| Computation of Current Requirements |      |

| Firmware Installation               |      |

| ROM Configuration Jumpers           |      |

| DIP Switch Configuration            | 2-6  |

| Card and Cable Installation         | 2-8  |

| Checkout Procedure                  | 2-8  |

| Interface Card Configuration Check  | 2-9  |

| Communication Link Check            | 2-9  |

| Interface Card LEDs                 | 2-10 |

| Section III                         |      |

| PROTOCOL                            |      |

| Introduction                        |      |

| Communications Protocol             |      |

| HDLC Frames                         |      |

| Flag Field                          |      |

| Station Address Field               |      |

| Control Field                       |      |

| Information Field                   | 3-3  |

| Frame Check Sequence Field          |      |

| Error Control                       | 3-4  |

| Frame Sequencing Checks             |      |

| Severe Error Processing             | 3-5  |

| Section IV                          |      |

| PRINCIPLES OF OPERATION             |      |

| Introduction                        |      |

| Hardware Functional Description     | 4-1  |

#### TABLES

| • |  | _ | - | _ |

|---|--|---|---|---|

|   |  |   |   |   |

| Table 1-1 | : Specifications                               | .1-4 |

|-----------|------------------------------------------------|------|

|           | ROM Categories According to Part Type          |      |

|           | : Jumper Requirements for all ROM Combinations |      |

| Table 2-3 | : Switch Assignments                           | .2-6 |

| Table 2-4 | : Transmission Clock Rate Selection            | .2-7 |

| Table 3-1 | : HDLC Protocol Bytes (Control Field)          | .3-4 |

| Table 6-1 | : Replaceable Parts                            | .6-3 |

| Γable 6-2 | : Manufacturer's Code List                     | .6-5 |

| Table 7-1 | : Backplane Connector Pl                       | .7-1 |

| Table 7-2 | : Communication Line Connector Jl              | .7-3 |

|           |                                                |      |

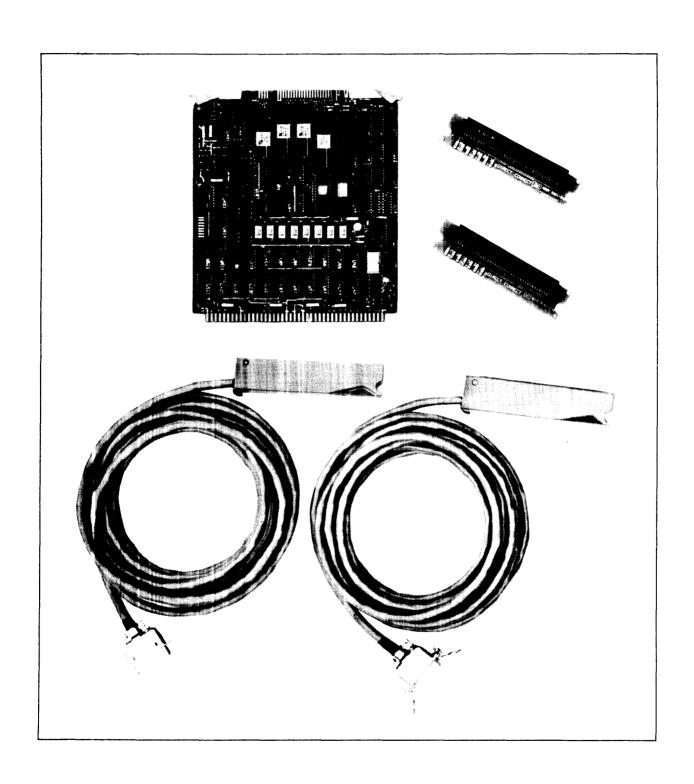

Fig. 1-1. HP 12825A HDLC Direct Connect Interface Kit Contents

# Section 1 General Information

#### Introduction

This manual provides general information, installation procedures, HDLC protocol information, principle of operation, maintenance instructions, replaceable parts information, and servicing diagrams for the HP 12825A HDLC Direct Connect Interface Kit. This section contains general information concerning the HP 12825A including a description and specifications.

# **Description**

The HP 12825A (see Figure 1-1) provides an HP 1000 M/E/F-Series computer with the capability to support a direct connect (hardwired) communications link to another HP 1000 M/E/F-Series computer, or to an HP 1000 L-Series computer. It is used in conjunction with DVR66 of the HP 91750A DS/1000-IV Software.

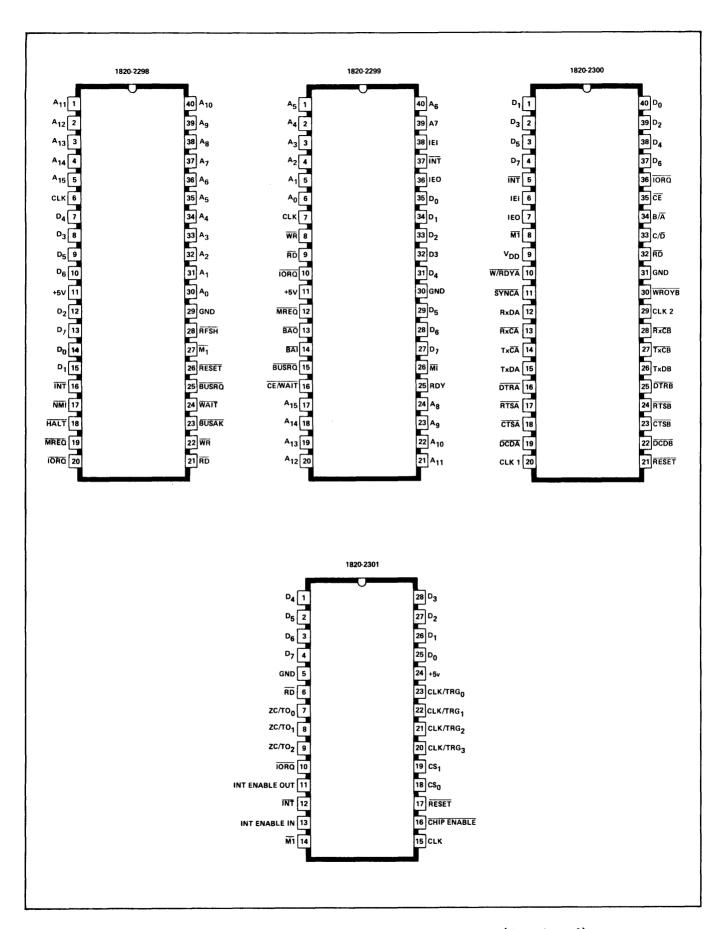

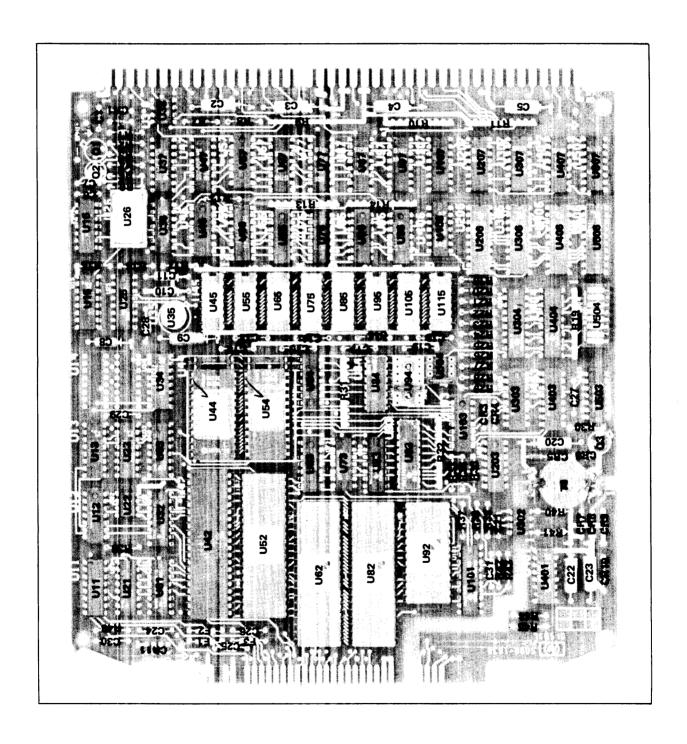

The HP 12825A card plugs into a single I/O slot of an HP 1000 M/E/F-Series Computer and is assigned a single select code. The card contains a Z-80A CPU chip with associated Z-80A support chips and two ROMs containing firmware to implement HDLC protocol. Due to this on-board intelligence, the card is able to relieve a large amount of CPU overhead. Functions such as HDLC protocol generation, CRC-16 block check error control, and a hardware self-test are all handled on the interface card. The Z-80A and on-board RAM also enable the card to maintain long term communications line statistics, and input and output data buffering.

# **Equipment Supplied**

The standard HP 12825A HDLC Direct Connect Interface Kit consists of the following items (see Figure 1-1):

- 1. Programmable serial interface card, HP part number 5061-3432.

- 2. HDLC firmware ROMs, HP part numbers 91750-80008 and 91750-80009.

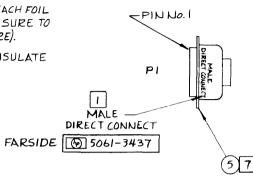

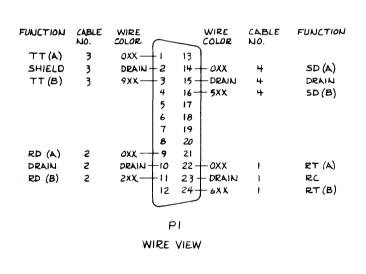

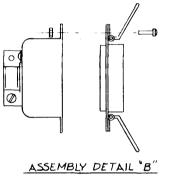

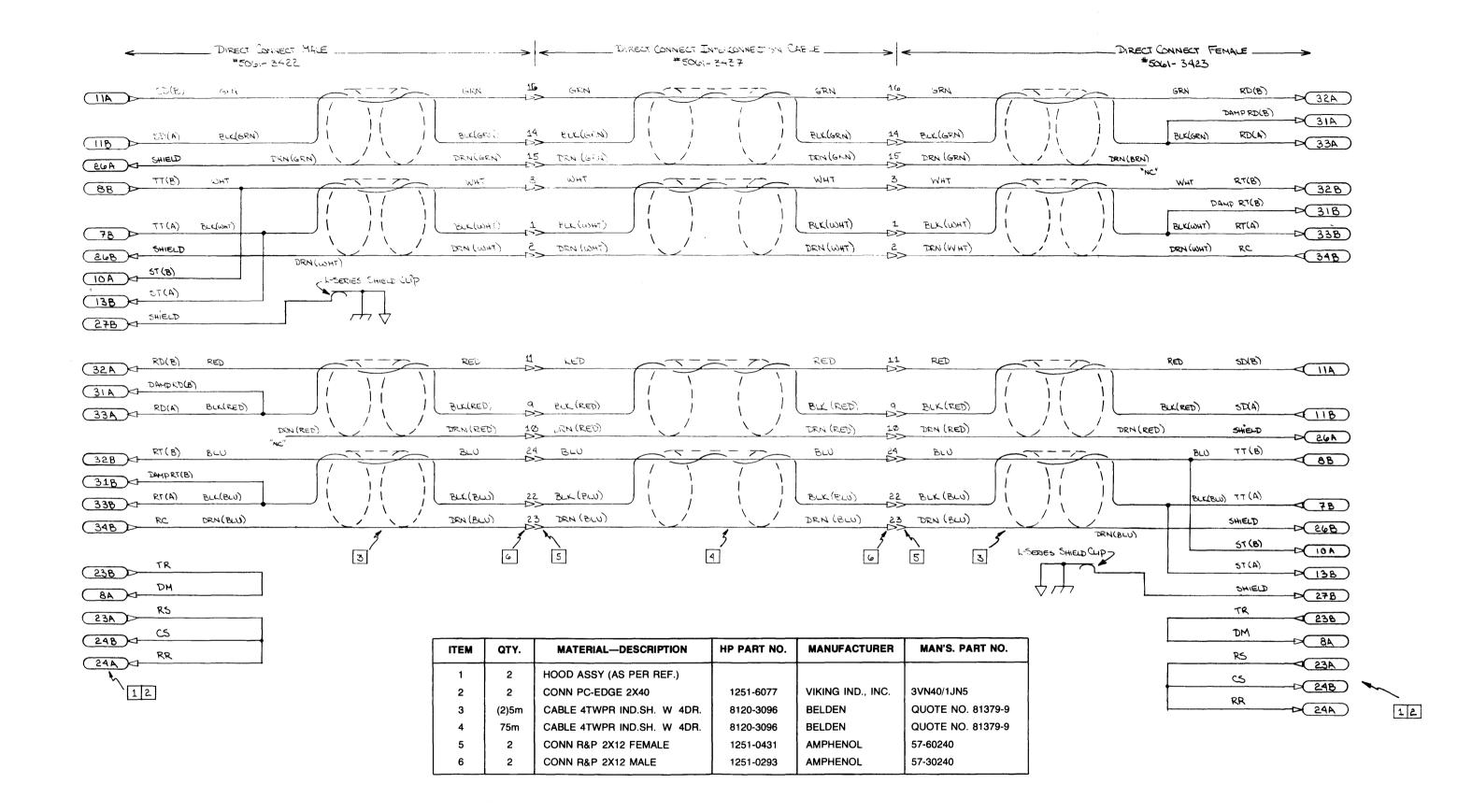

- 3. Direct connect interface cable (5 meter, 16.4 feet) with assembled male connector, HP part number 5061-3422.

- 4. Direct connect interface cable (5 meter, 16.4 feet) with assembled female connector, HP part number 5061-3423.

- 5. Two loop-back verifier hoods, HP part number 5061-3425.

- 6. Installation and Service Manual, HP part number 12825-90001.

The following options are available with the HP 12825A:

- 1. Option 001: Upgrade discount for latest revision of interface firmware (for previously purchased firmware only).

- 2. Option 002: Delete the male and female cables, HP part numbers 5061-3422 and 5061-3423, and delete the two loop-back verifier hoods, HP part number 5061-3421.

- 3. Option 003: Add an interconnection cable (75 meters, 246 feet) with assembled connectors (for extending the direct connect link an additional 75 meters), HP part number 5061-3437.

- 4. Option 004: Add a direct connect connector kit, HP part number 5061-3438, which includes one male and one female connector with hoods and clamps and a wiring diagram.

- 5. Option 005: Add a direct connect custom cable kit which contains one male and one female connector with hoods and clamps, a cable (300 meters, 984.25 feet), and a wiring diagram.

## Identification

#### The Product

Five digits and a letter (12825A in this case) are used to identify Hewlett-Packard products used with HP computers. The five digits identify the product and the letter indicates the revision level of the product.

#### The Circuit Card

The circuit card supplied with the kit is identified by a part number marked on the card. In addition to the part number, the card is further identified by a letter and a date code consisting of four digits (e.g., A-2026). This designation is placed below the part number. The letter identifies the version of the etched circuit on the card. The date code (the four digits following the letter) identifies the electrical characteristics of the card with components mounted. Thus, the complete part number on the interface card could be:

5061-3432 A-2026

If the date code stamped on the HDLC interface card does not agree with the date code on the title page of this manual, there are differences between your card and the card described herein. These differences are described in manual supplements available at the nearest Hewlett-Packard Sales and Service Office (a list of Hewlett-Packard Sales and Service Offices is supplied at the back of this manual).

#### Installation and Service Manual

The manual supplied with the kit is identified by its name and part number. Part number, 12825-90001, and publication date are printed on the title page. If the manual is revised, the publication date is changed and the List of Effective Pages (page iii) reflects the pages involved in the change. The Print History page (page ii) records the reprint dates.

# **Specifications**

Table 1-1 lists the specifications of the HP 12825A HDLC Direct Connect Interface Kit.

Table 1-1. Specifications

TRANSHISSION MODE: Bit serial; synchronous.

TRANSMISSION LINK: Full-duplex over four

individually-shielded twisted

pairs. Lines are optically

isolated at the receivers on the

card.

ISOLATION PROVIDED: 1 kilovolt common mode.

MAXIMUM CABLE LENGTH: 230000 bps: 1 kilometer

57600 bps: 2.2 kilometer

INTERFACE: EIA Standard RS-422 balanced

drivers and receivers.

DATA TRANSFER LENGTH: Selectable frame size (128 or

1024 byte information field

length).

DATA TRANSFER RATE: Approximately 300, 1200, 2400,

4800, 9600, 19200, 57600, or

230000 bps.

ERROR DETECTION: CRC-16 check controlled on the

interface.

ERROR CORRECTION: Retransmission under firmware

control.

POWER: Supplied by host computer as

follows: 1.806A at +5V, 0.272A at +12V, 0.035A at -12V. The total power dissipated is 12.71

Watts.

# Section 2 Installation

#### Introduction

This section provides information on unpacking, inspecting, installing, and checking the operation of the HP 12825A HDLC Direct Connect Interface Kit.

# **Unpacking and Inspection**

Inspect the shipping package immediately upon receipt to detect any evidence of mishandling during transit. If the package is damaged, ask that the carrier's agent be present when the kit is unpacked. Carefully unpack the card and accessories and inspect for damage (scratches, broken components, etc.). If damage is noticed, notify the carrier and the nearest Hewlett-Packard Sales and Service Office listed at the back of this manual. Return the carton and packing material for the carrier's inspection.

After inspecting all components, refer to the equipment supplied paragraph in Section 1 of this manual to ensure that the kit is complete. Also check the part numbers listed in that section against the part numbers on the kit components. If the kit is incomplete, or if an incorrect component has been furnished, notify the nearest Hewlett-Packard Sales and Service Office.

After unpacking, inspecting, and checking part numbers of all parts of the kit, follow installation and checkout procedures as defined in this section.

# **Computation of Current Requirements**

The circuit card in the HP 12825A obtains its operating voltages from the computer power supply through the backplane. Before installing the card, it is necessary to determine whether the added current will overload the power supply. The current requirements of the HP 12825A are listed in the power entry of Table 1-1. Current specifications for all other interfaces can be found in the appropriate Reference or Installation and Service Manuals.

#### Firmware Installation

CAUTION

#### STATIC SENSITIVE DEVICES

THE ROMS, RAMS, AND Z-80A COMPONENTS USED IN THIS PRODUCT ARE SUSCEPTIBLE TO DAMAGE BY STATIC DISCHARGE. REFER TO THE SAFETY CONSIDERATIONS INFORMATION AT THE FRONT OF THIS MANUAL BEFORE REPLACING.

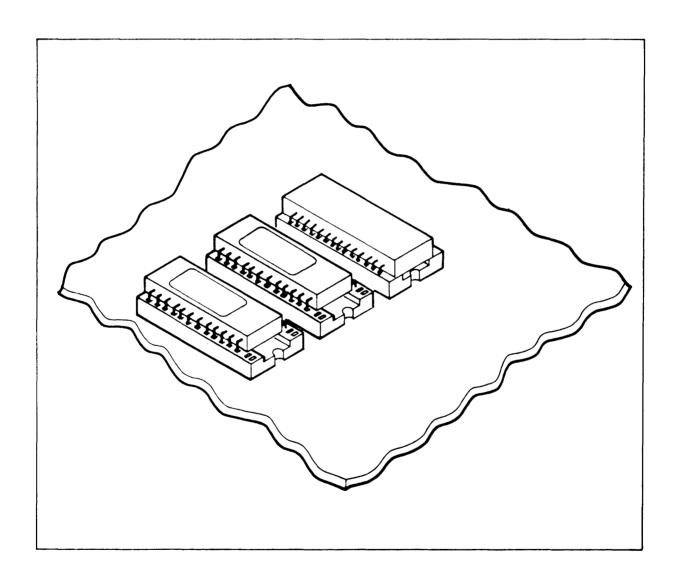

The firmware ROMs (HP part numbers 91750-80008 and 91750-80009) are factory installed in sockets on the card. Make sure that the ROMs are installed as shown in Figure 2-1, and that the part numbers on them match those given in this paragraph.

# **ROM Configuration Jumpers**

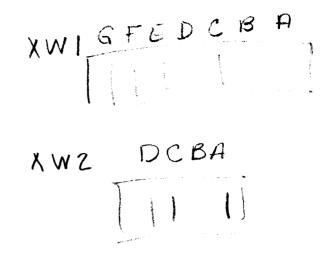

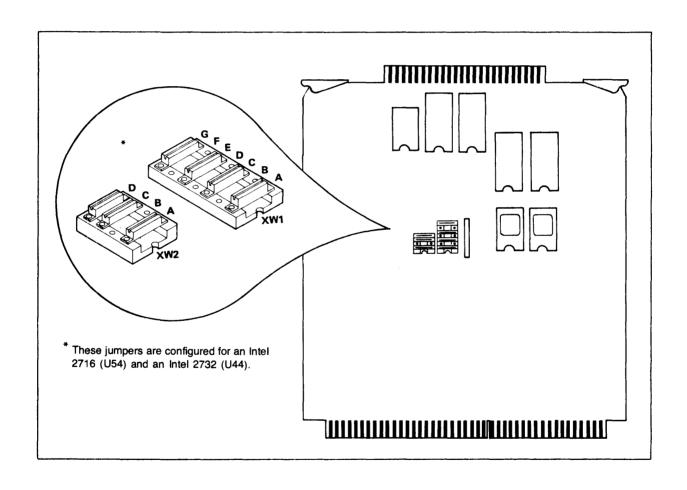

A set of jumpers on the interface card provides the option of using different ROM parts in the future. The set consists of a 14-pin socket housing seven removable jumpers (XWIA through XWIG), and an 8-pin socket housing 4 removable jumpers (XW2A through XW2D). Check to see that all of these jumpers are configured as described in Tables 2-1 and 2-2 for the specific ROMs that are installed. Refer to Figure 2-2 for the location of the socketed jumpers on the interface card.

Table 2-1. ROM Categories According to Part Type

| CATEGORY | HP PART # | PART TYPE                |    |

|----------|-----------|--------------------------|----|

| A        | 1818-0762 | TI 2532                  | 44 |

| В        | 1818-0498 | TI 2516<br>Intel 2716    | 54 |

| С        | 1818-0850 | Intel 2732               |    |

|          |           | Intel 2332<br>Intel 2364 |    |

Table 2-2. Jumper Requirements for all ROM Combinations (X denotes a required jumper; DC denotes a "don't care")

| CATE | I    | X<br>W<br>1 | X<br>W<br>1 | X<br>W<br>1 | X<br>W | X<br>W<br>1 | X<br>W<br>1 | X<br>W<br>1 | X<br>W<br>2 | X<br>W<br>2 | X<br>W<br>2 | X<br>W<br>2 |

|------|------|-------------|-------------|-------------|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| บ54  | U4 4 | A           | В           | С           | D      | Е           | F           | G           | A<br>D      | B           | c<br>B      | PA          |

| С    | С    |             |             |             |        | х           |             |             | х           |             | DC          | DC          |

| A    | A    |             |             |             | х      | x           | x           | х           | х           |             | DC          | DC          |

| С    | A    |             |             | х           |        | х           | Х           |             | х           |             | DC          | DC          |

| B    | (A)  |             |             | Х           |        | Х           | х           | X           | x           |             | DC          | DC          |

| В    | В    |             |             | х           | х      | х           | х           | х           | х           |             | DC          | DC          |

| A    | С    | Х           |             |             |        | х           |             | х           | х           |             | DC          | DC          |

| С    | В    | Х           |             |             | Х      | х           | х           |             | х           |             | DC          | DC          |

| A    | В    | X           |             | х           | Х      | х           | Х           | Х           | х           |             | DC          | DC          |

| В    | С    | х           |             | Х           |        | х           |             | Х           | х           |             | DC          | DC          |

Fig. 2-1. ROM Installation

Fig. 2-2. ROM Configuration Jumper Positions

# **DIP Switch Configuration**

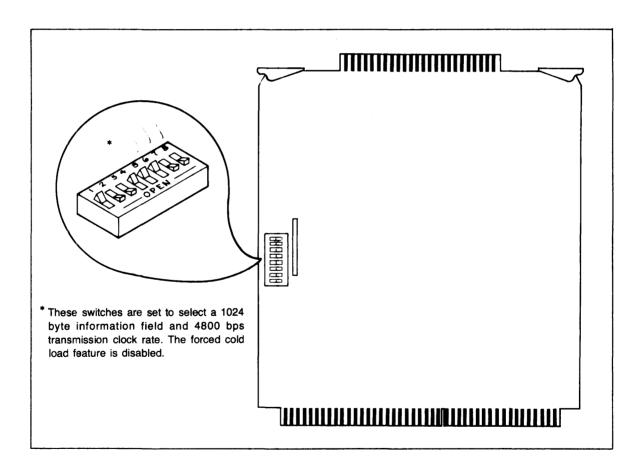

The HP 12825A card provides a Dual In-line Package (DIP) containing eight switches which may be sensed by the firmware. This set of switches is used to determine the information field size, and the transmitting clock rate and associated time-out values (time-outs are firmware controlled and not user programmable). The card sends a clock with transmitted data and receives a clock with received data. Therefore, the two communicating cards can have different transmission rates as selected by this switch. In addition, switch number 1 physically enables the ability to control a forced cold load from a remote node. Configure the switch as necessary using the switch assignments given in Tables 2-3 and 2-4. Refer to Figure 2-3 for switch position on the card.

Table 2-3. Switch Assignments

|   | SWITCH | FUNCTION                                                                           |

|---|--------|------------------------------------------------------------------------------------|

| 7 | 1 -0,  | Closed to enable forced cold load (FCL)/slave request. Open to disable.            |

| 7 | 2-Ope  | Closed to select 1024 byte information field.                                      |

|   |        | BOTH ENDS OF THE LINK MUST HAVE THIS SWITCH<br>SET THE SAME TO AVOID DATA OVERRUN. |

|   | 3,4,5  | Not used.                                                                          |

|   | 6,7,8  | Select transmission clock rate. See Table 2-4.                                     |

<sup>\* 128</sup> byte information field is the recommended configuration for minimizing frame retransmissions.

Table 2-4. Transmission Clock Rate Selection

| SWITCH<br>SETTINGS<br>6,7,8 | CLOCK RATE (bps) |                        |

|-----------------------------|------------------|------------------------|

| 8.7.6                       |                  | NOTE:                  |

| 600                         | 300              | X = closed = logic "1" |

| O OX                        | 1200             | 0 = open = logic "0"   |

| OXO                         | 2400             |                        |

| oxx                         | 4800             |                        |

| X00                         | 9600_            | ,                      |

| XOX                         | 19200            |                        |

| XXO                         | 57600            |                        |

| XXX                         | 230000           |                        |

Figure 2-3. DIP Switch Position

#### Card and Cable Installation

#### **CAUTION**

ALWAYS TURN POWER OFF TO THE COMPUTER AND OTHER ASSOCIATED EQUIPMENT WHEN INSERTING OR REMOVING INTERFACE CARDS OR CABLES. FAILURE TO DO SO COULD RESULT IN DAMAGE TO THE EQUIPMENT.

- Install all cables to be used to connect the two interfaces being installed. Wiring diagrams for the cables and for building extension cables are supplied in Section 7 of this manual.

- 2. Turn off power at the computer. Install the interface card in the desired slot in the computer card cage, noting the select code. The card should be oriented the same as all other cards in the computer: components on the top side of the card. Press the card firmly into place.

- 3. Connect all cables to be used with the interface cards. Power should be turned off at the remote computer also before installing cables on the remote interface.

- 4. Restore power to the computer.

- 5. Initialize the new link into the network as specified in the HP 91750A DS/1000-IV Network Manager's Manual, HP part number 91750-90003.

- 6. Perform the checkout procedure on the card as specified in the next paragraph.

## **Checkout Procedure**

For checkout after installation, perform the interface card and communication link checks described below.

### **Interface Card Configuration Check**

Since the interface card self-test is run each time that power is applied to the card or the card is reset, the first part of checkout is automatically performed. The following procedure will verify that the card passed the self-test and that the backplane interface circuitry is operational. It also provides a way to check the card configuration switch settings. To perform the check, enter the following commands:

#### 1. RU, DSINF <cr>

DSINF is a DS/1000-IV utility program that can be used to obtain information such as network configuration, communications parameters, etc. For more information on DSINF, refer to the Network Manager's Manual.

#### 2. LU, ##, AL<cr>

LU will return information on the configuration of a specified DS/1000 IV interface card, where ## is the LU (Logical Unit number) of that card. Information will only be returned if the card passed the self-test.

In this way, DSINF will return card configuration information as well as other useful parameters. Check to see that the returned information complies with desired card configuration. If the returned values are unexpected, check the switch settings on the interface card. If in error, reconfigure the switch and reinstall the card, going through all checkout procedures again.

#### **Communication Link Check**

Before following the procedure described in this paragraph, it is important to understand the message re-routing capabilities of the network. If there is an alternate path to the remote node being tested, message re-routing must be disabled to ensure that the desired link is being exercised. Check with the network manager about network topology and message re-routing before proceeding.

A good check of the communication link is accomplished by exercising a few REMAT commands. To do this, type in the following commands after the system prompt (:):

#### 1. :RU, REMAT(cr>

REMAT is the program that handles operator commands for communications from one HP 1000 to another in a Distributed Systems network. It schedules the appropriate monitors to

handle all outgoing and incoming requests. REMAT will prompt with a dollar sign (\$) when commands are referred to the local node only. When a remote node is referenced (another HP 1000), the prompt will become a number sign (#).

#### 2. \$SW,NODE1,NODE2,SC<cr>

The SW (Switch) instruction defines the action and destination nodes. Set NODE1 to the node number of the neighbor node that is to be exercised. Set NODE2 to the local node's number. SC is the security code for the network. It is defined when the network is initialized.

#### 3. #TI<cr> OR #TM<cr>

The TI and TM (Time) commands will obtain the time from the remote node and display it on the local terminal being used for this exercise. The TI command should be used if the remote node is an HP 1000 M/E/F-Series computer. The TM command should be used if the remote node is an HP 1000 L-Series computer. If the remote node does not have the necessary monitor to handle the TI or TM command, or does not have a real-time clock, try a DL (Directory List) command or a CL (Cartridge List) command.

#### 4. #EX<cr>

The EX (EXit) command will end REMAT.

If the above procedure is carried out successfully, the described results will be displayed with no error messages returned. If an error message is returned, refer to error code information supplied in the DS/1000-IV User's Manual, HP part number 91750-90002. For troubleshooting procedures, refer to Section 5 of this manual or the troubleshooting section of the DS/1000-IV Network Manager's Manual, HP part number 91750-90003.

# **Interface Card LEDs**

There are four Light Emitting Diodes (LEDs) on the interface card. Located on the left side of the card next to the front edge connector, the LEDs are visible when the card is installed in the computer and are referenced as 0 through 3 with 0 being the LED on the right. During normal operation, LEDO and LED1 are used by the firmware to indicate certain card states and are subject to change with different firmware releases. LED2 and LED3 should be off during normal operation. The LEDs are also used to indicate successful completion of the self-test with all four being off after the test and before DS software has been initialized.

# Section 3 Protocol

#### Introduction

There are several levels of protocol involved in an HP DS/1000-IV communications link. Two of these levels are handled on the HP 12825A: line protocol and communications protocol. The first level involves timing and control signals, and electrical specifications for computer-to-modem connections. The second level involves the more complex set of rules used to control the flow of data over the communication link. Both line and communications protocols are firmware controlled on the HP 12825A. This section will present an abbreviated discussion of the communications protocol. For information on the line protocol, refer to the Communication Line Interface paragraphs in Section 4 of this manual. For a more thorough understanding of HDLC, refer to the HP Computer Systems Group Data Communications Standard, October 1977.

### **Communications Protocol**

The HP 12825A is programmed via the read-only memory (ROM) on the card to implement High Level Data Link Control (HDLC) protocol. HDLC is a bit oriented protocol designed for use over full-duplex communications channels. The following paragraphs discuss the main characteristics of HDLC.

# **HDLC Frames**

Data transfers using HDLC protocol are bit oriented as opposed to character oriented. Blocks of data are transmitted in frames, a frame being a bit stream starting and ending with a flag character. For this implementation, the flag character is the following bit pattern:

#### 01111110

A frame may or may not contain data but always contains control information. There can be any number of frames in a single transmission.

A frame consists of several fields as illustrated in Figure 3-1 and described in the following paragraphs.

Figure 3-1. HDLC Frame Format

#### Flag Field

HDLC uses positional significance, not control characters, to identify the various elements of a message. The flag field is the first eight bits of a frame and the receiver uses it to count down the incoming bit stream to identify the other fields within the frame. The close flag is used to indicate the end of the frame. The firmware also uses the close flag to count back to the frame check sequence field.

Zeroes are inserted and deleted as required to prevent a flag bit pattern from appearing within the frame. When five l's appear, a 0 is inserted in the bit stream after the last l. The receiver detects the five l's followed by a 0 and deletes the 0. The inserted and deleted zeroes are not included in the frame check sequence. This zero insertion/deletion scheme is controlled by the Z-80A SIO chip on the HP 12794A card.

Each interface on the link is continuously seaching for the flag pattern. During lulls in message flow, a series of flags is transmitted to keep the link active and synchronized.

#### Station Address Field

Since all links in a DS network are point-to-point, station address information is not needed as such. Instead, this field is used to convey whether the frame contains a response or a command. This information is necessary due to the data handling organization at each station on the link. Outgoing commands and incoming responses are handled by the primary portion of the firmware driver. Incoming commands and outgoing responses are handled by the secondary portion of the driver. This primary/secondary scheme is one way of implementing a full-duplex communications protocol.

#### **Control Field**

The control field consists of eight bits containing a command or response pattern required for control of the data link. The primary station uses the field to command the secondary to perform an operation. The secondary uses it to respond to the primary. The control field has three formats, indicating the contents and purpose of the frame as follows (refer to Table 3-1 also):

- 1. Information Transfer. This control field format indicates that the present frame contains information being transfered from the local primary to the remote secondary.

- 2. Supervisory Response. A frame with a supervisory format in the control field contains no information (the information field is interpretted to be of zero length), and is used to regulate traffic and request retransmission of missed or erroneous frames.

- 3. Unnumbered Command/Response. This format consists of commands and responses used to establish or disconnect the communications channel, or reject commands (those not recoverable by retransmission).

#### Information Field

A non-zero length information field only exists in frames designated as information transfer frames by the control field. When used, the information field is the vehicle for moving data between stations and it is unrestricted in format and contents. Information field length is selected to be 128 or 1024 bytes (corresponding to external and internal clock selection) using one of the configuration switches on the card.

# Frame Check Sequence Field

This field is 16 bits in length and preceeds the closing flag. When information is present in the frame, it follows the information field, otherwise it follows the control field. Its purpose is to detect errors that occur during transmission. For the HP 12794A, the frame check sequence is computed under firmware control using the CRC-16, cyclic redundancy check, block check method. This consists of dividing a constant into the first group of bits being transmitted after the opening flag. The quotient is discarded and the remainder added to the next group of bits, which is again divided by the same constant. This continues until the closing flag is detected and the 16-bit CRC-16 remainder is sent in the frame check sequence field before the closing flag.

Table 3-1. HDLC Protocol Bytes (Control Field)

| TYPE                                                                                                 | MNEMONIC  | DESCRIPTION                          | 7 | 6        | El<br>5 | NCOD:  |    | 2 | 1 | 0      |

|------------------------------------------------------------------------------------------------------|-----------|--------------------------------------|---|----------|---------|--------|----|---|---|--------|

| INFO.                                                                                                | I         | Information                          |   | Nr       |         | P      | Ns |   |   | 0      |

| SUPRV.                                                                                               | RR<br>RNR | Receiver Ready<br>Receiver Not Ready |   | Nr<br>Nr |         | F<br>F | 0  | 0 | 0 | 1<br>1 |

|                                                                                                      | REJ       | Reject                               |   | Nr       |         | F      | 1  | 0 | 0 | 1      |

| UNNUM.                                                                                               | SARM      | Set Asynchronous                     | 0 | 0        | 0       | 0      | 1  | 1 | 1 | 1      |

|                                                                                                      | DISC      | Disconnect                           | 0 | 1        | 0       | 0      | 0  | 0 | 1 | 1      |

|                                                                                                      | UA        | Unnumbered Acknowl.                  | 0 | 1        | 1       | 0      | 0  | 0 | 1 | 1      |

|                                                                                                      | CMDR      | Command Reject                       | 1 | 0        | 0       | 0      | 0  | 1 | 1 | 1      |

|                                                                                                      | S IM      | Set Initial. Mode                    | 0 | 0        | 0       | 0      | 0  | 1 | 1 | 1      |

| Abbreviations:  P - Poll bit  F - Final bit  Nr - Send Sequence Number  Ns - Receive Sequence Number |           |                                      |   |          |         |        |    |   |   |        |

# **Error Control**

As described in a previous paragraph, CRC-16 is used by the HP 12825A to detect errors in transmitted frames. There are other types of error control methods used on the link as described in the following paragraphs.

# Frame Sequencing Checks

Sequencing counts are kept on each interface card and transmitted as necessary to acknowledge frames received correctly. The values of these counts are sent in the control field as the following variables:

Ns - Send Sequence Number.

Ns is only transmitted in information frame control words and is used to tell the receiver the number of the frame being sent.

Nr - Receive Sequence Number.

Nr is transmitted in the control field for supervisory and information frames only and is used to acknowledge correct frame reception. The value of Nr sent is equal to the number of the next frame that is expected.

The counts kept for Nr and Ns are only incremented when frames containing information are sent or received. Supervisory and unnumbered command/response frames do not affect these counts. These frames are acknowledged by proper response words. By keeping track of frames sent and received in this manner, it is possible for transmitting stations to transmit frames before the response is returned for previously transmitted frames. Also, one response can serve to acknowledge more than one received This scheme increases overall link throughput. The number of unacknowledged frames allowed in this implementation of HDLC is seven. After that, outgoing messages are put in a queue and sent only when the proper response is received.

If a sequence error is detected by a transmitting station, it will retransmit the frame after the last acknowledged frame and set the P (Poll) bit to signal that it is a retransmission. The P bit set also demands that the receiving station respond with a supervisory frame instead of the standard information frame acknowledgement. In the response supervisory frame, the F (Final) bit is set to indicate that it is responding to a received poll.

#### **Severe Error Processing**

The HP 12825A card is capable of detecting other types of errors besides invalid frames (CRC-16 detected errors) and sequence errors. The other detectable errors are referred to as severe errors and include such cases as:

- \* Unknown frame type

- \* Information field larger than available frame buffer

- \* Ns greater than seven

- \* Failure to acknowledge after maximum allowable retries

These errors are reported to the software driver by the firmware on the card, and then an attempt is made to recover. For failure to acknowledge, the link is reset. This is similar to the original connect sequence (see Section 4, Principles of Operation, of this manual). For the other severe errors, a command reject frame is sent.

# Section 4 Principles of Operation

#### Introduction

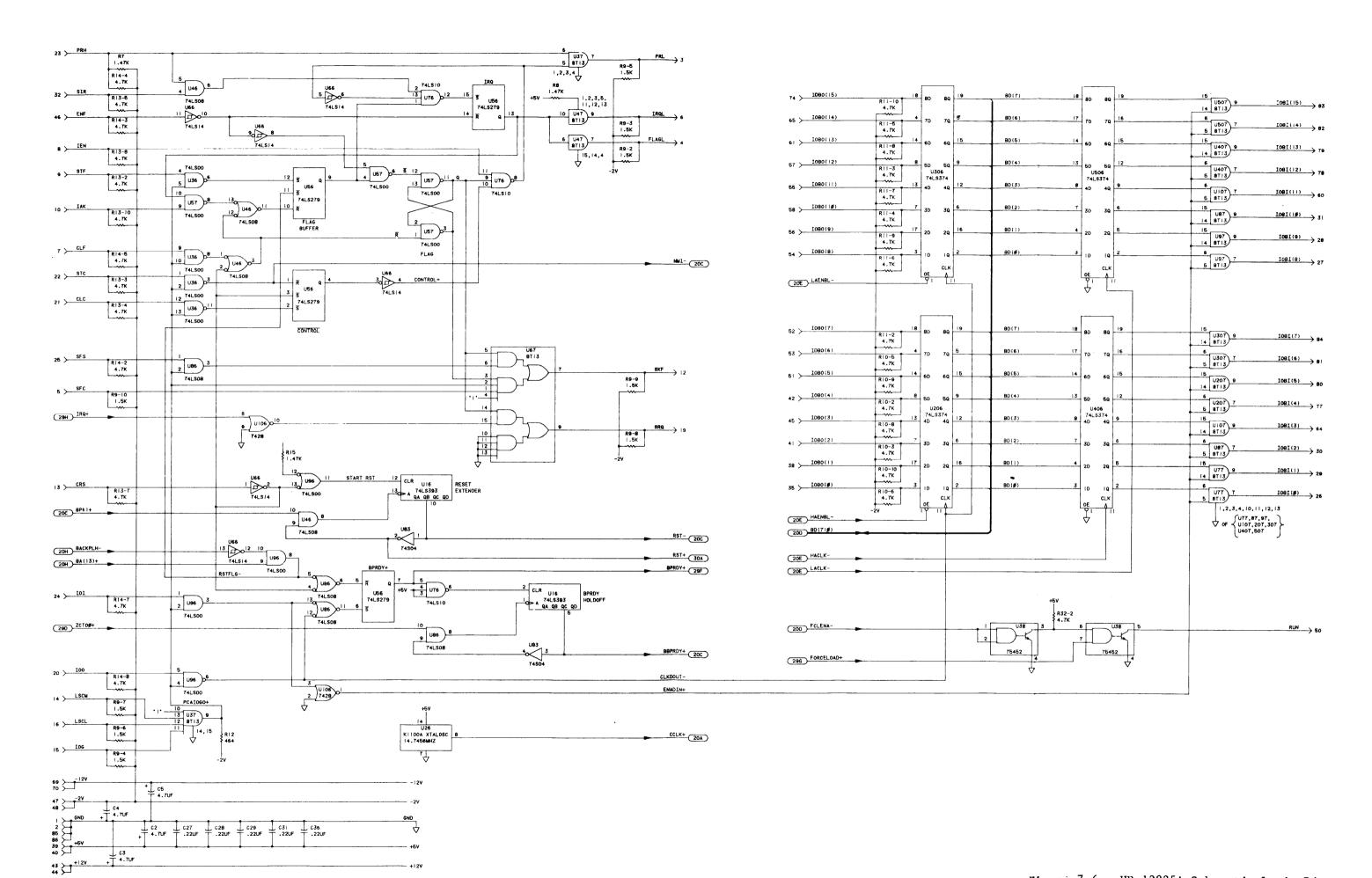

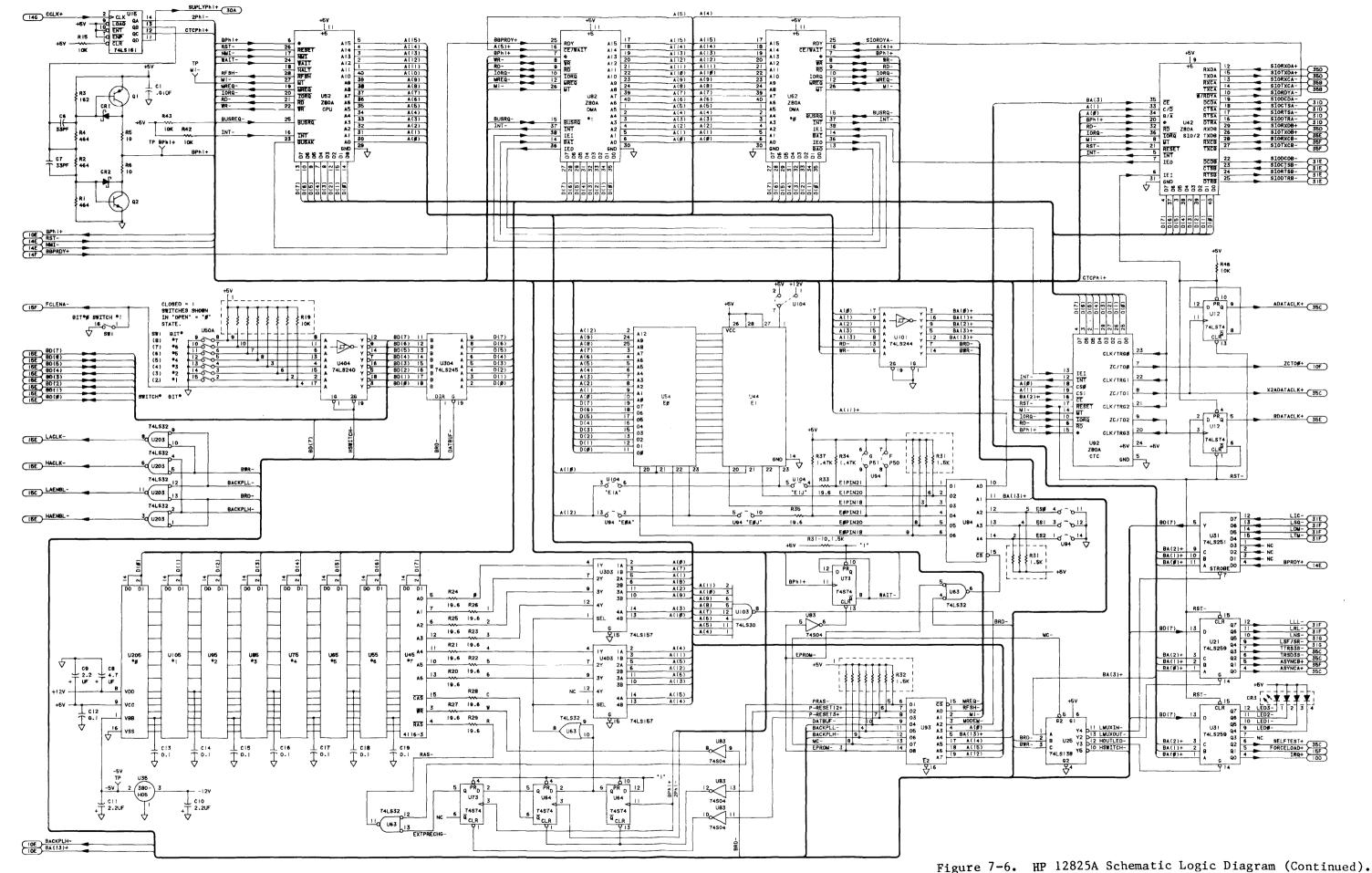

This section contains a description of the operation of the interface card included in the HP 12825A HDLC Direct Connect Interface Kit. The hardware is described in terms of five major functional areas. A brief explanation of the command and status words used in communication between the card and the host computer is also given. The last part of this section is devoted to a functional-level description of the operation of the card.

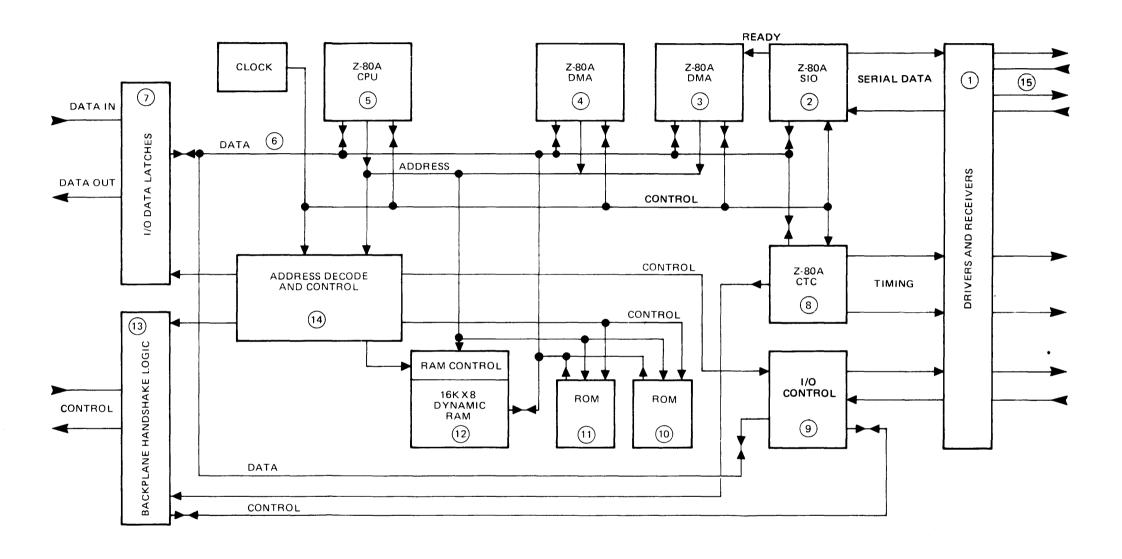

# **Hardware Functional Description**

The card, HP part number 5061-3418, includes the following major functional areas:

- \* HP 1000 M/E/F-Series Computer I/O backplane interface

- \* Z-80A Microprocessor family subsystem (CPU, SIO, DMA and CTC)

- \* Read-Only Memory (ROM)

- \* Random-Access Memory (RAM)

- \* Communication line interface

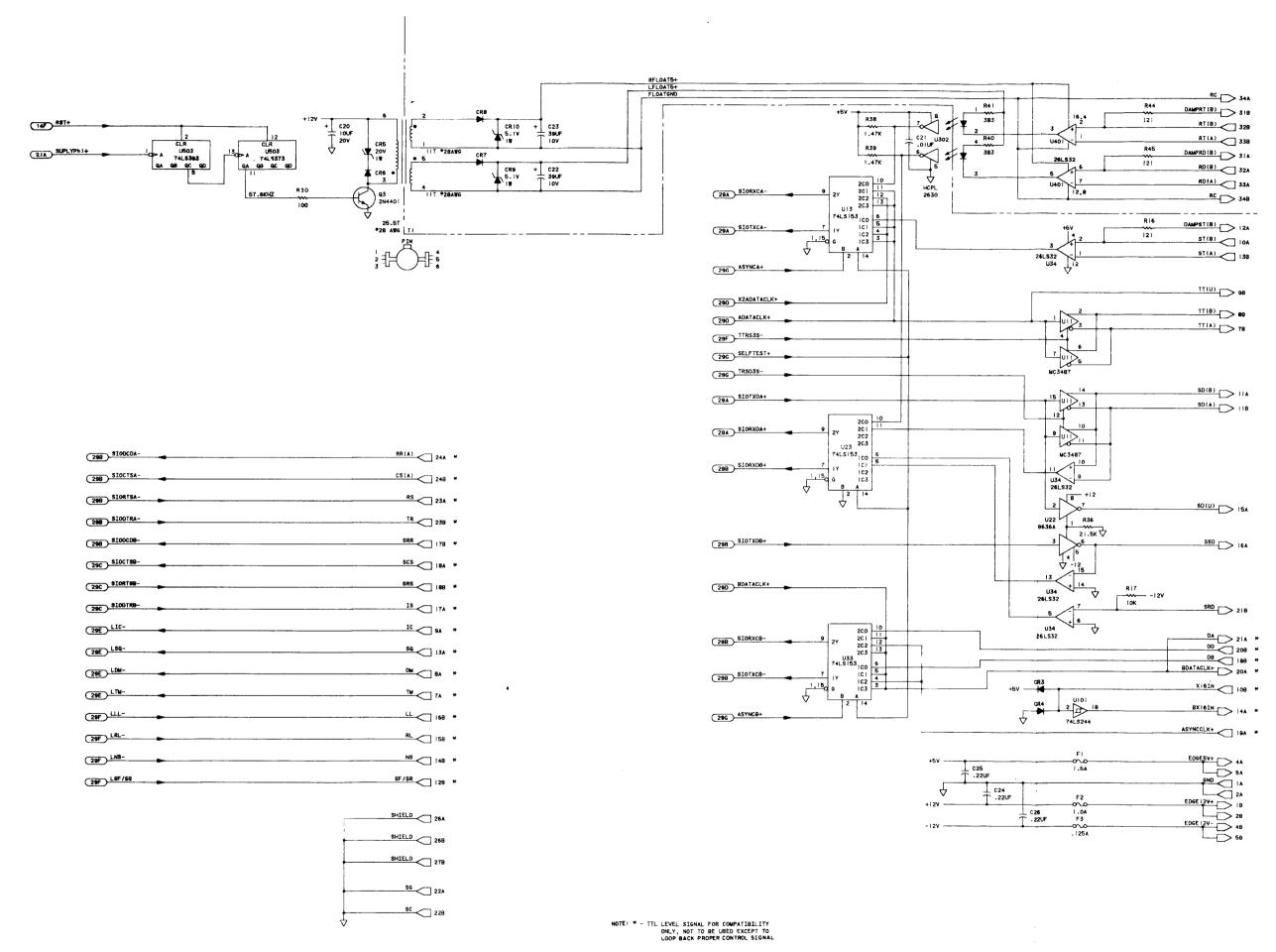

A block diagram illustrating the major functional areas of the card is presented in Figure 4-1.

# Host Computer I/O Backplane Interface

The card communicates with the HP 1000 host computer over the I/O backplane. The backplane interface circuitry can be logically divided into two major sections: the I/O data latches and the control circuitry section.

The I/O data latches consist of two 8-bit input latches and two 8-bit output latches. The input latches hold 16-bit data or command words from the host computer until the card is ready to accept them. Likewise, the output latches hold 16-bit data or status words output from the card to the host computer.

The control circuitry is made up of five flip-flops and other gate-level logic elements. The primary function of this section is to handle the control signals to and from I/O backplane. These signals are used to generate and acknowledge interrupts, to handshake data between the host and the card and to conform to the standard HP 1000 computer I/O backplane signal conventions. For a more detailed discussion of these signals, refer to the HP 1000 M/E/F-Series I/O Interfacing Guide, HP part number 02109-90006.

#### The Z-80A Microprocessor Subsystem

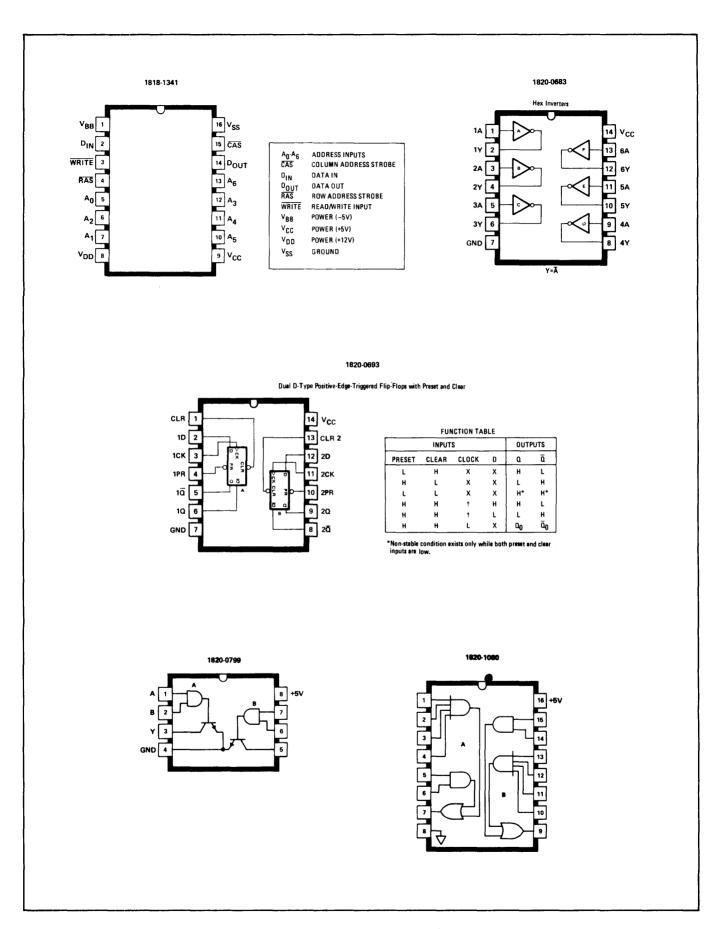

The heart of the card is the Z-80A CPU (Central Processing Unit). This MOS LSI microprocessor operates from a single 5 volt supply, uses a single phase clock and has a typical instruction execution time of 1.0 microsecond. The data bus is eight bits wide and the address bus is 16 bits wide. All CPU pins are TTL compatible.

The Z-80A CPU employs a register-based architecture which includes two sets of six general-purpose registers which can be used as 8-bit registers or 16-bit register pairs. Additional 8-bit registers include two sets of accumulator and flag registers, and the interrupt vector and memory refresh registers. Additional 16-bit registers include the stack pointer, program counter and two index registers. The Z-80A CPU provides the intelligence for the card to function as a preprocessor to relieve the host computer of a majority of the protocol processing.

An important pin on the Z-80A as far as this card is concerned is the NMI (Non-Maskable Interrupt) input pin. By pulling this input low with an STC instruction, the host computer can "get the attention of" the Z-80A. An NMI is the highest priority interrupt to the Z-80A and forces it to start fetching and executing instructions from a predetermined location in the firmware. The host software driver uses this feature to inform the card that it requires service.

Various support chips are used in conjunction with the Z-80A CPU to facilitate the card's operation as an intelligent serial interface. These chips are discussed in the paragraphs that follow.

#### Serial Input/Output (SIO)

A Z-80A SIO chip is used on the card to provide the serial data communications channel. The major functions performed by the SIO chip are serial-to-parallel conversion of input data and parallel-to-serial conversion of output data.

#### **Direct Memory Access (DMA)**

The card uses two Z-80A DMA chips which are LSI DMA controllers. One of these DMA chips is used to transfer data from the SIO Channel to the card memory; the other is used to transfer data between the host computer and the card memory. The primary function of the DMA logic is to transfer bytes of data in a manner that will be transparent to the Z-80A CPU software. This enables the card to achieve higher throughput rates.

#### **Counter Timer Circuit (CTC)**

The card uses one Z-80A CTC chip which provides four independent counter/timers. One of the counter/timers is used as a baud rate generator and two are used as timers for the HDLC protocol. The fourth is used to maximize the effective card throughput by controlling the frequency of DMA cycle stealing.

#### Read-Only Memory (ROM)

The card uses 8k bytes of ROM on two chips. All of the software required to implement the functions of HDLC protocol generation and backplane interaction control is contained in these chips and is referred to as firmware. The self-check routine is also contained in ROM.

#### Random-Access Memory (RAM)

The card has 16k bytes of dynamic RAM. This memory is used for data buffers and the storage of firmware variables. The refresh capability of the Z-80A CPU is used to provide the appropriate refresh signals to the dynamic RAM chips.

#### **Communication Line Interface**

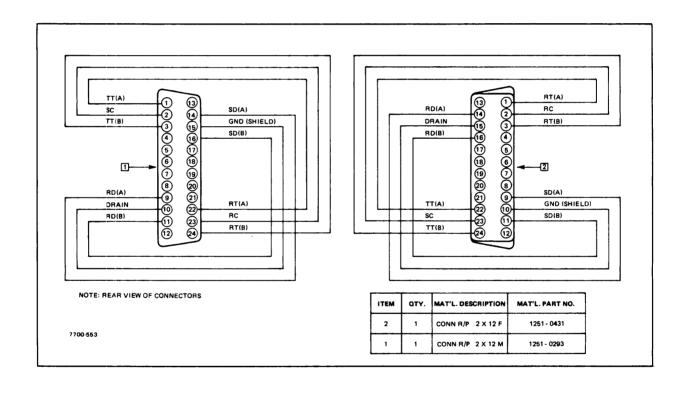

The communication line interface is the point at which the various signals used are received onto the card or driven onto the communications line. The signals sent from the card are Send Data (SD) and Transmit Timing (TT), and the signals received are Receive Data (RD) and Receive Timing (RT).

These signals are conveyed through the use of differential drivers and receivers (as per EIA RS-422) connected by four twisted-pair cables. (This connection is illustrated in Section 7.) A differential driver drives both the inverted and non-inverted signal to a differential receiver. The advantage of the differential drivers and receivers is that they offer higher noise immunity than single-ended drivers and receivers, thus allowing longer cable lengths and higher data signalling rates. The receivers on the card can survive an input voltage range of  $\pm$ 0 volts. The receivers on the card can operate with a maximum common mode input voltage of  $\pm$ 1 volts.

#### **Command and Status Words**

In addition to data words, command and status words are also exchanged between the host computer and the card. These additional words are transferred across the data bus and the data latches to aid in the process of communication between the host and the card.

Command words are initiated by the host driver and fall into the following four basic categories:

- Type 0 initiates a data transfer from a card buffer to a host computer buffer.

- Type 1 a single word command sent directly to the card firmware.

Examples include disconnect, abort current operation,

- Type 2 initiates a data transfer from a host computer buffer to a card buffer.

- Type 3 specifies that a multiple-word command is to follow.

Status words are generated by the card to inform the host of events that have occurred, are occurring or will be occurring on the card or communications line. Examples of these messages include transfer buffer ready, connect complete, error condition and message block size.

# **Functional-Level Description**

The description given in this section is of a typical operation of the card. The host computer assumed for this discussion is an HP 1000 M/E/F-Series Computer and the direct connection is made to an HP 1000 M/E/F/L-Series Computer, employing its own interface card.

#### **Power-Up**

Initially, the HP 1000 has been powered up and the communications line is not yet operational. At power-up, a reset signal is asserted that resets all the logic on the card, including the Z-80A components. The resetting of the Z-80A CPU invokes a ROM-resident self-test routine which makes its pass/fail message available to the host driver.

#### 4.4.2 Connect Sequence

The two ends of the communications line must be logically connected (physical connection is assumed at this point). must be logically connected. The primary sends a SARM frame (refer to Section 3 for a description of the HDLC protocol) and waits for a UA frame from the secondary. In our HP 1000 to HP 1000 configuration, each card sends a SARM frame and waits for a UA frame. When this handshake sequence is complete, a logical connection exists between the two computers.

### I/O Backplane Processing

The steps involved in a transfer from the host computer to the communications line (i.e., an output transfer) are as follows (the numbers in parentheses reference the various data paths and functional areas in Figure 4-1):

- 1. The host (software) driver issues a request for for output buffers (command type 1) onto the data latches (7) and then causes a Z-80A NMI (5). Because of the NMI, the firmware interprets the data in the latches as a command.

- 2. When a buffer becomes available, the host driver requests a transfer (command type 2) and enables the DCPC (Dual Channel Port Controller) hardware of the host.

- 3. The card writes zeros to the output latches (7). This starts the DCPC transfer from the host involving the backplane latches (7), control logic (13), data bus (6), DMA chip (4) and RAM (12).

- 4. The card interrupts the host (13) when the data transfer is complete.

- 5. The host may transfer additional blocks of data to the the card as buffer space becomes available. Steps 2 through 4 are repeated until the message is transferred from the host to the card in its entirety.

- 6. Each data block in the RAM buffer on the card is transferred via DMA (3) to the SIO (2) when the SIO chip becomes ready for the transfer. The SIO transmits the data as it is received. The CRC-16 block check characters (BCC) are sent as required.

Keep in mind that the CPU (5) is controlling all of the processing on the card by executing instructions that it fetches from ROM (10) and (11).

The steps involved in a transfer from the communications line to the host computer (i.e., an input transfer) are as follows:

- 1. The host driver enables inputs from the card by enabling a command word (command type 1) into the data latches (7).

- 2. The card firmware then sends a status word via the data latches (7) to the host driver informing it that an input buffer is available.

- 3. The host driver issues a request for input data command type 0) and enables the DCPC hardware of the host computer.

- 4. The card enables the first data word into the data latches (7) and asserts SRQ via the backplane logic (13).

- 5. The host driver begins the data transfer and the data block is transferred from the RAM (13) on the card to the host via a DMA chip (4), the data bus (6), the backplane latches (7) and the backplane handshake logic (13). Steps 2 through 5 are repeated until the entire message has been transferred.

- 6. The host is interrupted when the transfer is complete.

# **Disconnect Sequence**

The communications line is logically disconnected after each station sends a DISC frame and receives a UA frame. Either end of the DS link can initiate the disconnect sequence.

# Section 5 Maintenance

#### Introduction

This section provides maintenance information for the HP 12825A HDLC Direct Connect Interface Kit. Included are preventive maintenance instructions and troubleshooting information.

#### **Preventive Maintenance**

There is no preventive maintenance (PM) necessary for the HP 12825A other than a routine inspection of the equipment which can be performed at the same time that PM is done for the entire system. The card and cables should be checked for broken components, or the presence of foreign objects.

A self-test, residing in the firmware, is executed each time that power is applied to the card or the card is reset. In this manner, the interface card is checked automatically and only requires more thorough testing when specific failures occur.

### **Troubleshooting Techniques**

#### **CAUTION**

ALWAYS TURN POWER OFF TO THE COMPUTER AND OTHER ASSOCIATED EQUIPMENT WHEN INSERTING OR REMOVING INTERFACE CARDS OR CABLES. FAILURE TO DO SO COULD RESULT IN DAMAGE TO THE EQUIPMENT.

#### **CAUTION**

#### STATIC SENSITIVE DEVICES

THE ROMS, RAMS, AND Z-80A COMPONENTS USED IN THIS PRODUCT ARE SUSCEPTIBLE TO DAMAGE BY STATIC DISCHARGE. REFER TO THE SAFETY CONSIDERATIONS INFORMATION AT THE FRONT OF THIS MANUAL BEFORE REPLACING.

Once it has been determined that the hardware of the HP 1000-to-HP 1000 link is failing, proceed as follows to localize the failure to the specific component failing:

- 1. Run the following tests at both HP 1000s on the link:

- a. DSINF Card Configuration Check. (Follow the procedure outlined in the interface card configuration check paragraphs in Section 2 of this manual.)

- b. Firmware self-test.

- Loop-back verifier hood test.

- 2. If the above procedures are carried out successfully, it is reasonably certain that the interface cards and software/firmware at the HP 1000 nodes are operational. This implies that the failure is due to the cabling, or the line quality. To investigate the cabling, it is possible to run the self-test in a loop-back mode through the cables being used. This is accomplished by installing a test connector at some point in the cabling of the link. A wiring diagram is given in Section 7 of this manual for this test connector. To run the self-test in this mode, follow the same instructions

given in the loop-back verifier test paragraphs, installing the test connector instead of the loop-back hood. Other troubleshooting aids for investigating line quality and use are discussed in the last paragraphs of this section.

3. If a failure is found using one of the above test procedures, replace the failing card, firmware, or cables and repeat the test that failed to verify that the problem has been properly corrected. If the problem is still present with new equipment, refer to the last paragraph of this section for further troubleshooting procedures.

#### Firmware Self-Test

A self-test is available for the interface card included with the HP 12825A. The test examines CPU operation, on-board DMA operation (channels 0 and 1), counter/timer chip performance, RAM and ROM memory, and some parts of the receiver/driver circuits and controller. The test does not check the backplane circuitry on the card.

The self-test is located in the firmware ROMs on the interface card and is run at power up or whenever the card is reset (whenever a CLC 0 is sent to the card). Therefore it can be run by pressing the PRESET button on the front panel (such as during a re-boot), or by cycling the power on the computer. Note that these procedures require system and DS software reinitialization after running the test. It is recommended that the node is quiesced before running the self-test. This will allow all pending DS transactions to be completed and prevent new ones from starting. To quiesce the node, enter the commands RU,DSMOD<cr> and, after DS110D prompts for a command, enter /Q. description of DSMOD, refer to the Network Manager's Manual.) DSMOD prompts for the network security code which can be obtained from the network manager. The default security code is DS. Once the "NODE IS QUIESCENT" message appears on the screen, cycle power on the computer.

Self-test results are made available to the driver once the test is complete. To find out if the card passed the self-test, try executing the LU command after running DSINF as described in the interface card configuration check given in Section 2. The LEDs on the card will also indicate successful completion of the tests with all of them being turned off after the test is finished and before DS software has been initialized.

# **Loop-Back Verifier Hood Test**

Run the loop-back verifier hood test by proceeding as follows:

- a. Quiesce the node. This allows all pending transactions to be completed and prevents new ones from starting before running the test. Follow the same procedure used in the self-test procedure for quiescing the node. Remove power from the computer once the node is guiescent.

- b. Remove the cable fro the front edge connector and install the loop-back verifier hood, HP part number 5061-3421, in its place, orienting the connector the same as all other connectors in the card cage.

- c. Restore power to the system. When this occurs, the self-test is automatically executed on the card. The results of the test are returned to the software driver. Restore the operating system and check that the self-test completed successfully and that the hood was sensed by running DSINF and checking the information returned with the LU command.

- d. Once it has been established that the card has passed the self-test and that the hood has been sensed, a further check of the card can be accomplished by sending a message to the card and having it looped back on itself. This will out all message sending and thoroughly check receiving capabilities of the card and card/computer interaction capabilities. To configure the card to talk to itself, start by running DSMOD. command CN. DSMOD will prompt for the network security code which can be obtained from the network manager. After that has been entered, DSMOD will prompt for the node number to be changed. Enter the local node number. DSMOD will display the current routing vector for the local node which should specify LU 0. Then after the prompt for the new configuration, enter the LU # of the card that has the loop-back verifier hood installed on it. Now enter /E in response to the prompt for the next node number to be configured, and another /E to exit DSMOD. The card is now configured to talk to the local node.

- e. Run REMAT and execute some REMAT commands such as TI or DL. When this happens, the routing vector will specify that all commands to be executed at the local node should be sent out to the configured interface card. The card will transmit the data, it will be looped back through the hood, and the card will receive the data and send it back to the local CPU. If no errors are returned, this is a very good indication that the interface card and backplane circuitry are operational.

- f. Once the test is complete, run DSMOD and reconfigure the local node routing vector to again specify LU 0.

- g. To remove the loop-back verifier hood, remove power from the system and replace the hood with the cable.

- h. Restore power to the computer and reinitialize the system and DS software.

Since the loop-back verifier hood test checks more areas of the card (specifically the line drivers and receivers area of the interface, and the backplane interface circuitry), it is possible for the card to pass the self-test and fail the loop-back hood test. Therefore it is important that both the self-test and the loop-back verifier hood test are run.

### Other Troubleshooting Aids

If problems occur that cannot be identified using the hardware tests described above, there are other troubleshooting tools available. However, these tools require more familiarity with hardware operations, HDLC protocol, and characteristics of line use for the link being tested. Therefore, a review of the Theory of Operation and Protocol sections of this manual is recommended before proceeding. Detailed troubleshooting techniques are further discussed in the Distributed Systems Network Manager's Manual. Refer to that manual for information on DS utility programs available and their use as troubleshooting aids.

# Section 6 Replaceable Parts

#### Introduction

This section contains information for ordering replaceable parts for the HP 12044A HDLC Direct Connect Interface. Table 6-1 gives a list of replaceable parts, and Table 6-2 contains names and manufacturers of the parts.

# Replaceable Parts

Table 6-1 contains a list of replaceable parts in reference designation order. The following information is listed for each part:

- 1. Reference designation of the part.

- 2. The Hewlett-Packard part number.

- 3. Part number check digit (CD).

- 4. Total quantity (QTY).

- 5. Description of the part.

- 6. A five-digit manufacturer's code number of a typical manufacturer of the part.

- 7. The manufacturer's part number.

# **Ordering Information**

To order replacement parts or to obtain information on parts, address the order or inquiry to the local Hewlett-Packard Sales and Service Office (Sales and Service Offices are listd at the back of this manual).

To order a part listed in the replaceable parts table, quote the Hewlett-Packard part number (with the check digit), and indicate the quantity required. The check digit will insure accurate and timely processing of your order.

To order a part that is not listed in the replaceable parts table, specify the following information:

- 1. Identification of the kit containing the part (refer to Section 1 of this manual).

- 2. Description and function of the part.

- 3. Quantity required.

Table 6-1. Replaceable Parts

| Reference<br>Designation        | HP Part<br>Number                                                          | СЪ                         | Qty               | Description                                                                                                                                                                    | Mfr<br>Code                                        | Mfr Part Number                                                                |

|---------------------------------|----------------------------------------------------------------------------|----------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------|

|                                 | 5061-3432                                                                  | 3                          | 1                 | MX PROGRAM SER IF                                                                                                                                                              | 28480                                              | 5001-3432                                                                      |

| CRII                            | 1990-0662                                                                  | 0                          | 1                 | LED-VISIBLE LUM-INT#200UCD IF#5MA-MAX                                                                                                                                          | 28480                                              | 1990-0662                                                                      |

| 01<br>02<br>03                  | 1853-0015<br>1854-0019<br>1854-0467                                        | 7 3 5                      | 1<br>1<br>1       | TRANSISTOR PNP SI PD=200Mm FT=500Mm2<br>Transistor npn SI TD=18 PD=360Mm<br>Transistor npn 2N4401 SI TO=92 PD=310Mm                                                            | 28480<br>28480<br>03508                            | 1853-0015<br>1854-0019<br>2N4401                                               |

| 代中<br>円10<br>円11<br>尺13<br>尺14  | 1810-0276<br>1810-0279<br>1810-0279<br>1810-0279<br>1810-0279              | 2 5 5 5 5                  | 3<br>4            | NETWORK-RES 10-SIP1.5K DHM X 9 NETWORK-RES 10-SIP4.7K DHM X 9                     | 01121<br>01121<br>01121<br>01121<br>01121          | 210A152<br>210A472<br>210A472<br>210A472<br>210A472                            |

| R19<br>R31<br>R32               | 1810-0280<br>1810-0276<br>1810-0276                                        | 5 8                        | 1                 | NETHORK-RES 10-SIP10.0K OHM X 9<br>NETHORK-RES 10-SIP1.5K OHM X 9<br>NETHORK-RES 10-SIP1.5K OHM X 9                                                                            | 01121<br>01121<br>01121                            | 210A103<br>210A152<br>210A152                                                  |

| <b>\$</b> 1                     | 3101-1983                                                                  | 9                          | 1                 | SWITCH-DIP, 8-ROCKER                                                                                                                                                           | 28480                                              | 3101-1983                                                                      |

| T1                              | 9100-2643                                                                  | 4                          | 1                 | TRANSFORMER-DATA COMM                                                                                                                                                          | 28480                                              | 9100-2643                                                                      |

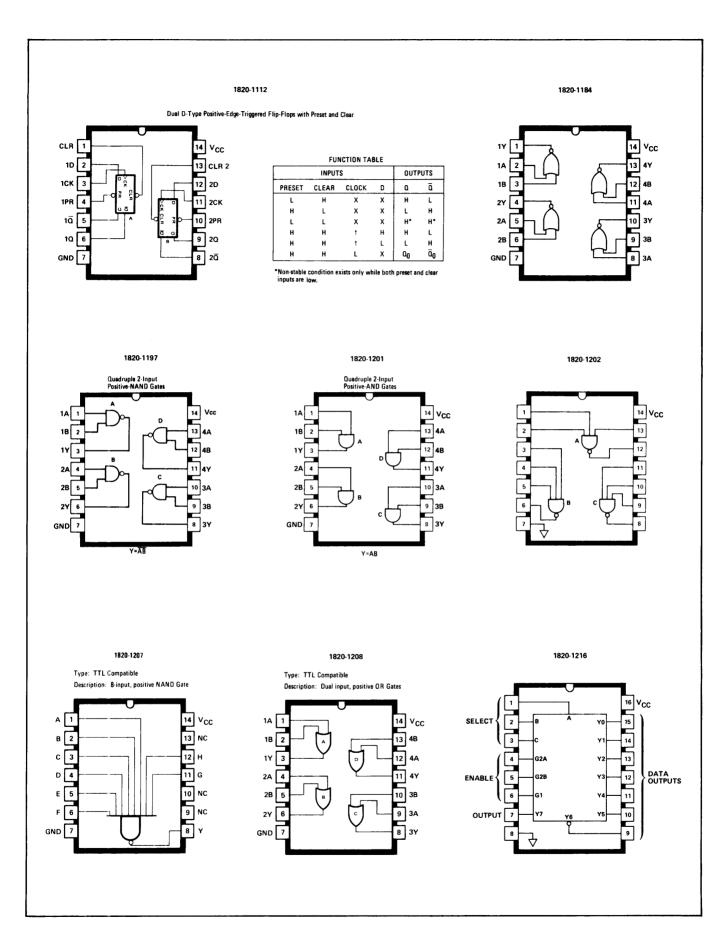

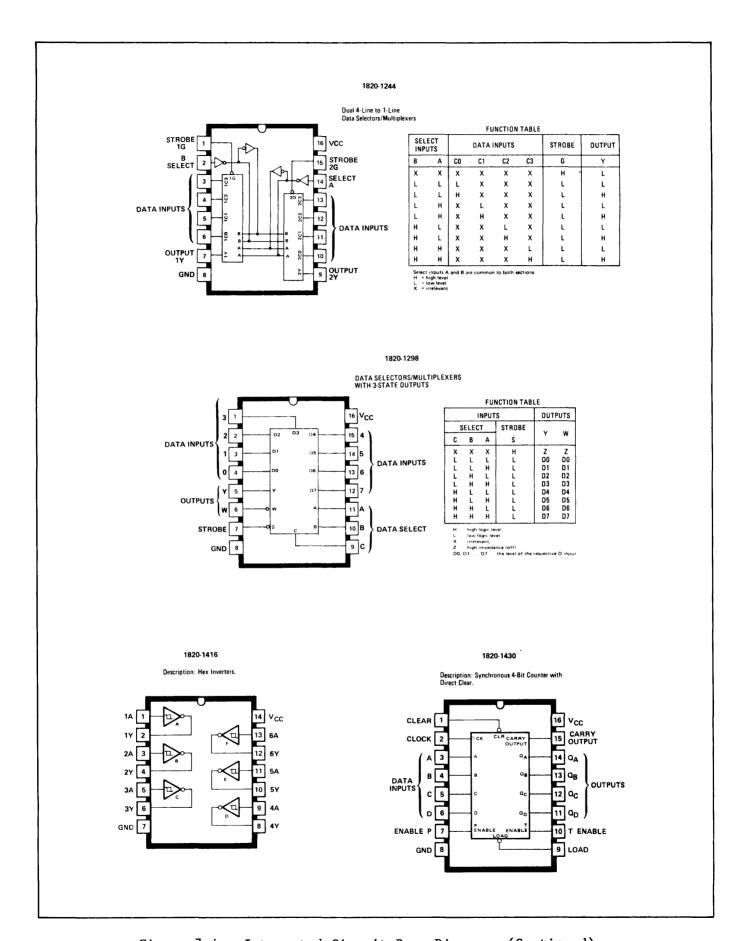

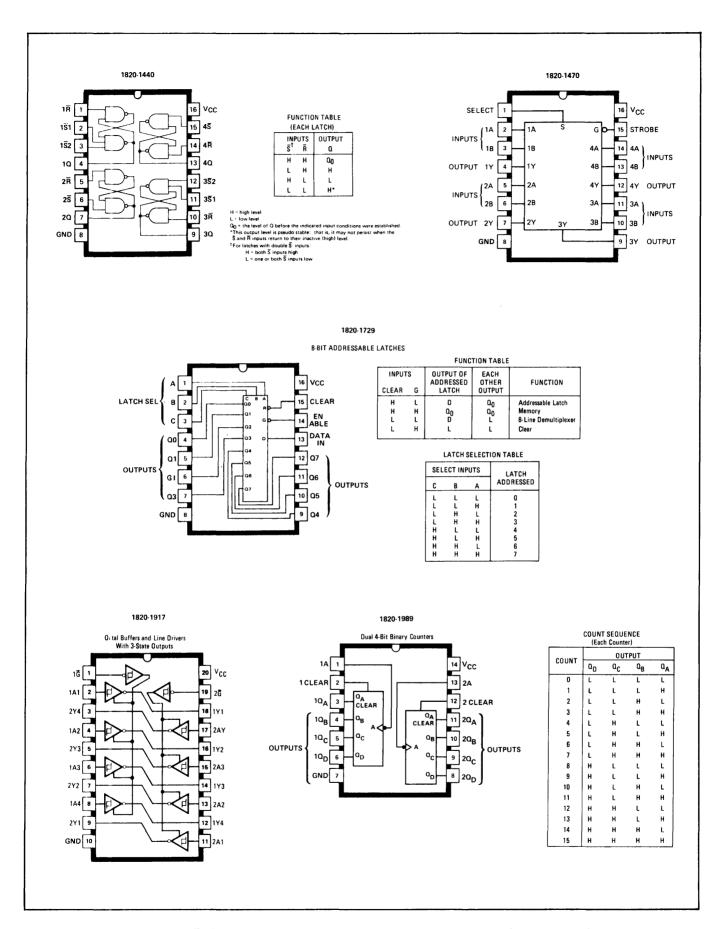

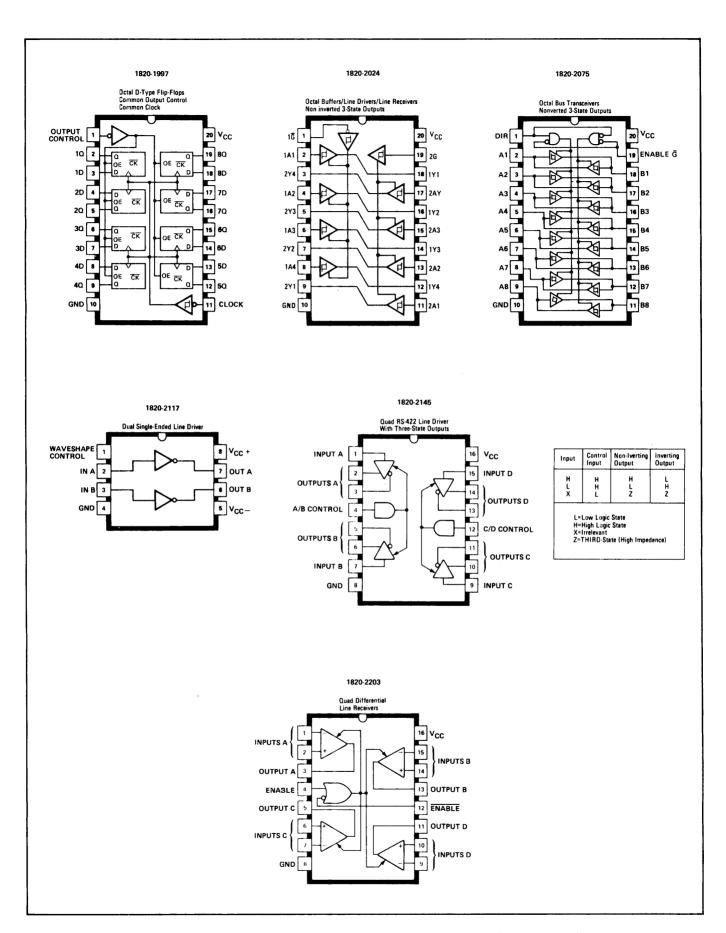

| U11<br>U13<br>U15<br>U16<br>U21 | 1820-2145<br>1820-1244<br>1820-1430<br>1820-1989<br>1820-1729              | 9<br>7<br>3<br>7<br>3      | 3<br>1<br>2<br>2  | IC DRVR TTL LINE DRVR QUAD IC MUXR/DATA-SEL TTL LS 4-TO-1-LINE DUAL IC CNTR TTL LS BIN SYNCHRO POS-EDGE-TRIG IC CNTR TTL LS BIN DUAL 4-BIT IC LCH TTL LS COM CLEAR 8-BIT       | 04713<br>01295<br>01295<br>07263<br>01295          | MC3487P<br>8N74L9153N<br>8N74L9161AN<br>74L389PC<br>8N74L8259N                 |

| U25<br>U25<br>U25               | 1820-2117<br>1820-1244<br>1820-1216<br>1813-0129<br>1200-0638              | 5<br>7<br>3<br>0<br>7      | 1<br>1<br>1       | IC DRVR TIL LINE DRVR DUAL IC MUXA/DATA-SEL TIL LS 4-TO-1-LINE DUAL IC DCDR TIL LS 3-TO-8-LINE 3-INP IC DSC HYBRID SOCKET-IC 14-CONT DIP DIP-SLOR                              | 07263<br>01295<br>01295<br>34344<br>28460          | 9636ATC<br>8n74L8153N<br>8n74L8138N<br>K1100A<br>1200-0638                     |

| U31<br>U32<br>U33<br>U34        | 1820-1298<br>1820-1729<br>1820-1244<br>1820-2203<br>1826-0220<br>1200-0185 | 1 3 7 0 9                  | 2 1 1             | IC MUXR/DATA-BEL TTL LS 8-TO-1-LINE IC LCH TTL LS COM CLEAR 8-BIT IC MUXR/DATA-BEL TTL LS 4-TO-1-LINE DUAL IC RCVR TTL LS LINE RCVR QUAD IC V RGLTR TO-39 INSULATOR-XSTR NYLON | 01295<br>01295<br>01295<br>34335<br>27014<br>28480 | 3N74L8251N<br>3N74L8259N<br>3N74L8153N<br>AM26L312PC<br>LM32OM-05<br>1200-0185 |

| U30<br>U37<br>U38<br>U42<br>U42 | 1820-1197<br>1820-1080<br>1820-0799<br>1820-1112<br>1820-2300<br>1200-0654 | 9<br>9<br>5<br>8<br>8<br>7 | 3<br>11<br>1<br>1 | IC GATE TIL LS NAND QUAD 2-INP IC DRVR TIL LINE DRVR DUAL 6-INP IC DRVR TIL NAND DUAL 2-INP IC FF TIL LS D-TYPE POS-EDGE-TRIG SOCKET-IC 40-CONT DIP DIP-SLOR                   | 01295<br>18324<br>01295<br>01295<br>28480<br>28480 | 8N74L800N<br>N8T13N<br>8N75452BP<br>8N74L3744N<br>1820-2300<br>1200-0654       |

| U45<br>U46<br>U47               | 1200-0567<br>1818-0341<br>1200-0607<br>1820-1201<br>1820-1080              | 1<br>8<br>0<br>6           | 3<br>6<br>6       | SOCKET-IC 28-CONT DIP DIP-SLDR<br>IC NMDS 16364-BIT RAM DYN 200-NS 3-8<br>SOCKET-IC 16-CONT DIP DIP-SLDR<br>IC GATE TIL LS AND QUAD 2-INP<br>IC DRVP TIL LINE DRVR DUAL 6-INP  | 28480<br>0003J<br>28480<br>01295<br>18324          | 1200-0567<br>UP04160-2<br>1200-0607<br>5N704506N<br>N8713N                     |

| U55                             | 1820-2298<br>1200-0654<br>1200-0567<br>1818-0341<br>1200-0607              | 3<br>7<br>1<br>8<br>0      | 1                 | SOCKET-IC 40-CONT DIP DIP-SLDR<br>SOCKET-IC 28-CONT DIP DIP-SLDR<br>IC NºOS 18384-BIT RAM DYN 200-NS 3-S<br>SOCKET-IC 16-CONT DIP DIP-SLDR                                     | 28480<br>28480<br>28480<br>0003J<br>28480          | 1620-2298<br>1200-0554<br>1200-0567<br>UPD416D-2<br>1200-0607                  |

| U56<br>U57<br>U62<br>U63        | 1820-1440<br>1820-1197<br>1820-2299<br>1200-0654<br>1820-1208              | 5<br>9<br>4<br>7<br>3      | 1<br>2<br>2       | IC LCH TTL LS GUAD IC GATE TTL LS NAND GUAD 2-INP SOCKET-IC 40-CONT DIP DIP-SLDR IC GATE TTL LS OR GUAD 2-INP                                                                  | 01295<br>01295<br>28480<br>28480<br>01295          | 8n74L8279n<br>8n74L900n<br>1820-2299<br>1200-0654<br>8n74L832n                 |

| U65<br>U65                      | 1820-0693<br>1818-0341<br>1200-0607<br>1820-1416                           | 8 8 0 5                    | 2                 | IC FF TTL S D-TYPE POS-EDGE-TRIG IC NMOS 16364-BIT RAM DYN 200-NS 3-S SOCKET-IC 16-CONT DIP DIP-SLDR IC SCMMITT-TRIG TTL LS INV MEX 1-INP                                      | 01295<br>0003J<br>28480<br>01295                   | 3N74874N<br>UPD4160-2<br>1200-0607<br>3N74L314N                                |

| U67                             | 1820-1080                                                                  | 9                          |                   | IC DRYR TTL LINE DRYR DUAL 6-INP                                                                                                                                               | 18324                                              | N8713N                                                                         |

| U73<br>U75                      | 1820-0693<br>1818-0341<br>1200-0607<br>1820-1202                           | 8 0 7                      | 1                 | IC FF TTL S D-TYPE POS-EDGE-TRIG IC NMOS 16384-BIT RAM DYN 200-NS 3-8 SOCKET-IC 16-CONT DIP DIP-SLOR IC GATE TTL LS NAND TPL 3-INP                                             | 01295<br>0003J<br>28480<br>01295                   | SN74874N<br>UPD416D-2<br>1200-0807<br>SN74L310N                                |

| U77                             | 1820-1080                                                                  | 9                          | 1                 | IC DRVR TTL LINE DRVR DUAL 6-INP                                                                                                                                               | 18324                                              | N8713N                                                                         |

| U83<br>U84<br>U85               | 1820-2299<br>1200-0654<br>1820-083<br>5090-0599<br>1818-0341<br>1200-0607  | 4<br>7<br>6<br>8<br>8      | 1 1               | SOCKET-IC 40-CONT DIP DIP-SLDR<br>IC INV TTL 8 MEX 1-INP<br>IC-ROM<br>IC NMOS 16384-BIT RAM DYN 200-NS 3-S<br>SOCKET-IC 16-CONT DIP DIP-SLDR                                   | 28480<br>28480<br>01295<br>28480<br>0003J<br>28480 | 1820-2299<br>1200-0654<br>8N74806N<br>5090-0599<br>UPD4160-2<br>1200-0607      |

| U86<br>U87<br>U92               | 1820-1201<br>1820-1080<br>1820-2301<br>1200-0567                           | 9                          | 1                 | IC GATE TTL LS AND QUAD 2-INP IC DRVR TTL LINE DRVR DUAL 6-INP SOCKET-IC 28-CONT DIP DIP-SLDR                                                                                  | 01295<br>18324<br>28480<br>28480                   | 8N74L508N<br>N8T13N<br>1820=2301<br>1200=0567                                  |

| U93                             | 5090-1614                                                                  | 0                          | 1                 | 10-6309-1                                                                                                                                                                      | 28480                                              | 5090-1614                                                                      |

Table 6-1. Replaceable Parts (Continued)

| Reference<br>Designation             | HP Part<br>Number                                             | C<br>D                | Qty         | Description                                                                                                                                                                            | Mfr<br>Code                               | Mfr Part Number                                                |

|--------------------------------------|---------------------------------------------------------------|-----------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------|

| U95<br>U96<br>U97                    | 1200-0483<br>1818-0341<br>1200-0607<br>1820-1197<br>1820-1080 | 0 0 0 0 0             | 1           | SOCKET-IC 14-CONT DIP-SLOR IC NMOS 16384-BIT RAM-DYN 200-NS 3-S SOCKET-IC 16-CONT DIP DIP-SLOR IC GATE TTL LS NAND GUAD 2-INP IC DRYR TTL LINE DRYR DUAL 6-INP                         | 28480<br>0003J<br>28480<br>01295<br>18324 | 1200-0483<br>UPD41aD=2<br>1200-0607<br>8n74L800N<br>N8T13N     |

| U101<br>U103<br>U105<br>U106         | 1820=2024<br>1820=1207<br>1818=0341<br>1200=0607<br>1820=1184 | 3 2 8 0 4             | 1<br>1      | IC DRVR TIL L8 LINE DRVR OCTL IC GATE TIL L8 NAND 8-INP IC NMOS 16384-BIT RAM DYN 200-NS 3-8 SOCKET-IC 16-CONT DIP DIP-SLDR IC 8FR TIL NOR QUAD 2-INP                                  | 01295<br>01295<br>0003J<br>28480<br>01295 | 8N74L8244N<br>8N74L830N<br>UPD418D=2<br>1200-0807<br>8N7428N   |

| U107<br>U203<br>U205<br>U206         | 1820-1080<br>1820-1208<br>1818-0341<br>1200-0607<br>1820-1997 | 9<br>3<br>8<br>0<br>7 | 4           | IC DRVR TIL LINE DRVR DUAL 6=INP IC GATE TIL LS OR QUAD 2=INP IC NMOS 16384-81T RAP DYN 200-NS 3=8 SOCKET=IC 16-CONT DIP DIP=8LDR IC FF TIL LS O-TYPE POS-EDGE-TRIG PRL-IN             | 18324<br>01295<br>0003J<br>28480<br>01295 | N8T13N<br>8N74L532N<br>UPD418D=2<br>1200-0607<br>8N74L8374N    |

| U207<br>U302<br>U303<br>U304<br>U306 | 1820-1080<br>1990-0461<br>1820-1470<br>1820-2075<br>1820-1997 | 9<br>7<br>1<br>4<br>7 | 1<br>2<br>1 | IC DRVR TTL LINE DRVR DUAL 6-INP OPTO-ISOLATOR LED-IC GATE IF-10MA-MAX IC MUXP/DATA-SEL TTL LS 2-TO-1-LINE GUAD IC MISC TTL LS IC MISC TTL LS IC FF TTL LS D-TYPE POS-EDGE-TRIG PRL-IN | 18324<br>28480<br>01295<br>01295<br>01295 | N8T13N<br>5082-4364<br>8N74L8157N<br>8N74L8248N<br>8N74L8374N  |

| U307<br>U401<br>U403<br>U404<br>U406 | 1A20-1080<br>1820-2203<br>1820-1470<br>1820-1917<br>1820-1997 | 9<br>0<br>1<br>1<br>7 | 1           | IC DRVR TIL LINE DRVR DUAL 6-INP IC RCVR TIL L8 LINE RCVR QUAD IC MUXR/DATA-8EL TIL LS 2-T0-1-LINE QUAD IC BPR TIL LS LINE DRVR DCTL IC FF TIL LS D-TYPE POS-EDGE-TRIG PRL-IN          | 18324<br>34335<br>01295<br>01295<br>01295 | N8T13N<br>AM26L832PC<br>8N74L8157N<br>8N74L8240N<br>8N74L8374N |

| U407<br>U503<br>U506<br>U507         | 1820-1080<br>1820-1989<br>1820-1997<br>1820-1080              | 9<br>7<br>7<br>9      |             | IC DRVR TTL LINE DRVR DUAL 6-INP IC CNTR TTL LS BIN DUAL 4-BIT IC FF TTL LS D-TYPE POS-EGGE-TRIG PRL-IN IC DRVR TTL LINE DRVR DUAL 6-INP                                               | 16324<br>07263<br>01295<br>16324          | NST13N<br>74L3393PC<br>8N74L3374N<br>NST13N                    |

|                                      | 1200-0455                                                     | 6                     | i           | SOCKET-IC 8-CONT DIP-SLDR MISCELLANEOUS PARTS                                                                                                                                          | 28480                                     | 1200-0455                                                      |

|                                      | 1480-0116<br>5061-3433                                        | 8 4                   | 1 1         | PIN-GRV 062-IN-DIA .25-IN-LG STL<br>AXIAL INSERTION                                                                                                                                    | 28480<br>28480                            | 1480-0116<br>5061-3433                                         |

|                                      |                                                               |                       |             |                                                                                                                                                                                        |                                           |                                                                |