# Enterprise Server Group Intel SC450NX MP Server System Technical Product Specification

Released version 2.0 Order Number 243785-002 January 1999

intel

The S450NX MP Server baseboard may contain design defects or errors known as errata. Characterized errata that may cause the S450NX MP Server baseboard's behavior to deviate from published specifications are documented in the S450NX MP Server Specification Update.

# **Revision History**

| Revision | Revision History                                                                                                                                                                                                              | Date |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Rev 1.0  | Initial Release                                                                                                                                                                                                               | 7/98 |

| Rev 2.0  | Added POST codes, POST error codes and messages, Server Management POST codes, cable information, RTC accuracy section, MTBF numbers, errata, updated validation summary information, moved Cabrillo information in this TPS. | 1/99 |

**NOTE**: If printing this document from an electronic file, use a PostScript printer with the appropriate PostScript print driver to ensure the drawings print clearly.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

The Intel products referred to in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

The S450NX MP Server baseboard is Year 2000 capable. For more information with regard to the Year 2000 issue, please refer to the Intel web site at http://support.intel.com/sites/support/index.htm.

Copyright © Intel Corporation 1999. \*Third-party brands and names are the property of their respective owners.

# **Table of Contents**

| 1. | Boar | d Set Des   | criptions                                  | 6   |

|----|------|-------------|--------------------------------------------|-----|

|    | 1.1  | Baseboard   | Overview                                   | 6   |

|    |      | 1.1.1       | Baseboard Diagram                          | 7   |

|    | 1.2  | Processor/  | PCI Host Bridge                            | 8   |

|    | 1.3  | Pentium II  | ী Xeon™ Processor Cartridge                | 9   |

|    |      | 1.3.1       | Retention Module                           | 9   |

|    |      | 1.3.2       | Processor Cartridge Connector              | 9   |

|    |      | 1.3.3       | Processor Heat/Fan Sinks                   | 9   |

|    |      | 1.3.4       | Processor Bus Termination/Regulation/Power | 9   |

|    |      | 1.3.5       | Termination Card                           | 9   |

|    |      | 1.3.6       | APIC Bus                                   | 9   |

|    | 1.4  | 82450NX F   | PCIset                                     | .10 |

|    |      | 1.4.1       | 82450NX System I/O Access                  | .10 |

|    |      | 1.4.2       | 82450NX Main Memory Access                 | .10 |

|    | 1.5  | PCI-A I/O S | Sub-system                                 | .11 |

|    |      | 1.5.1       | PCI-A Arbitration                          | .11 |

|    |      | 1.5.2       | PCI-to-ISA/IDE/USB Controller PIIX4(e)     | .12 |

|    | 1.6  | PCI-A Narr  | ow SCSI                                    | .12 |

|    |      | 1.6.1       | SYM53C810AE PCI Signals                    | .12 |

|    | 1.7  | PCI-A Vide  | 0                                          | .13 |

|    |      | 1.7.1       | Video Component PCI Signals                | .13 |

|    |      | 1.7.2       | Video Controller PCI Commands              | .14 |

|    |      | 1.7.3       | Video Modes                                | 14  |

|    |      | 1.7.4       | VGA connector                              | .17 |

|    | 1.8  | PCI-B I/O S | Sub-system                                 | 18  |

|    |      | 1.8.1       | PCI-B Arbitration                          | .18 |

|    | 1.9  | PCI-B Wide  | e SCSI                                     | .18 |

|    |      | 1.9.1       | SYM53C896 PCI Signals                      | .19 |

|    |      | 1.9.2       | SCSI Interface                             | .19 |

|    | 1.10 | ISA I/O Su  | b-system                                   | .20 |

|    |      | 1.10.1      | I/O Controller Sub-system                  | .20 |

|    |      | 1.10.2      | Serial Ports                               | .21 |

|    |      | 1.10.3      | Parallel Port                              | .21 |

|    |      | 1.10.4      | Floppy Disk Controller                     | .21 |

|    |      | 1.10.5      | Keyboard and Mouse Connectors              | .22 |

|    | 1.11 | System Re   | set Control                                | .23 |

|    |      | 1.11.1      | Power-up Reset                             | .23 |

|    |      | 1.11.2       | Hard Reset                                                 | 23 |

|----|------|--------------|------------------------------------------------------------|----|

|    |      | 1.11.3       | Soft Reset                                                 | 23 |

|    |      | 1.11.4       | Reset Diagram                                              | 24 |

|    | 1.12 | Clock Gene   | eration and Distribution                                   | 24 |

|    |      | 1.12.1       | Real Time Clock, CMOS SRAM, and Battery                    | 25 |

|    | 1.13 | Interrupts a | ind the PID                                                | 25 |

|    |      | 1.13.1       | PIIX4(e) Compatibility Interrupt Controller                | 25 |

|    |      | 1.13.2       | Intel PID                                                  | 25 |

|    |      | 1.13.3       | Interrupt Routing                                          | 26 |

|    |      | 1.13.4       | Interrupt Sources                                          | 26 |

|    | 1.14 | System Boa   | ard Jumpers                                                | 27 |

|    | 1.15 | RAID Confi   | guration                                                   | 28 |

| 2. | Serv | er Manage    | ment                                                       | 29 |

|    | 2.1  | -            | /anagement Bus                                             |    |

|    | 2.2  | •            | Management Controller (BMC)                                |    |

|    | 2.3  |              | I Connector                                                |    |

|    |      | 2.3.1        | Baseboard / Front Panel Interface                          | 30 |

|    |      | 2.3.2        | Hot Swap Backplane / Front Panel Interface                 | 31 |

|    |      | 2.3.3        | Chassis Intrusion Switch Connector / Front Panel Interface | 31 |

|    |      | 2.3.4        | Fan Power Connector / Front Panel Interface                | 31 |

|    |      | 2.3.5        | Fan Connector /Front Panel Interface                       | 31 |

|    | 2.4  | Fault Resili | ent Booting                                                | 32 |

|    | 2.5  | Auxiliary IP | MB Connector                                               | 32 |

|    | 2.6  | ICMB Conr    | nector                                                     | 32 |

|    | 2.7  | Server Mon   | itor Module Connector                                      | 33 |

|    | 2.8  | System Far   | n Interface                                                | 33 |

| 3. | Mem  | ory and Ot   | ther Resource Mappings                                     | 34 |

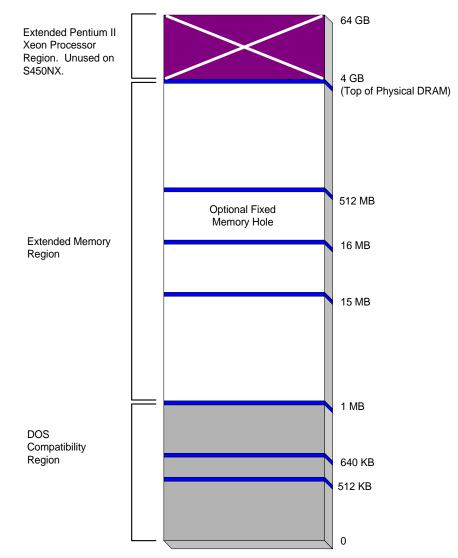

|    | 3.1  | Memory Sp    | pace                                                       | 35 |

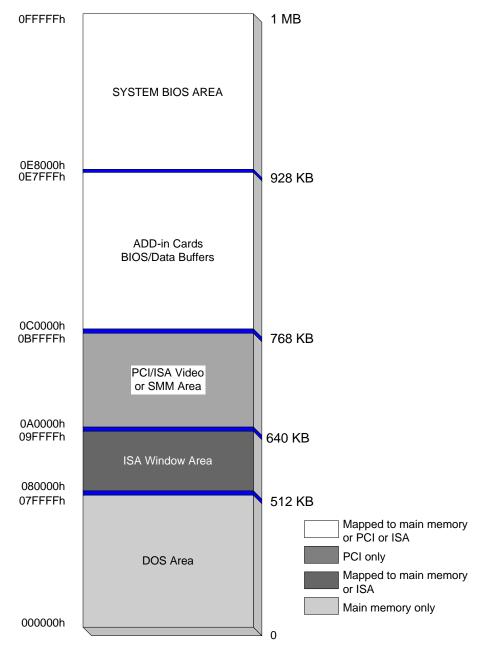

|    |      | 3.1.1        | DOS Compatibility Region                                   | 36 |

|    |      | 3.1.2        | DOS Area                                                   | 37 |

|    |      | 3.1.3        | ISA Window Memory                                          | 37 |

|    |      | 3.1.4        | Video or SMM Memory                                        | 37 |

|    |      | 3.1.5        | Add-in Card BIOS and Buffer Area                           | 37 |

|    |      | 3.1.6        | System BIOS                                                | 37 |

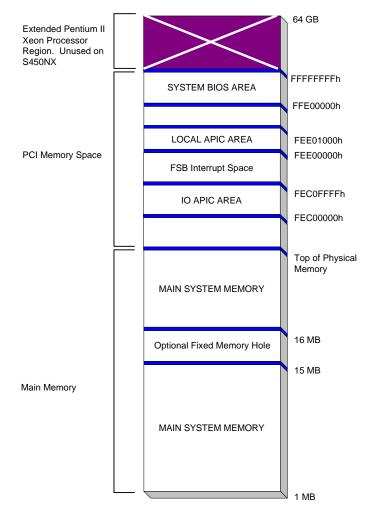

|    |      | 3.1.7        | Extended Memory                                            | 37 |

|    |      | 3.1.8        | Main Memory                                                | 38 |

|    |      | 3.1.9        | PCI Memory Space                                           | 38 |

|    |      | 3.1.10       | High BIOS                                                  | 39 |

|    |      |              |                                                            |    |

|    |      | 3.1.11     | Local APIC Space                                         |    |

|----|------|------------|----------------------------------------------------------|----|

|    |      | 3.1.12     | FSB Interrupt Space                                      |    |

|    |      | 3.1.13     | I/O APIC Configuration Space                             |    |

|    |      | 3.1.14     | Extended Pentium II Xeon Slot 2 Region (above 4GB)       |    |

|    |      | 3.1.15     | Memory Shadowing                                         |    |

|    |      | 3.1.16     | SMM Mode Handling                                        | 40 |

|    | 3.2  | I/O Map .  |                                                          | 40 |

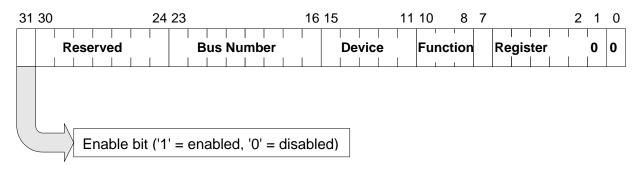

|    | 3.3  | Accessing  | g Configuration Space                                    | 41 |

|    |      | 3.3.1      | CONFIG_ADDRESS Register                                  | 41 |

|    |      | 3.3.2      | Device Number and IDSEL Mapping                          | 42 |

|    | 3.4  | Error Har  | ndling                                                   | 42 |

|    | 3.5  | Hardware   | e Initialization and Configuration                       | 43 |

|    |      | 3.5.1      | System Initialization Sequence                           | 43 |

|    | 3.6  | Server M   | anagement Programming Interface                          | 43 |

|    | 3.7  | PCI Interr | rupt to IRQ Routing Control                              | 43 |

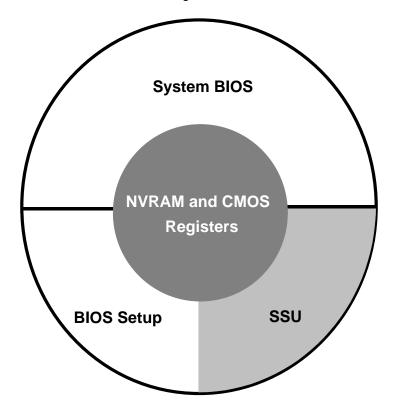

| 4. | BIOS | S. Setup a | and SSU                                                  | 44 |

|    | 4.1  | -          | erview                                                   |    |

|    | 4.2  |            | 3105                                                     |    |

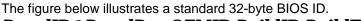

|    | 4.3  |            | History Format                                           |    |

|    | 4.4  |            | odes                                                     |    |

|    | 4.5  |            | ror Codes and Messages                                   |    |

|    | 4.6  |            | al Diagnostic Beep Codes                                 |    |

| _  |      |            |                                                          |    |

| 5. |      | -          | ecifications                                             |    |

|    | 5.1  |            | Maximum Ratings                                          |    |

|    | 5.2  |            | Specifications                                           |    |

|    |      | 5.2.1      | Power Connection                                         |    |

|    |      | 5.2.2      | Power Consumption                                        |    |

|    |      | 5.2.3      | Power Supply Specifications                              |    |

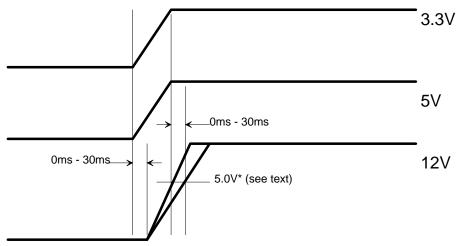

|    |      | 5.2.4      | Voltage Recovery Timing Specifications                   |    |

|    |      | 5.2.5      | Voltage Sequencing and Power Good Signal Characteristics |    |

|    |      | 5.2.6      | Ripple Voltage                                           |    |

|    | 5.3  |            | cal Specifications                                       |    |

|    |      | 5.3.1      | Connector Specifications                                 |    |

|    |      | 5.3.2      | PCI and ISA Connectors                                   |    |

|    | 5.4  |            | ne between Failures (MTBF) Data                          |    |

|    |      | 5.4.1      | S450NX MP Server Baseboard MTBF                          |    |

|    |      | 5.4.2      | SC450NX MP Server System MTBF                            | 60 |

| 6. | Pow  | er Share   | Backplane                                                | 61 |

|    | 6.1 | Features  | S                                             | 61 |

|----|-----|-----------|-----------------------------------------------|----|

|    | 6.2 | Electrica | al Connections                                | 61 |

|    |     | 6.2.1     | Power Supply                                  | 62 |

|    |     | 6.2.2     | Baseboard Power                               | 62 |

|    |     | 6.2.3     | Baseboard Auxiliary                           | 63 |

|    |     | 6.2.4     | Peripherals                                   | 63 |

|    | 6.3 | Power S   | Supplies and Sharing Circuits                 | 63 |

|    | 6.4 | Clusterin | ng Support                                    | 63 |

|    |     | 6.4.1     | 3.3V Power Form                               | 64 |

|    |     | 6.4.2     | VCC_STDBY Power Form                          | 64 |

|    |     | 6.4.3     | 5V Power Form                                 | 64 |

|    |     | 6.4.4     | 12V Power Form                                | 64 |

|    |     | 6.4.5     | -12V Power Form                               | 64 |

|    |     | 6.4.6     | Micro-controller                              | 64 |

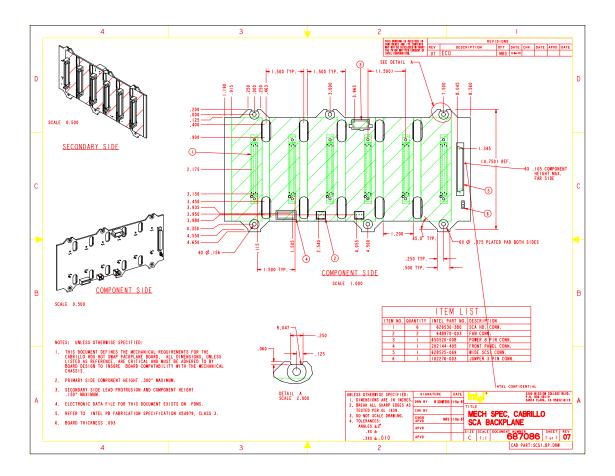

| 7. | LVC | )/SE SCSI | I Backplane                                   | 65 |

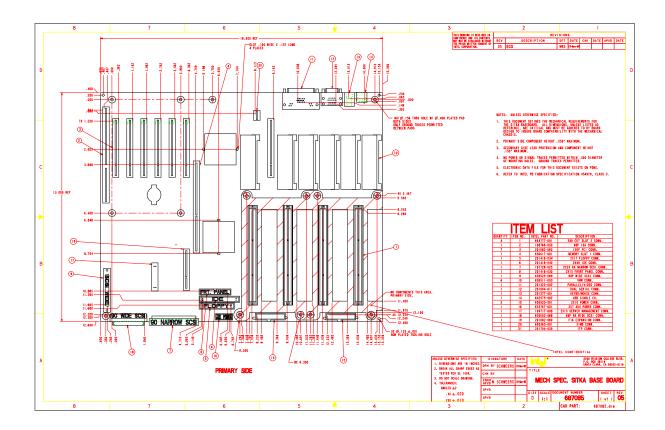

|    | 7.1 | Overview  | w                                             | 65 |

|    | 7.2 | Function  | nal Description                               | 65 |

|    |     | 7.2.2     | SCA-2 Connectors                              | 65 |

|    |     | 7.2.3     | SCSI Multi-Mode Termination                   | 66 |

|    |     | 7.2.4     | SCSI Interface                                | 66 |

|    |     | 7.2.5     | Power Control                                 | 66 |

|    |     | 7.2.6     | FET short protection                          | 66 |

|    |     | 7.2.7     | Microcontroller                               | 66 |

|    |     | 7.2.8     | Hard Drive Fault LED                          | 66 |

|    |     | 7.2.9     | IPMB (IPMB bus)                               | 66 |

|    |     | 7.2.10    | Fan                                           | 67 |

|    |     | 7.2.11    | Serial EEPROM                                 | 67 |

|    | 7.3 | Board Fu  | unctions                                      | 67 |

|    |     | 7.3.1     | Microcontroller                               | 67 |

|    |     | 7.3.2     | SCSI Controller                               | 67 |

|    |     | 7.3.3     | Multi-Mode SCSI Termination                   | 67 |

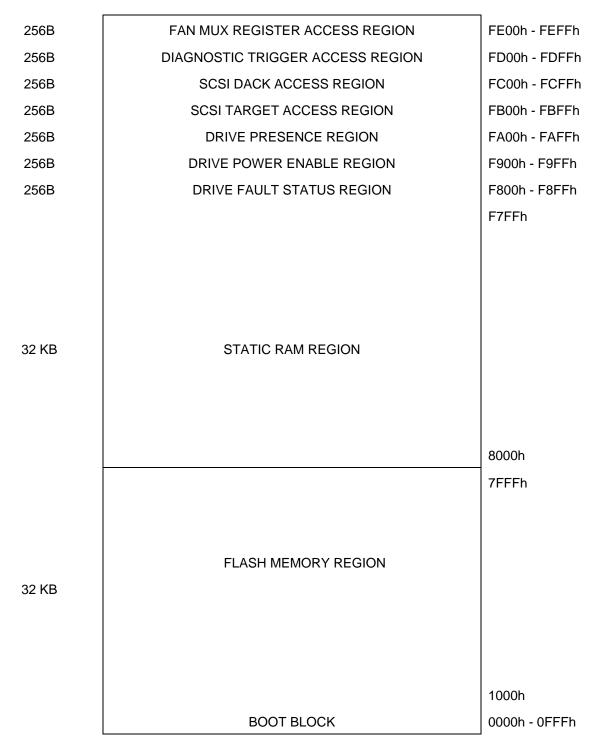

|    | 7.4 | Memory    | Мар                                           | 67 |

|    |     | 7.4.1     | Flash Memory Region (0x0000 - 0x7FFF)         | 69 |

|    |     | 7.4.2     | Static RAM Region (0x8000 - 0xF7FF)           | 69 |

|    |     | 7.4.3     | Memory Mapped Registers (0xF800 - 0xFFFF)     | 69 |

|    |     | 7.4.4     | Drive Fault Status Region (0xF800 - 0xF8FF)   | 69 |

|    |     | 7.4.5     | Drive Power Enable Region (0xF900 - 0xF9FF)   | 69 |

|    |     | 7.4.6     | Drive Present Status Region (0xFA00 - 0xFAFF) | 69 |

|    |     | 7.4.7     | SCSI Target Access Region (0xFB00 - 0xFBFF)   | 70 |

|     |         | 7.4.8        | SCSI DACK Access Region (0xFC00 - 0xFCFF)          | 70 |

|-----|---------|--------------|----------------------------------------------------|----|

|     |         | 7.4.9        | Diagnostic Trigger Access Region (0xFD00 - 0xFDFF) | 70 |

|     |         | 7.4.10       | Fan Mux Register Access Region (0xFE00 - 0xFEFF)   | 70 |

|     | 7.5     | I/O Ports    |                                                    | 70 |

|     |         | 7.5.1        | P0                                                 | 70 |

|     |         | 7.5.2        | P1                                                 | 71 |

|     |         | 7.5.3        | P2                                                 | 71 |

|     |         | 7.5.4        | P3                                                 | 71 |

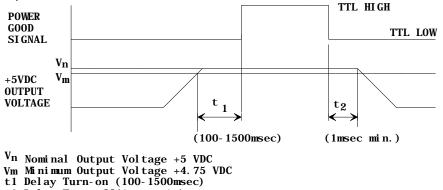

|     | 7.6     | Mechanica    | I Specifications                                   | 72 |

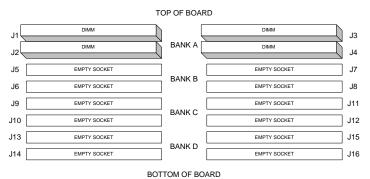

| 8.  | Mem     | ory Modul    | e                                                  | 73 |

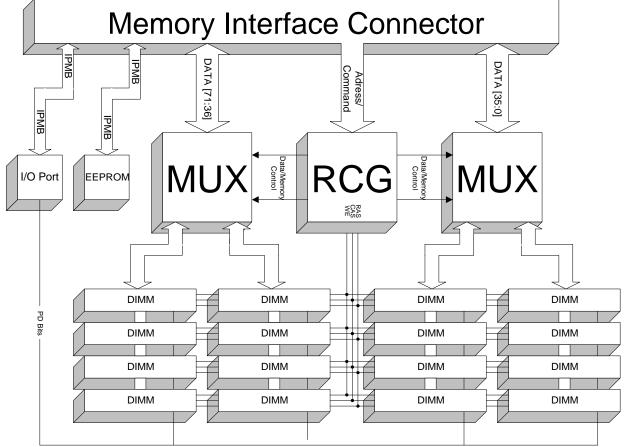

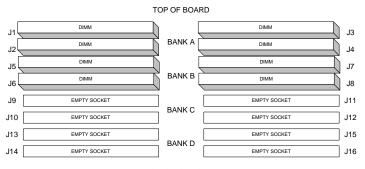

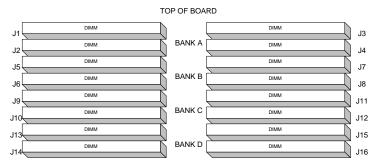

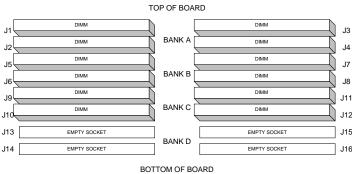

|     | 8.1     | Block Diag   | ram                                                | 73 |

|     | 8.2     | Overview     |                                                    | 74 |

|     | 8.3     | EDO DRAN     | VI Array                                           | 74 |

|     | 8.4     | The Intel 82 | 2450NX PCIset                                      |    |

|     |         | 8.4.1        | MUX                                                |    |

|     |         | 8.4.2        | RCG                                                |    |

|     |         | 8.4.3        | System Management Interface                        | 77 |

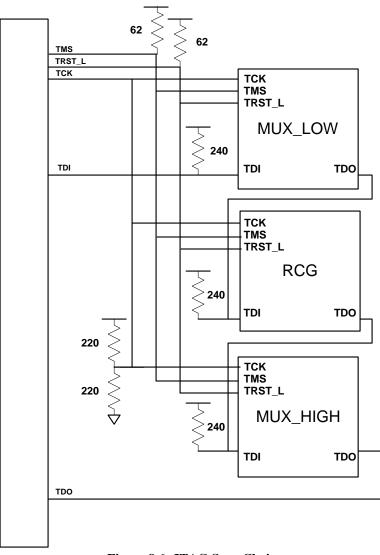

|     |         | 8.4.4        | JTAG Scan                                          | 79 |

|     | 8.5     | Signal Des   | criptions                                          | 80 |

|     |         | 8.5.1        | Memory Interface Bus Signals                       | 80 |

|     |         | 8.5.2        | DRAM Interface Signals                             | 82 |

|     |         | 8.5.3        | Other Signals                                      | 83 |

|     | 8.6     | Mechanical   | I Specifications                                   | 83 |

| 9.  | Cabr    | illo Chassi  | is Overview                                        | 85 |

|     | 9.1 Int | roduction    |                                                    | 85 |

|     | 9.2 Pr  | oduct Descri | iption                                             | 85 |

|     |         | 9.2.1        | Front Bezel                                        | 85 |

|     |         | 9.2.2        | Security                                           | 85 |

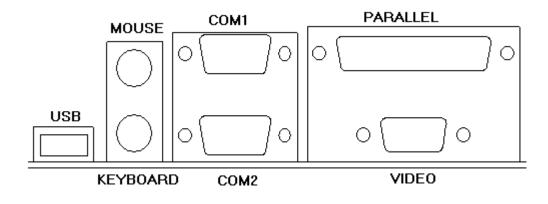

|     |         | 9.2.3        | I/O panel                                          | 86 |

| 10. | Syste   | em Configu   | uration                                            |    |

|     | 10.1    | -            | wer                                                |    |

|     |         | 10.1.1       | Fan Requirements                                   |    |

|     |         | 10.1.2       | AC Power Line                                      |    |

|     |         | 10.1.3       | Power Distribution Boards                          | 89 |

|     |         | 10.1.4       | System with Power Share Configuration              |    |

|     | 10.2    | System Co    | ooling                                             |    |

|     | 10.3    | System Pe    | ripheral Bays                                      |    |

|     |         | 10.3.1       | 3.5" Floppy Drive Bay                              |    |

|      |        | 10.3.2         | 5.25" Peripheral Bays                                       | 90  |

|------|--------|----------------|-------------------------------------------------------------|-----|

|      |        | 10.3.3         | Internal 3.5" Hard Drive Bays with SCSI Hot Swap Back plane | 90  |

|      | 10.4   | Standard       | Configurations                                              | 91  |

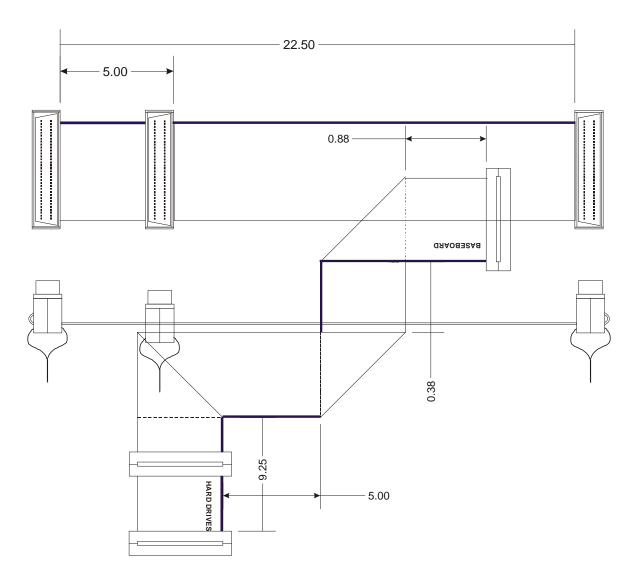

|      | 10.5   | System In      | terconnection                                               | 92  |

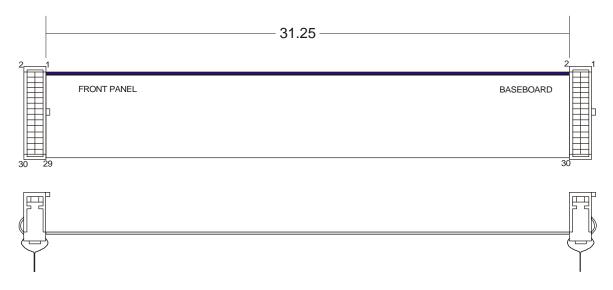

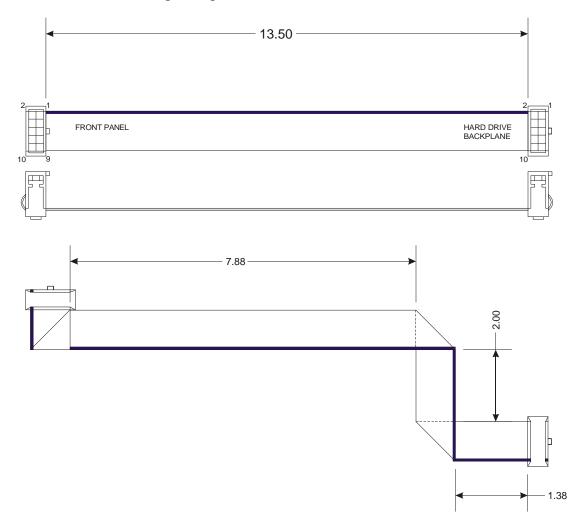

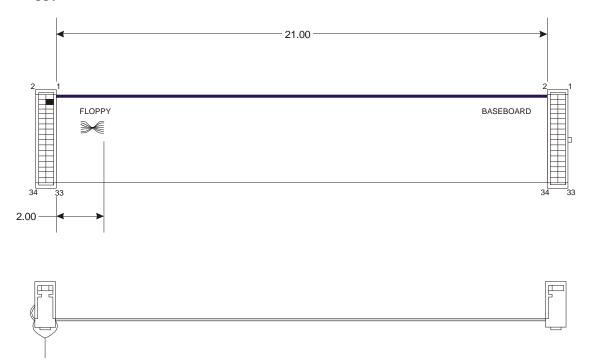

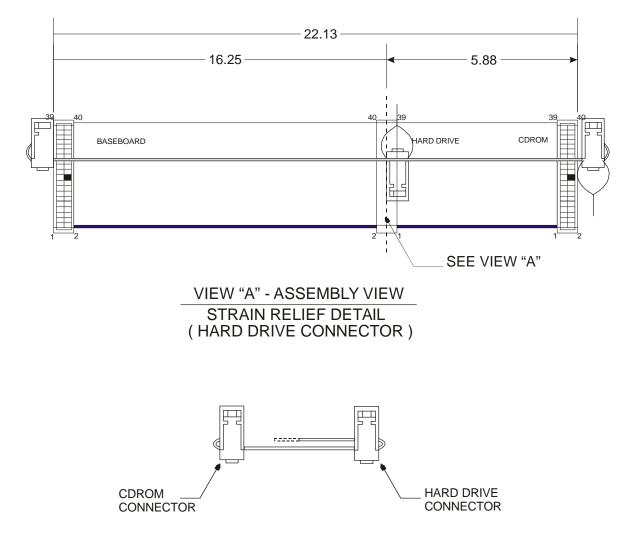

|      |        | 10.5.1         | Cable Definitions                                           | 92  |

|      |        | 10.5.2         | System Internal Cables                                      | 92  |

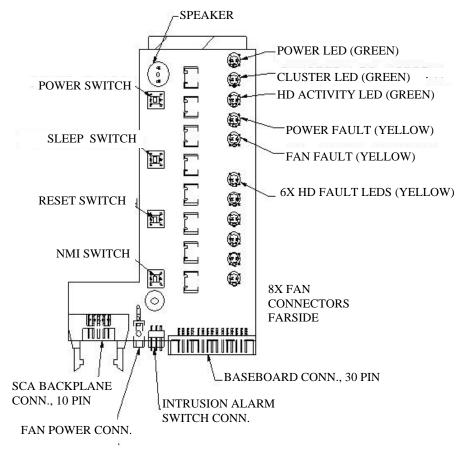

|      | 10.6   | Front Pan      | iel                                                         | 92  |

|      |        | 10.6.1         | Baseboard / Front Panel Interface                           | 95  |

|      |        | 10.6.2         | Hot Swap Backplane / Front Panel Interface                  | 96  |

|      |        | 10.6.3         | Fan Power Connector / Front Panel Interface                 | 96  |

|      |        | 10.6.4         | Chassis Intrusion Switch Connector / Front Panel Interface  | 96  |

|      |        | 10.6.5         | Fan Connector / Front Panel Interface                       | 96  |

| 11.  | Certi  | fication       |                                                             | 97  |

|      | 11.1 S | afety          |                                                             | 97  |

|      |        | 11.1.1         | USA                                                         | 97  |

|      |        | 11.1.2         | Canada                                                      | 97  |

|      |        | 11.1.3         | Europe                                                      | 97  |

|      |        | 11.1.4         | International                                               | 97  |

|      | 11.2 E | lectro-Mag     | netic Compatibility                                         | 97  |

|      |        | 11.2.1         | USA                                                         | 97  |

|      |        | 11.2.2         | Canada                                                      | 97  |

|      |        | 11.2.3         | Europe                                                      | 97  |

|      |        | 11.2.4         | International                                               | 97  |

|      |        | 11.2.5         | Japan                                                       | 97  |

|      | 11.3 E | Invironment    | tal Limits                                                  |     |

|      |        | 11.3.1         | System Office Environment                                   |     |

|      |        | 11.3.2         | System Environmental Testing                                | 98  |

| 12.  | Relia  | bility, Ser    | viceability and Availability                                |     |

|      |        |                | Between-Failure (MTBF)                                      |     |

|      | 12.2 S | Serviceability | y                                                           |     |

| Ар   | pendix | A.             | Supported Environments                                      | 100 |

| Ар   | pendix | В.             | Product Codes/Spares                                        | 101 |

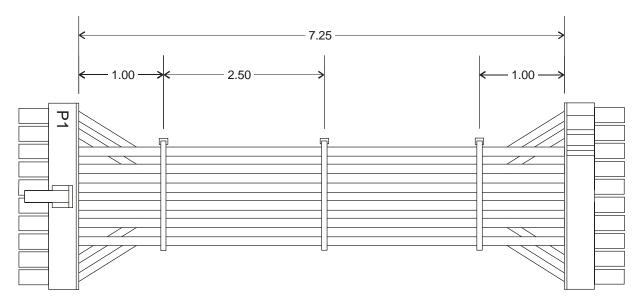

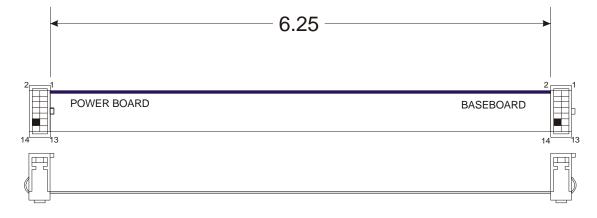

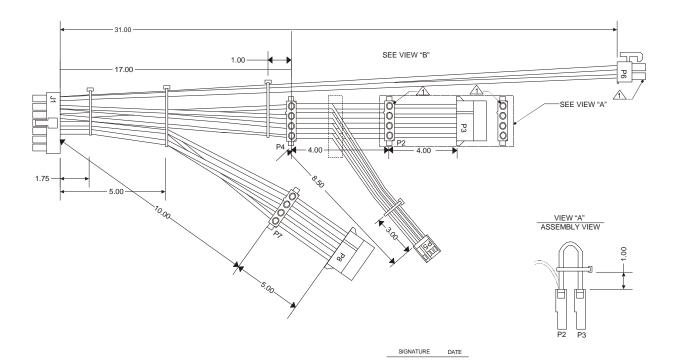

| Ар   | pendix | c.             | Cable Drawings                                              | 102 |

| Ар   | pendix | D.             | Customer Support                                            | 109 |

| Ap   | pendix | E.             | Errata                                                      |     |

| -1-1 |        |                | ed in Summary Table                                         |     |

|      |        |                | ,                                                           |     |

# 1. Board Set Descriptions

# 1.1 Baseboard Overview

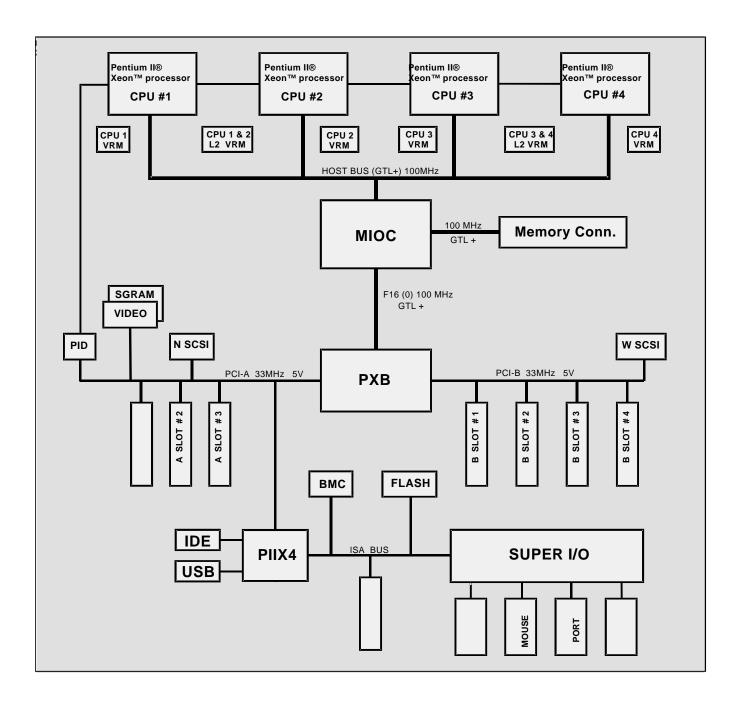

The Intel S450NX MP Server is a flat baseboard design featuring a quad Pentium<sup>®</sup> II Xeon<sup>™</sup> processor-based server system that combines the latest technology and integrated features to provide a high-performance platform at mid-range cost efficiency.

The S450NX MP Server baseboard utilizes the Intel 82450NX PCIset, the latest in chipset technology from Intel, to maximize system performance for 32-bit application software and operating systems.

The S450NX MP Server design is complemented with an array of features. These include:

- Edge connector interface to memory card supports up to 4GB of memory using commodity EDO DIMM devices.

- The Intel 82450NX PCIset as PCI host bridge and memory controller (Memory and I/O Controller (MIOC), PCI Expansion Bridge (PXB)).

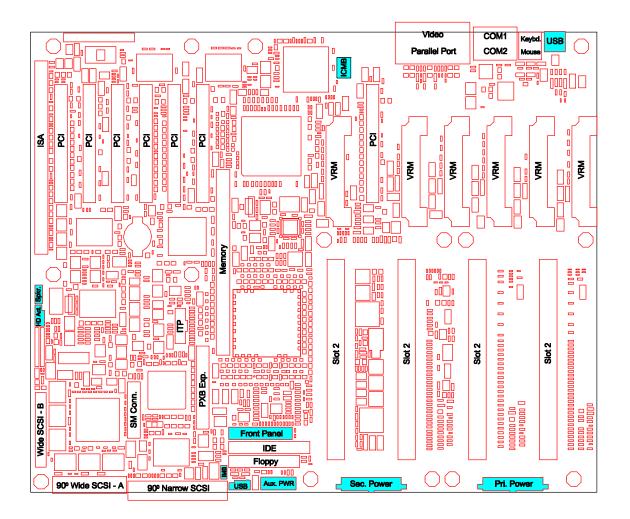

- Dual 32-bit, 33MHz PCI segments compliant with revision 2.1 of the PCI specification. PCI-A and PCI-B are provided by the PXB in the Intel 82450NX PCIset, with a total of 7 expansion slots; 3 on PCI-A, 4 on PCI-B (one shared with ISA).

- 1 ISA slot and PC Compatible I/O (serial, parallel, mouse, and keyboard).

- PIIX4(e) PCI-to-ISA bridge, IDE controller, USB controller, and power management.

- Other embedded PCI I/O devices, including SCSI, and IDE controllers.

- Server management features, including thermal/voltage monitoring, chassis intrusion detection, and fan failure detection.

- High-performance 2D PCI video controller (Cirrus Logic GD5480) with 2MB of SGRAM onboard.

- Four "Slot 2" Single Edge Contact (SEC) cartridge connectors (to accommodate 1 to 4 Pentium II® Xeon<sup>™</sup> processors and future processor upgrades).

The S450NX MP Server baseboard supports one to four Pentium II Xeon processors (conforming to the Slot 2 specification) contained on Single Edge Contact (SEC) cartridges. The SEC cartridges enclose the processor with integrated ECC L2 cache to enable high-frequency operation. The baseboard provides four "Slot 2" connectors, and connectors for six, VRM 8.3-compliant, plug-in voltage regulator modules. The S450NX MP Server baseboard design will accommodate identified upgrades to future Intel processing technology.

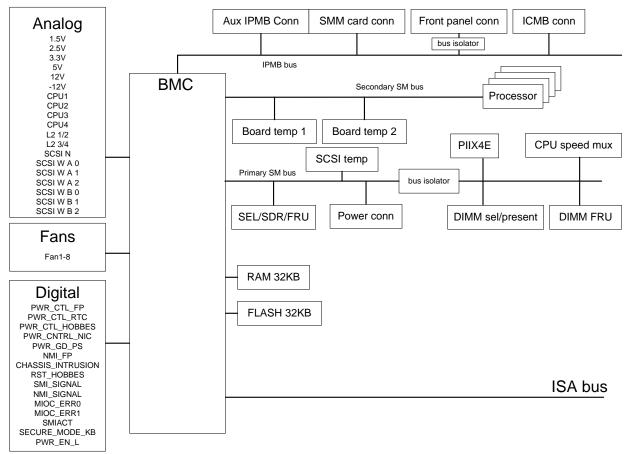

Figure 1.1: S450NX MP Server Functional Block Architecture

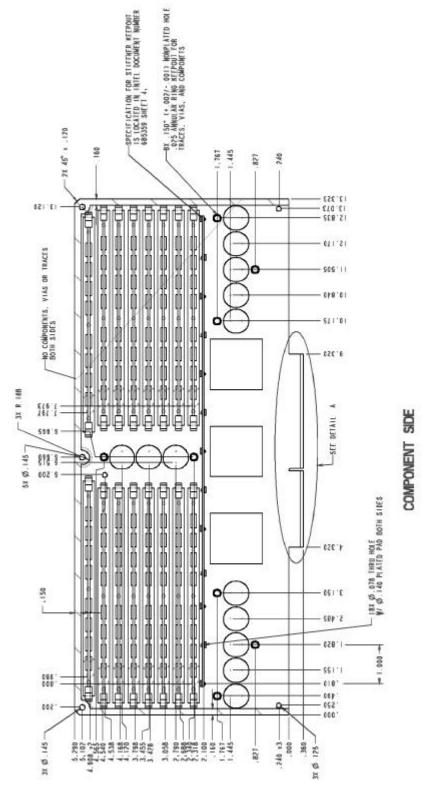

#### 1.1.1 Baseboard Diagram

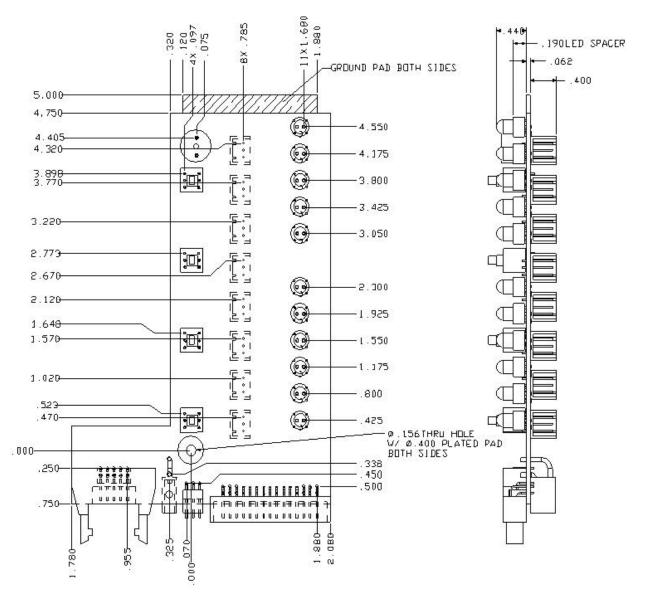

The following diagram shows the placement of major components and connector interfaces on the S450NX MP Server baseboard.

Figure 1.2: S450NX MP Baseboard Layout

# 1.2 Processor/PCI Host Bridge

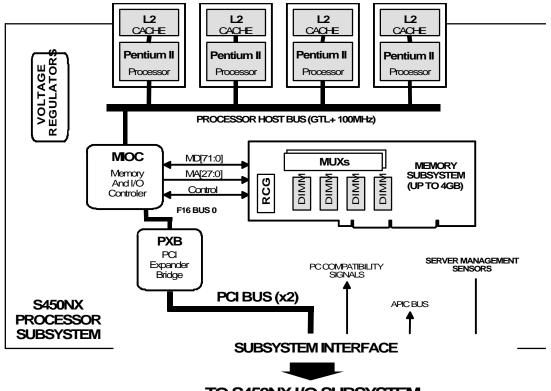

The processor/PCI bridge/memory sub-system consists of one to four identical Pentium II® Xeon<sup>™</sup> processors, a plug-in memory board, and support circuitry on the baseboard consisting of the following:

- Intel 82450NX PCIset which provides an integrated I/O bridge and memory controller and a flexible I/O sub-system core (PCI) optimized for multiprocessor systems and standard highvolume (SHV) servers

- Quad "Slot 2" edge connectors that accept Pentium II Xeon processors

- 242-pin connector interface to memory board

- Processor host bus AGTL+ support circuitry, including termination power supply

- Six sockets for plug-in VRMs to power SEC processor cartridges

- APIC bus

- Miscellaneous logic for reset configuration, processor presence detection, and server management

#### TO S450NX I/O SUBSYSTEM

Figure 1.3: Processor/PCI Host Bridge/Memory Sub-system

# **1.3** Pentium II® Xeon<sup>™</sup> Processor Cartridge

The S450NX MP Server Baseboard is designed to accommodate the Pentium II Xeon cartridge. The L1 cache, and L2 cache components are on a pre-assembled printed circuit board, approximately 4.8" x 6" in size. The L2 cache and processor core/L1 cache connect using a private bus isolated from the processor host bus. This L2 cache bus operates at the processor core frequency.

The Pentium II Xeon processor cartridge external interface is designed to be MP-ready. Each processor contains a local APIC section for interrupt handling. When four processor cartridges are installed, all processor cartridges must be of identical revision, core voltage, and bus/core speeds.

#### 1.3.1 Retention Module

The Pentium II® Xeon<sup>™</sup> processor retention module is used to add stability to the processor cartridge connector and a way of providing attachment to the baseboard. The processor retention module is attached with screws.

#### 1.3.2 Processor Cartridge Connector

The Pentium II Xeon processor cartridge edge connector conforms to the "Slot 2" specification, which can also accommodate future processor cartridges. The baseboard provides 4 Slot 2 processor cartridge connectors. Processors and Slot 2 connectors are keyed to ensure proper orientation.

#### 1.3.3 Processor Heat/Fan Sinks

The S450NX MP Server baseboard is not dependent on having fansinks, nor are fansinks supported by the S450NX MP Server baseboard.

#### 1.3.4 Processor Bus Termination/Regulation/Power

The termination circuitry required by the Pentium II processor bus (GTL+) signaling environment, and the circuitry to set the GTL+ reference voltage are implemented directly on the processor cartridges. The baseboard provides 1.5V GTL+ termination power (VTT), and VRM 8.3-compliant DC-to-DC converters to provide processor power (VCCP and L2) at each connector. Six sockets are provided on the baseboard for VRMs to power the processors, which derive power from the 12V supply. Refer to the VRM 8.3 DC-DC Converter Specification for more information.

#### 1.3.5 Termination Card

Logic is provided on the baseboard to detect the presence and identity of installed processor or termination cards. If any SEC processor cartridge is not installed in the system, a termination card *must* be installed in the vacant SEC processor cartridge slot to ensure reliable system operation. The termination card contains AGTL+ termination circuitry, clock signal termination, and Test Access Port (TAP) bypassing for the vacant connector. The system will not boot unless all slots are occupied with a processor or termination card.

#### 1.3.6 APIC Bus

Interrupt notification and generation for the processors is done using an independent path between local APICs in each processor and the Intel I/O APIC in PID located on the baseboard. This bus consists of 2 data signals and one clock line. Refer to "Interrupts and the PID" later in this chapter for more information.

# 1.4 82450NX PCIset

The Intel 82450NX PCIset provides an integrated I/O bridge and memory controller and a flexible I/O sub-system core (PCI), targeted for multi-processor systems and standard high-volume (SHV) servers based on the Pentium II® Xeon<sup>™</sup> processor. The Intel 82450NX PCIset consists of five components, as listed below:

**MIOC - Memory and I/O Controller**. The MIOC is responsible for accepting access requests from the host (processor) bus, and directing those accesses to memory or one of the PCI buses. The MIOC monitors the host bus, examining addresses for each request. Accesses may be directed to a memory request queue, for subsequent forwarding to the memory subsystem, or to an outbound request queue, for subsequent forwarding to the PXB and hence to the PCI buses. The MIOC also accepts inbound requests from the PXB representing requests from the PCI buses. The MIOC is also responsible for generating the appropriate controls to the RCG and MUX to control data transfer to and from the memory.

**PXB - PCI Expander Bridge.** The PXB provides the interface to two independent 32-bit 33MHz Rev 2.1-compliant PCI buses. The PXB is both master and target on each PCI bus. The two buses are processed completely independent except where transactions must be forwarded across the Expander (F16) Bus between PXB and MIOC.

**RCG - RAS/CAS Generator**. The RCG is responsible for accepting memory requests from the MIOC and converting these into the specific signals and timings required by the DRAM. **MUX - Data Path Multiplexers**. The two MUX components provide the multiplexing and staging required to support memory interleaving between the DRAMs and the MIOC.

#### 1.4.1 82450NX System I/O Access

The MIOC and PXB components provide the pathway between processor and I/O systems. The MIOC is responsible for accepting access requests from the host (processor) bus, and directing all I/O accesses to the PXB through the F16 Bus. The PXB then translates the F16 Bus operation to a 32-bit PCI Rev. 2.1 compliant, 5V signaling environment at 33MHz. The PXB also handles arbitration for the PCI bus segments.

The PCI interface provides greater than 100 MB/s data streaming for PCI to DRAM accesses, while supporting concurrent processor host bus and PCI transactions to main memory. This is accomplished using extensive data buffering, with processor-to-DRAM and PCI-to-DRAM write data buffering and write-combining support for processor-to-PCI burst writes.

#### 1.4.2 82450NX Main Memory Access

The MIOC also provides the memory controller for the system, issuing commands to the RCGs and MUXs, and accepting the data returned from the DRAMs. Memory amounts from 128MB to 4GB of DIMMs are supported, with a 64/72-bit four-way-interleaved pathway to main memory which is located on a plug-in module. The memory controller supports EDO DRAMs. The ECC used for the memory module is capable of correcting single-bit errors and detecting 100% of double-bit errors over one code word. Nibble error detection is also provided.

# 1.5 PCI-A I/O Sub-system

All I/O for S450NX, including PCI and PC-compatible, is directed through the PXB. The two PCI buses on S450NX run concurrently, with PCI-A and B at the same level. PCI-A supports the following embedded devices and connectors:

- Three 120-pin, 32-bit PCI expansion slot connectors, numbered PCI-A1, PCI-A2, PCI-A3

- PIIX4(e) PCI-to-ISA bridge, IDE controller, USB controller, and power management

- PCI video controller, Cirrus Logic CL-GD5480

- PCI narrow SCSI controller, Symbios 5353C810AE

- Programmable Interrupt Device (Intel ASIC; contains I/O APIC)

Each device under the PCI host bridge has its IDSEL signal connected to one bit out of AD[31:11], which acts as a chip select on the PCI bus segment. This determines a unique PCI device ID value for use in configuration cycles. The following table shows the bit to which each IDSEL signal is attached for PCI-A devices, and corresponding device number. Refer to "Accessing Configuration Space" in Chapter 3 for more information.

| Tuble III   | 1. I CI-A Configuration IDs |

|-------------|-----------------------------|

| IDSEL Value | Device                      |

| 22          | PCI Slot PCI-A1             |

| 23          | PCI Slot PCI-A2             |

| 24          | PCI Narrow SCSI             |

| 25          | PCI Slot PCI-A3             |

| 26          | PCI Video                   |

| 27          | Programmable Interrupt      |

|             | Device                      |

| 28          | PIIX4(e)                    |

Table 1.1: PCI-A Configuration IDs

#### 1.5.1 PCI-A Arbitration

PCI-A supports seven PCI masters (slots PCI-A1 through PCI-A3, PID, PIIX4(e), Narrow SCSI, and the PXB). All PCI masters must arbitrate for PCI access, using resources supplied by the PXB. The host bridge PCI interface arbitration lines REQx\_L and GNTx\_L are a special case in that they are internal to the host bridge. PIIX4(e) arbitration signals are also a special case so that access time capability for ISA masters is guaranteed. The following table defines the arbitration connections:

| Table 1.2: PCI-A Arbit | ration Connections |

|------------------------|--------------------|

| Baseboard Signals      | Device             |

| PA_PHOLD_L/P_PHLDA_L   | PIIX4(e)           |

| PA_REQ0_L/P_GNT0_L     | PCI-A Slot PCI-A1  |

| PA_REQ1_L/P_GNT1_L     | PCI-A Slot PCI-A2  |

| PA_REQ2_L/P_GNT2_L     | PCI-A Slot PCI-A3  |

| PA_REQ3_L/P_GNT3_L     | Video GD5480       |

| PA_REQ4_L/P_GNT4_L     | Narrow SCSI        |

| PA_REQ5_L/P_GNT5_L     | PID                |

11

#### 1.5.2 PCI-to-ISA/IDE/USB Controller PIIX4(e)

The PIIX4(e), is a multi-function PCI device, providing 4 PCI functions in a single package: PCI-to-ISA bridge, PCI IDE interface, PCI USB controller, and power management controller. Each function within the PIIX4(e) has its own set of configuration registers and once configured, each appears to the system as a distinct hardware controller sharing the same PCI bus interface.

The PIIX4(e) fully implements a 32-bit PCI master/slave interface, in accordance with the PCI Local Bus Specification, Rev. 2.1. The PCI interface operates at 33 MHz, using the 5V-signaling environment. The PIIX4(e) provides an ISA bus interface, operating at 8.33 MHz that supports a single ISA connector, Flash memory, server management interface, and the SuperI/O controller.

The Fast IDE controller in the PIIX4(e) supports programmed I/O transfers up to 14MB/s and bus master IDE transfers up to 33MB/s.

The PIIX4(e) contains a USB controller and two port USB hub. The USB controller moves data between main memory and up to two devices each connected on either the external or internal USB header. The S450NX MP Server baseboard provides a single external USB connector interface for the back panel, and a special internal header to be used with device bay expansion. The external USB port, logically Port B, is defined by the USB Specification, Revision 1.0, with the pin-out shown in table 1.3.

| Pin | Name  | Comment                           |

|-----|-------|-----------------------------------|

| 1   | VCC   | CABLE POWER                       |

| 2   | DATA- | Data (differential pair negative) |

| 3   | DATA+ | Data (differential pair positive) |

| 4   | GND   | CABLE GROUND                      |

#### **Table 1.3: USB Connector Pin-out**

The internal USB header has been defined to work with device bay; it is logically Port A. Power is not supplied by the baseboard for this port. The header pin-out is shown in table 1.4. Table 1 4. USB Header Pin-out

| Pin | Name  | Comment                           |

|-----|-------|-----------------------------------|

| 1   |       | nc                                |

| 2   | DATA- | Data (differential pair negative) |

| 3   | DATA+ | Data (differential pair positive) |

| 4   | GND   | CABLE GROUND                      |

#### 1.6 PCI-A Narrow SCSI

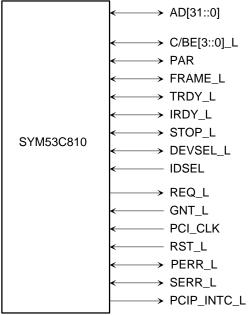

The PCI-A bus provides an embedded narrow SCSI host adapter: Symbios SYM53C810AE. The SYM53C810AE contains a high-performance SCSI core capable of Fast 8-bit SCSI transfers in singleended mode. The high-performance SCSI core, PCI bus master DMA, and internal SCRIPTS\* processor meets SCSI-1 and SCSI-2 standards. This part provides programmable active negation, PCI zero wait-state bursts of faster than 110MB/s at 33MHz and SCSI transfers rates from 5MB/s to 10MB/s.

### 1.6.1 SYM53C810AE PCI Signals

The SYM53C810AE supports all of the required 32-bit PCI signals including the PERR\_L and SERR\_L functions. Full PCI parity is maintained on the entire data path through the component. The device also takes advantage of a PCI interrupt resource to operate. The 53C810AE does not support the CLKRUN\_L, LOCK\_L, SBO\_L, SDONE\_L, INTB/C/D\_L, TCK, TDI, TDO, TMS, and TRST\_L signals. The SYM53C810AE interrupt request signal connects to P\_INTC\_L on the S450NX MP Server baseboard.

Figure 1.4: Embedded Narrow SCSI PCI Signals

# 1.7 PCI-A Video

The S450NX MP Server baseboard integrates a Cirrus Logic CL-GD5480 video controller, along with video SGRAM and support circuitry for an embedded SVGA video sub-system. The CL-GD5480 64-bit VGA Graphics Accelerator component contains an SVGA video controller, clock generator, Bit BLT engine, and RAMDAC. Two 256K x 32 SGRAM components provide 2 MB of 10ns video memory. The SVGA sub-system supports a variety of modes: up to 1600 x 1200 resolution, and up to 16.7 M colors. It also supports analog VGA monitors, single- and multi-frequency, interlaced and non-interlaced, up to 100Hz vertical retrace frequency. The S450NX MP Server baseboard also provides a standard 15-pin VGA connector, and external video blanking logic for server management support.

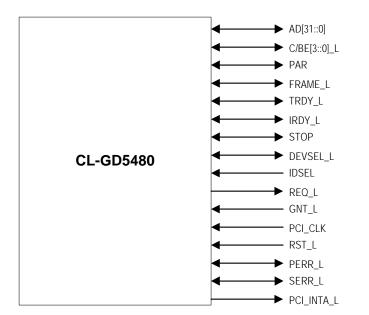

#### 1.7.1 Video Component PCI Signals

The CL-GD5480 is a 32-bit PCI device with PCI master capability. Below is a diagram of the PCI signals used.

Figure 1.5: Video Controller PCI Signals

#### 1.7.2 Video Controller PCI Commands

The CL-GD5480 supports the following PCI commands:

| Table 1.5: Video Component Supported PCI Comman |

|-------------------------------------------------|

|-------------------------------------------------|

|              |                             | GD54   | 480 Support |

|--------------|-----------------------------|--------|-------------|

| C/BE[3::0]_L | Command Type                | Target | Master      |

| 0000         | Interrupt Acknowledge       | No     | No          |

| 0001         | Special Cycle               | No     | No          |

| 0010         | I/O Read                    | Yes    | No          |

| 0011         | I/O Write                   | Yes    | No          |

| 0100         | Reserved                    | No     | No          |

| 0101         | Reserved                    | No     | No          |

| 0110         | Memory Read                 | Yes    | No          |

| 0111         | Memory Write                | Yes    | No          |

| 1000         | Reserved                    | No     | No          |

| 1001         | Reserved                    | No     | No          |

| 1010         | Configuration Read          | Yes    | No          |

| 1011         | Configuration Write         | Yes    | No          |

| 1100         | Memory Read Multiple        | No     | No          |

| 1101         | Dual Address Cycle          | No     | No          |

| 1110         | Memory Read Line            | No     | No          |

| 1111         | Memory Write and Invalidate | No     | No          |

#### 1.7.3 Video Modes

The CL-GD5480 supports all standard IBM VGA modes. Using 2MB of SGRAM, the S450NX MP Server supports special Cirrus Logic extended modes. The following tables show the standard and extended modes that this implementation supports, including the number of colors and palette size (e.g., 16 colors out of 256 K colors), resolution, pixel frequency, and scan frequencies.

| Mode(s)<br>in Hex | Colors (number<br>/palette size) | Resolution | Pixel Freq.<br>(MHz) | Horiz. Freq.<br>(KHz) | Vert. Freq.<br>(Hz) |

|-------------------|----------------------------------|------------|----------------------|-----------------------|---------------------|

| 0, 1              | 16/256K                          | 360 X 400  | 14                   | 31.5                  | 70                  |

| 2, 3              | 16/256K                          | 720 X 400  | 28                   | 31.5                  | 70                  |

| 4, 5              | 4/256K                           | 320 X 200  | 12.5                 | 31.5                  | 70                  |

| 6                 | 2/256K                           | 640 X 200  | 25                   | 31.5                  | 70                  |

| 7                 | Mono                             | 720 X 400  | 28                   | 31.5                  | 70                  |

| D                 | 16/256K                          | 320 X 200  | 12.5                 | 31.5                  | 70                  |

| E                 | 16/256K                          | 640 X 200  | 25                   | 31.5                  | 70                  |

| F                 | Mono                             | 640 X 350  | 25                   | 31.5                  | 70                  |

| 10                | 16/256K                          | 640 X 350  | 25                   | 31.5                  | 70                  |

| 11                | 2/256K                           | 640 X 480  | 25                   | 31.5                  | 60                  |

| 12                | 16/256K                          | 640 X 480  | 25                   | 31.5                  | 60                  |

| 12+               | 16/256K                          | 640 X 480  | 31.5                 | 37.5                  | 75                  |

| 13                | 256/256K                         | 320 X 200  | 12.5                 | 31.5                  | 70                  |

#### Table 1.6: Standard VGA Modes

Table 1.7: Extended VGA Modes

| Mode(s)<br>in Hex | Colors                | Resolution | Pixel Freq.<br>(MHz) | Horiz. Freq.<br>(KHz) | Vert. Freq.<br>(Hz) |

|-------------------|-----------------------|------------|----------------------|-----------------------|---------------------|

| 58, 6A            | 16/256K               | 800 X 600  | 36                   | 35.2                  | 56                  |

| 58, 6A            | 16/256K               | 800 X 600  | 40                   | 37.8                  | 60                  |

| 58, 6A            | 16/256K               | 800 X 600  | 50                   | 48.1                  | 72                  |

| 58, 6A            | 16/256K               | 800 X 600  | 49.5                 | 46.9                  | 75                  |

| 5C                | 256/256K              | 800 X 600  | 36                   | 35.2                  | 56                  |

| 5C                | 256/256K              | 800 X 600  | 40                   | 37.9                  | 60                  |

| 5C                | 256/256K              | 800 X 600  | 50                   | 48.1                  | 72                  |

| 5C                | 256/256K              | 800 X 600  | 49.5                 | 46.9                  | 75                  |

| 5C                | 256/256K              | 800 X 600  | 56.25                | 53.7                  | 85                  |

| 5C                | 256/256K              | 800 X 600  | 68.2                 | 63.6                  | 100                 |

| 5D                | 16/256K (interlaced)  | 1024 X 768 | 44.9                 | 35.5                  | 43                  |

| 5D                | 16/256K               | 1024 X 768 | 65                   | 48.3                  | 60                  |

| 5D                | 16/256K               | 1024 X 768 | 75                   | 56                    | 70                  |

| 5D                | 16/256K               | 1024 X 768 | 78.7                 | 60                    | 75                  |

| 5E                | 256/256K              | 640 X 400  | 25                   | 31.5                  | 70                  |

| 5F                | 256/256K              | 640 X 480  | 25                   | 31.5                  | 60                  |

| 5F                | 256/256K              | 640 X 480  | 31.5                 | 37.9                  | 72                  |

| 5F                | 256/256K              | 640 X 480  | 31.5                 | 37.5                  | 75                  |

| 5F                | 256/256K              | 640 X 480  | 36                   | 43.3                  | 85                  |

| 5F                | 256/256K              | 640 X 480  | 43.2                 | 50.9                  | 100                 |

| 60                | 256/256K (interlaced) | 1024 X 768 | 44.9                 | 35.5                  | 43                  |

| 60                | 256/256K              | 1024 X 768 | 65                   | 48.3                  | 60                  |

| 60                | 256/256K              | 1024 X 768 | 75                   | 56                    | 70                  |

| 60                | 256/256K              | 1024 X 768 | 78.7                 | 60                    | 75                  |

| 60                | 256/256K              | 1024 X 768 | 94.5                 | 68.3                  | 85                  |

| 60                | 256/256K              | 1024 X 768 | 113.3                | 81.4                  | 100                 |

| 64                | 64K                   | 640 X 480  | 25                   | 31.5                  | 60                  |

| 64                | 64K                   | 640 X 480  | 31.5                 | 37.9                  | 72                  |

| 64                | 64K                   | 640 X 480  | 31.5                 | 37.5                  | 75                  |

Table 1.7: Extended VGA Modes (cont.)

| Mode(s)<br>in Hex | Colors                | Resolution    | Pixel Freq.<br>(MHz) | Horiz. Freq.<br>(KHz) | Vert.<br>Freq. (Hz) |

|-------------------|-----------------------|---------------|----------------------|-----------------------|---------------------|

| 64                | 64K                   | 640 X 480     | 36                   | 43.3                  | 85                  |

| 64                | 64K                   | 640 X 480     | 43.2                 | 50.9                  | 100                 |

| 65                | 64K                   | 800 X 600     | 36                   | 35.2                  | 56                  |

| 65                | 64K                   | 800 X 600     | 40                   | 37.8                  | 60                  |

| 65                | 64K                   | 800 X 600     | 50                   | 48.1                  | 72                  |

| 65                | 64K                   | 800 X 600     | 49.5                 | 46.9                  | 75                  |

| 65                | 64K                   | 800 X 600     | 56.25                | 53.7                  | 85                  |

| 65                | 64K                   | 800 X 600     | 68.2                 | 63.6                  | 100                 |

| 66                | 32K                   | 640 X 480     | 25                   | 31.5                  | 60                  |

| 66                | 32K                   | 640 X 480     | 31.5                 | 37.9                  | 72                  |

| 66                | 32K                   | 640 X 480     | 31.5                 | 37.5                  | 75                  |

| 66                | 32K                   | 640 X 480     | 36                   | 43.3                  | 85                  |

| 66                | 32K                   | 640 X 480     | 43.2                 | 50.9                  | 100                 |

| 67                | 32K                   | 800 X 600     | 36                   | 35.2                  | 56                  |

| 67                | 32K                   | 800 X 600     | 40                   | 37.8                  | 60                  |

| 67                | 32K                   | 800 X 600     | 50                   | 48.1                  | 72                  |

| 67                | 32K                   | 800 X 600     | 49.5                 | 46.9                  | 75                  |

| 67                | 32K                   | 800 X 600     | 56.25                | 53.7                  | 85                  |

| 67                | 32K                   | 800 X 600     | 68.2                 | 63.6                  | 100                 |

| 68                | 32K (interlaced)      | 1024 X 768    | 44.9                 | 35.5                  | 43                  |

| 68                | 32K                   | 1024 X 768    | 65                   | 48.3                  | 60                  |

| 68                | 32K                   | 1024 X 768    | 75                   | 56                    | 70                  |

| 68                | 32K                   | 1024 X 768    | 78.7                 | 60                    | 75                  |

| 68                | 32K                   | 1024 X 768    | 94.5                 | 68.3                  | 85                  |

| 68                | 32K                   | 1024 X 768    | 113.3                | 81.4                  | 100                 |

| 6C                | 16/256K (interlaced)  | 1280 X 1024   | 75                   | 48                    | 43                  |

| 6D                | 256/256K (interlaced) | 1280 X 1024   | 75                   | 48                    | 43                  |

| 6D                | 256/256K              | 1280 X 1024   | 108                  | 65                    | 60                  |

| 6D                | 256/256K              | 1280 X 1024   | 135                  | 80                    | 75                  |

| 6D                | 256/256K              | 1280 X 1024   | 157.5                | 91                    | 85                  |

| 6E                | 32K                   | 1152 X 864    | 94.5                 | 63.9                  | 70                  |

| 6E                | 32K                   | 1152 X 864    | 108                  | 67.5                  | 75                  |

| 6E                | 32K                   | 1152 X 864    | 121.5                | 76.7                  | 85                  |

| 6E                | 32K                   | 1152 X 864    | 143.5                | 91.5                  | 100                 |

| 71                | 16M                   | 640 X 480     | 25                   | 31.5                  | 60                  |

| 71                | 16M                   | 640 X 480     | 31.5                 | 37.9                  | 72                  |

| 71                | 16M                   | 640 X 480     | 31.5                 | 37.5                  | 75                  |

| 71                | 16M                   | 640 X 480     | 36                   | 43.3                  | 85                  |

| 71                | 16M                   | 640 X 480     | 43.2                 | 50.9                  | 100                 |

| 74                | 64K (interlaced)      | 1024 X 768    | 44.9                 | 35.5                  | 43                  |

| 74                | 64K                   | 1024 X 768    | 65                   | 48.3                  | 60                  |

| 74                | 64K                   | 1024 X 768    | 75                   | 56                    | 70                  |

| 74                | 64K                   | 1024 X 768    | 78.7                 | 60                    | 75                  |

| 74                | 64K                   | 1024 X 768    | 94.5                 | 68.3                  | 85                  |

| 74                | 64K                   | 1024 X 768    | 113.3                | 81.4                  | 100                 |

| 78                | 32K                   | 800 X 600     | 36                   | 35.2                  | 56                  |

| _ · •             |                       | : Extended VG |                      |                       | 20                  |

| Mode(s)           | Colors                | Resolution    | Pixel Freq.          | Horiz. Freq.          | Vert.<br>Freq (Hz)  |

| in Hex            | 16M                   | 800 X 600     | (MHz)                | (KHz)                 | Freq. (Hz)          |

| 78                | 16M                   | 800 X 600     | 40                   | 37.8                  | 60                  |

#### 16

| 78 | 16M                   | 800 X 600   | 50    | 48.1 | 72  |

|----|-----------------------|-------------|-------|------|-----|

| 78 | 16M                   | 800 X 600   | 49.5  | 46.9 | 75  |

| 78 | 16M                   | 800 X 600   | 56.25 | 53.7 | 85  |

| 78 | 16M                   | 800 X 600   | 68.2  | 63.6 | 100 |

| 7B | 256/256K (interlaced) | 1600 X 1200 | 135   | 62.5 | 48  |

| 7B | 256/256K              | 1600 X 1200 | 162   | 75   | 60  |

| 7C | 256/256K              | 1152 X 864  | 94.5  | 63.9 | 70  |

| 7C | 256/256K              | 1152 X 864  | 108   | 67.5 | 75  |

| 7C | 256/256K              | 1152 X 864  | 121.5 | 76.7 | 85  |

| 7C | 256/256K              | 1152 X 864  | 143.5 | 91.5 | 100 |

| 7D | 64K                   | 1152 X 864  | 94.5  | 63.9 | 70  |

| 7D | 64K                   | 1152 X 864  | 108   | 67.5 | 75  |

| 7D | 64K                   | 1152 X 864  | 121.5 | 76.7 | 85  |

| 7D | 64K                   | 1152 X 864  | 143.5 | 91.5 | 100 |

For more information refer to the Cirrus Logic GD5480 Technical Reference Manual.

## 1.7.4 VGA connector

The following table shows the pin-out of the VGA connector:

| _   | Table 1.8: Video Port Connector Pin-out |                       |  |  |  |

|-----|-----------------------------------------|-----------------------|--|--|--|

| Pin | Signal                                  | Description           |  |  |  |

| 1   | RED                                     | Analog color signal R |  |  |  |

| 2   | GREEN                                   | Analog color signal G |  |  |  |

| 3   | BLUE                                    | Analog color signal B |  |  |  |

| 4   | nc                                      | No connect            |  |  |  |

| 5   | GND                                     | Video ground (shield) |  |  |  |

| 6   | GND                                     | Video ground (shield) |  |  |  |

| 7   | GND                                     | Video ground (shield) |  |  |  |

| 8   | GND                                     | Video ground (shield) |  |  |  |

| 9   | nc                                      | No connect            |  |  |  |

| 10  | GND                                     | Video ground          |  |  |  |

| 11  | nc                                      | No connect            |  |  |  |

| 12  | DDCDAT                                  | Monitor ID data       |  |  |  |

| 13  | HSYNC                                   | Horizontal Sync       |  |  |  |

| 14  | VSYNC                                   | Vertical Sync         |  |  |  |

| 15  | DDCCLK                                  | Monitor ID clock      |  |  |  |

For more information refer to the Cirrus Logic GD5480 Technical Reference Manual.

# 1.8 PCI-B I/O Sub-system

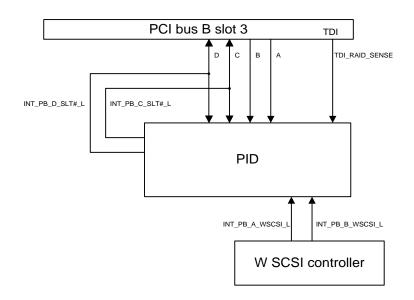

PCI segments A and B are non-hierarchical and exist at the same level. PCI-B supports the following embedded devices and connectors:

- One Symbios SYM53C896 dual-channel SCSI-3 Ultra2 SCSI controller.

- Four 120-pin, 32-bit PCI expansion slot connectors, numbered PCI-B1, PCI-B2, PCI-B3, PCI-B4. Slot PCI-B4 is shared with an ISA slot.

- Slot PCI-B3 also supports the optional I<sub>2</sub>O RAID card.

The PCI IDSEL signal connections to PCI AD[31::11] lines for PCI-B devices are shown in the following table.

| IDSEL Value | Device               |

|-------------|----------------------|

| 17          | PCI Slot PB1         |

| 18          | PCI Slot PCI-B2      |

| 19          | Wide SCSI Controller |

| 20          | PCI Slot PCI-B3      |

| 21          | PCI Slot PCI-B4      |

#### Table 1.9: PCI-B Configuration IDs

#### 1.8.1 PCI-B Arbitration

PCI-B supports six PCI masters: slots PCI-B1 through PCI-B4, the wide SCSI controller, and the PXB. All PCI masters must arbitrate for PCI access using resources supplied by the PXB. The PXB PCI-B interface arbitration connections are internal to the device. The following table defines the external arbitration connections:

| Baseboard Signals | Device               |

|-------------------|----------------------|

| S_REQ0_L/S_GNT0_L | PCI Slot PCI-B1      |

| S_REQ1_L/S_GNT1_L | PCI Slot PCI-B2      |

| S_REQ2_L/S_GNT2_L | PCI Slot PCI-B3      |

| S_REQ3_L/S_GNT3_L | PCI Slot PCI-B4      |

| S_REQ4_L/S_GNT4_L | unused               |

| S_REQ5_L/S_GNT5_L | Wide SCSI controller |

Table 1.10: PCI-B Arbitration Connections

## 1.9 PCI-B Wide SCSI

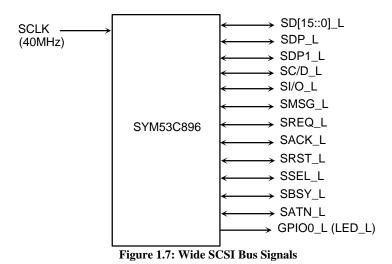

PCI-B provides an embedded Symbios SYM53C896 dual channel LVD/SE (Ultra2/Ultra) SCSI controller. The SYM53C896 supports SE mode with 8-bit (10 MB/s or 20 MB/s) or 16-bit (20 MB/s or 40 MB/s) transfers and LVD mode with 8-bit (40 MB/s) or 16-bit (80 MB/s) transfers. The SYM53C896 is a highly integrated PCI-to-SCSI solution containing a high-performance PCI bus interface, DMA controller, internal SCRIPTS\* engine, and a high-performance SCSI bus interface. PCI performance features include bursts of up to 128 Dwords for data rates of greater than 110 MB/s. The SCRIPTS\* engine is a special high-speed processor optimized for SCSI protocol. The SCRIPTS engine and 8 KB of internal RAM for instruction storage can execute complex SCSI bus sequences independently of the host processor. The internal DMA, in combination with the SCRIPTS engine, creates a tightly-coupled connection between PCI and SCSI bus interfaces for optimum performance.

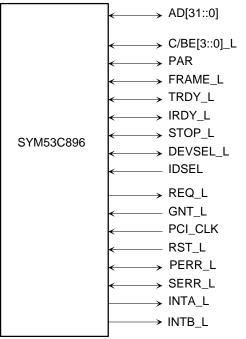

#### 1.9.1 SYM53C896 PCI Signals

The SYM53C896 is a 64-bit PCI device and is interfaced to the 32-bit PCI bus in the S450NX MP Server. It supports all of the required 32-bit PCI signals including PERR\_L and SERR\_L. Full PCI parity is maintained on the entire data path through the component. The device has two programmable interrupt outputs which are connected to the PID. Refer to "Interrupts and the PID" later in this chapter for more details on interrupt routing in the I/O sub-system. The SYM53C896 does not support the CLKRUN\_L, LOCK\_L, SBO\_L, SDONE\_L and TRST\_L signals. Support for these signals is specified as optional under the PCI 2.1 Specification.

Figure 1.6: Embedded Wide SCSI PCI Signals

#### 1.9.2 SCSI Interface

The SYM53C896 offers 8-bit or 16-bit SCSI operation at data transfer rates of 10, 20, 40, or 80 MB/s. The SYM53C896 uses Tolerant\* technology for improved data integrity when running in the fastest SCSI transfer modes. Tolerant\* technology includes active negation of SCSI signals when driving and programmable input signal filtering when receiving. Active negation outputs reduce the chance of data errors by actively driving both polarities of the SCSI bus avoiding indeterminate voltage levels and common-mode noise on long cable runs.

The SYM53C896 supports the SCSI 2, 8 or 16-bits wide bus with odd parity generated per byte. SCSI control signals are the same for either bus width. All SCSI signals are active low. SCSI P-connector cabling connects easily. During component power-down, all inputs are disabled to reduce power consumption.

# 1.10 ISA I/O Sub-system

On the S450NX MP Server, the PIIX4(e) provides a bridge to an ISA I/O sub-system that supports the following connectors and devices:

• 1 ISA connector slot which supports slave only cards (**bus master cards are not supported**) and is physically shared with PCI slot PCI-B4.

ISA Slot Length Restriction: If wide SCSI channel B is used, only half length ISA cards are supported.

- Flash memory for BIOS ROM and extensions.

- Baseboard Management Controller (BMC).

- PC87309 SuperI/O component, which supports the following:

- $\Rightarrow$  2 PC-compatible serial ports

- ⇒ Enhanced parallel port

- $\Rightarrow$  Floppy controller

- ⇒ Keyboard/Mouse ports

The ISA interrupts are handled by either the PIIX4(e) or the PID. The PID handles interrupts in an MP environment. Refer to "Interrupts and the PID" later in this chapter for more information on these devices and how they are used in the S450NX MP Server interrupt structure.

#### 1.10.1 I/O Controller Sub-system

The National 87309 SuperI/O device contains all of the necessary circuitry to control two serial ports, one parallel port, floppy disk, and PS/2-compatible keyboard and mouse. The S450NX MP Server provides the connector interface for each. Upon reset, the National 87309 reads the values on 3 GPO pins to determine its boot-up configuration. The S450NX MP Server baseboard configures the SuperI/O into Plug and Play baseboard and 2 UART modes.

#### 1.10.2 Serial Ports

Two 9-pin connectors are provided in one stacked 9-pin D-Sub housing for Serial port A and Serial port B. By default port A is physically the top connector, port B is on the bottom. Both ports are compatible with 16550A and 16450 modes and are re-locatable. Each serial port can be set to 1 of 4 different COM ports and can be enabled separately. When enabled, each port can be programmed to generate edge or level sensitive interrupts. When disabled, serial port interrupts are available to add-in cards. Pin-out is shown below:

| Pin | Name | Description            |

|-----|------|------------------------|

| 1   | DCD  | Data Carrier Detected  |

| 2   | RXD  | Receive Data           |

| 3   | TXD  | Transmit Data          |

| 4   | DTR  | Data Terminal Ready    |

| 5   | GND  | Ground                 |

| 6   | DSR  | Data Set Ready         |

| 7   | RTS  | Request to Send        |

| 8   | CTS  | Clear to Send          |

| 9   | RIA  | Ring Indication Active |

#### 1.10.3 Parallel Port

The 25/15 pin connector stacks the parallel port connector over the VGA connector. BIOS programming of the National 87309 registers enable the parallel port, and determine the port address and interrupt. When disabled, the interrupt is available to add-in cards. Pin-out is shown below:

| Pin | Name     | Pin | Name     |

|-----|----------|-----|----------|

| 1   | STROBE_L | 14  | AUFDXT_L |

| 2   | D0       | 15  | ERROR_L  |

| 3   | D1       | 16  | INIT_L   |

| 4   | D2       | 17  | SLCTIN_L |

| 5   | D3       | 18  | GND      |

| 6   | D4       | 19  | GND      |

| 7   | D5       | 20  | GND      |

| 8   | D6       | 21  | GND      |

| 9   | D7       | 22  | GND      |

| 10  | ACK_L    | 23  | GND      |

| 11  | BUSY     | 24  | GND      |

| 12  | PE       | 25  | GND      |

| 13  | SLCT     |     |          |

#### Table 1.12: Parallel Port Connector Pin-out

#### 1.10.4 Floppy Disk Controller

The FDC in the National 87309 is functionally compatible with floppy disk controllers in the DP8473 and N82077. The baseboard provides the 24MHz clock, termination resistors, and chip selects. All other FDC functions are integrated into the National 87309 including analog data separator and 16-byte FIFO. The floppy connector on the baseboard has the pin-out shown in table 1.13.

| Pin | Name       | Pin | Name        |

|-----|------------|-----|-------------|

| 1   | GND        | 18  | FD_DIR_L    |

| 2   | FD_DENSEL  | 19  | GND         |

| 3   | GND        | 20  | FD_STEP_L   |

| 4   | n/c        | 21  | GND         |

| 5   | Key        | 22  | FD_WDATA_L  |

| 6   | FD_DRATE0  | 23  | GND         |

| 7   | GND        | 24  | FD_WGATE_L  |

| 8   | FD_INDEX_L | 25  | GND         |

| 9   | GND        | 26  | FD_TRK0_L   |

| 10  | FD_MTR0_L  | 27  | FD_MSEN0    |

| 11  | GND        | 28  | FD_WPROT_L  |

| 12  | FD_DR1_L   | 29  | GND         |

| 13  | GND        | 30  | FD_RDATA_L  |

| 14  | FD_DR0_L   | 31  | GND         |

| 15  | GND        | 32  | FD_HDSEL_L  |

| 16  | FD_MTR1_L  | 33  | GND         |

| 17  | FD_MSEN1   | 34  | FD_DSKCHG_L |

#### Table 1.13: Floppy Port Connector Pin-out

#### 1.10.5 Keyboard and Mouse Connectors

The keyboard and mouse connectors are mounted within a single stacked housing. The mouse connector is stacked over the keyboard connector. External to the board they appear as two connectors. The keyboard controller is functionally compatible with the 8042A. The keyboard and mouse connectors are PS/2 compatible, with pin-outs shown in tables 1.14 and 1.15.

| -   | Table 1.14: Keyboard Connector Pin-out |                |  |  |  |

|-----|----------------------------------------|----------------|--|--|--|

| Pin | Signal                                 | Description    |  |  |  |

| 1   | KEYDAT                                 | Keyboard Data  |  |  |  |

| 2   | (NC)                                   |                |  |  |  |

| 3   | GND                                    | Ground         |  |  |  |

| 4   | FUSED_VCC                              | +5 V, fused    |  |  |  |

| 5   | KEYCLK                                 | Keyboard Clock |  |  |  |

| 6   | (NC)                                   |                |  |  |  |

#### Table 1.15: Mouse Connector Pin-out

| Pin | Signal    | Description |  |

|-----|-----------|-------------|--|

| 1   | MSEDAT    | Mouse Data  |  |

| 2   | (NC)      |             |  |

| 3   | GND       | Ground      |  |

| 4   | FUSED_VCC | +5 V, fused |  |

| 5   | MSECLK    | Mouse Clock |  |

| 6   | (NC)      |             |  |

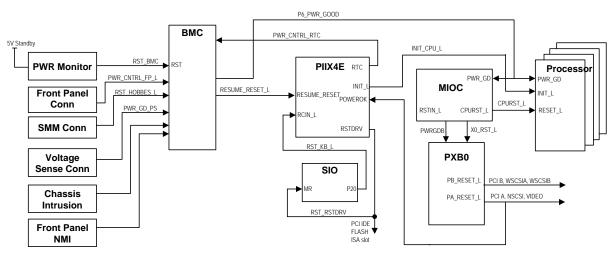

# 1.11 System Reset Control

Reset circuitry on the S450NX MP Server baseboard looks at resets from the front panel, PIIX4(e), I/O controller, and processor sub-system to determine proper reset sequencing for all types of reset. The reset logic is designed to accommodate a variety of ways to reset the system, which can be divided into the following categories:

- Power-up reset

- Hard reset

- Soft (programmed) reset

#### 1.11.1 Power-up Reset

When the system is disconnected from power, all logic on the baseboard is not powered. When proper AC line voltage is provided to the power supply, 5 Volt standby power will be applied to the baseboard. A power monitor circuit on 5 Volt standby will assert RST\_BMC, causing the Baseboard Management Controller (BMC) to reset. The BMC is powered by 5 Volt standby and monitors and controls key events in the system related to reset and power control.

#### 1.11.2 Hard Reset

Hard reset may be initiated by software, by the user resetting the system through the front panel switch, or through the Server Management Module. For a software initiated reset, the MIOC Reset Control (RC) register should be used. The BMC is not reset by a hard reset. It may be reset at power-up.

#### 1.11.3 Soft Reset

Soft reset causes the processors to begin execution in a known state without flushing caches or internal buffers. Soft resets may be generated by the keyboard controller located in the 87309 SIO, by the PIIX4(e), or by the MIOC. The output of the 87309 is input to the PIIX4(e), and combined with its internal sources to drive the PIIX4(e). Both the PIIX4(e) and MIOC are open collector signals and are wire ORed on baseboard and connected to the Slot 2 connectors.

#### 1.11.4 Reset Diagram

Reset flows throughout the S450NX MP Server baseboard as shown in the following figure.

Figure 1.8: Reset Flow Diagram

## 1.12 Clock Generation and Distribution

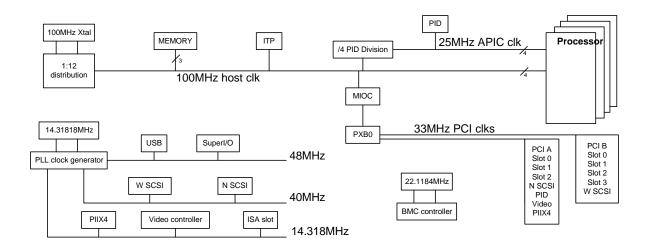

There are three clock sources used on the S450NX MP Server baseboard. The 100MHz host clocks are generated from a 1:12 clock distribution component. The MIOC generates the 100MHz clock for the two F16 busses to the PXBs. The PXB generates two 33.3MHz PCI reference clocks for the two PCI busses. A clock generator on the baseboard generates two 48MHz clocks (USB and SuperI/O), two 40MHz clocks (Wide and Narrow SCSI controllers), and three 14.318MHz clocks (PIIX4(e), Video, and ISA slot). Since the BMC runs off of 5V standby, the BMC has its own crystal providing a 22.1184MHz time reference. The baseboard also has a low skew clock buffer to distribute the PCI reference clock to all the embedded PCI devices and to all PCI slots. The baseboard also divides a host clock by 4 for five 25MHz APIC clocks (PROC4-PROC1 and PID). The following figure illustrates clock generation and distribution on the S450NX MP Server baseboard.

Figure 1.9: S450NX MP Server Baseboard Clock Distribution

#### 1.12.1 Real Time Clock, CMOS SRAM, and Battery

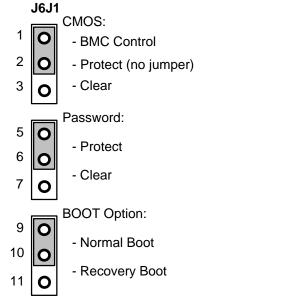

The real time clock supports 256 bytes of battery-packed CMOS SRAM in two banks that are reserved for BIOS use. The time, date and CMOS values can be specified in the Setup program. The CMOS values can be returned to their defaults by using the Setup program.

The recommended method of accessing the date with the baseboard is indirectly from the Real Time Clock (RTC) via the BIOS. The BIOS on the baseboard contains a century checking and maintenance feature that checks the least two significant digits of the year stored in the RTC during each BIOS request (INT 1Ah) to read the date and, if less than 80, updates the century byte to 20. This feature enables operating systems and applications using the BIOS date/time services to reliably manipulate the year as a four-digit value.

A coin-cell battery powers the real time clock and CMOS memory. When the system is not plugged into a wall socket, the battery has an estimated life of three years. When the system is plugged in, the 3.3V standby current from the power supply extends the life of the battery. The clock is accurate to +/-13 minutes/year at 25 °C with 3.3V applied.

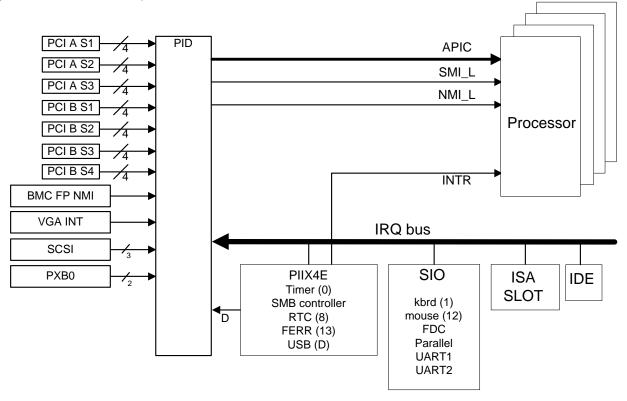

### 1.13 Interrupts and the PID

The S450NX MP Server interrupt architecture accommodates both PC-compatible PIC mode, and APIC mode interrupts through use of the Programmable Interrupt Device (PID).

#### 1.13.1 PIIX4(e) Compatibility Interrupt Controller

For PC-compatible mode, the PIIX4(e) provides two 82C59-compatible interrupt controllers embedded in the device. The two controllers are cascaded with interrupt levels 8-15 entering on level 2 of the primary interrupt controller (standard PC configuration). A single interrupt signal is presented to the processors, to which only one processor will respond for servicing. The PIIX4(e) and 87309VUL contain configuration registers that define which interrupt source logically maps to I/O APIC INTx pins.

#### 1.13.2 Intel PID

For APIC mode, the S450NX MP Server interrupt architecture incorporates the Intel PID device, to manage and broadcast interrupts to local APICs in each processor. The PID monitors each interrupt on

each PCI device including PCI slots in addition to the compatible interrupts IRQ(0-15), and on occurrence of an interrupt sends a message corresponding to the interrupt across a three wire serial interface to the local APICs. The APIC bus minimizes interrupt latency time for compatibility interrupt sources. The PID can also supply greater than 16 interrupt levels to the processor(s). This APIC bus consists of an APIC clock, and two bi-directional data lines. The PXB1 expansion slot has reserved signals for four PCI interrupts.

Figure 1.10: S450NX MP Server Baseboard Interrupt Diagram

#### 1.13.3 Interrupt Routing

Interrupts, both PCI and IRQ types, are handled by the PID. The PID then translates these to the APIC bus.

#### 1.13.4 Interrupt Sources

The following table recommends the logical interrupt mapping of interrupt sources on the S450NX MP Server baseboard. The actual interrupt map is defined using configuration registers in the PIIX4(e) and the PID.

| Interrupt | I/O APIC level | Description                                                                                                               |  |

|-----------|----------------|---------------------------------------------------------------------------------------------------------------------------|--|

| INTR      | INT0           | Processor interrupt.                                                                                                      |  |

| NMI       |                | NMI from PID to processor.                                                                                                |  |

| IRQ1      | INT1           | Keyboard interrupt.                                                                                                       |  |

| Cascade   | INT2           | Interrupt signal from second 8259 in PIIX4(e).                                                                            |  |

| IRQ3      | INT3           | Serial port A or B interrupt from SIO device, user-configurable.                                                          |  |

| IRQ4      | INT4           | Serial port A or B interrupt from SIO device, user-configurable.                                                          |  |

| IRQ5      | INT5           | Parallel port.                                                                                                            |  |

| IRQ6      | INT6           | Floppy disk.                                                                                                              |  |