# **Technical Information Manual**

IBM IntelliStation E Pro

**Professional Workstation (Type 6893)**

## **Technical Information Manual**

IBM IntelliStation E Pro

**Professional Workstation (Type 6893)**

Before using this information and the product it supports, be sure to read the general information under Appendix E, "Notices and Trademarks" on page 67.

#### Second Edition (September 1998)

The following paragraph does not apply to the United Kingdom or any country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time.

This publication was developed for products and services offered in the United States of America. IBM may not offer the products, services, or features discussed in this document in other countries, and the information is subject to change without notice. Consult your local IBM representative for information on the products, services, and features available in your area.

Requests for technical information about IBM products should be made to your IBM reseller or IBM marketing representative.

© Copyright International Business Machines Corporation September 1998. All rights reserved.

Note to U.S. Government Users — Documentation related to restricted rights — Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

# Contents

| Preface                                       | <b>v</b> i     |

|-----------------------------------------------|----------------|

| Manual Style                                  | <b>v</b> i     |

| Related Publications                          | <b>vi</b> i    |

|                                               |                |

| Chapter 1. System Overview                    | ′              |

| Hardware Features                             | ′              |

| Software Features                             |                |

| Wake on LAN                                   |                |

| Wake Up on Ring                               |                |

| Alert on LAN                                  |                |

| Asset ID                                      |                |

| Network Enablement                            |                |

| Operating System Support                      |                |

| Euro Sign Support Information                 |                |

|                                               |                |

| Chapter 2. System Board Features              | į              |

| Microprocessor                                |                |

| Pentium II Microprocessor with MMX Technology |                |

| Chip Set Control                              |                |

| L2 Cache                                      |                |

| System Memory                                 |                |

| Memory DIMM Options                           |                |

| PCI Bus                                       |                |

| IDE Bus Master Interface                      |                |

|                                               |                |

| PCI-to-ISA Bridge                             |                |

| USB Interface                                 |                |

| Video Subsystem                               |                |

| Matrox Millennium G200 AGP Graphics Adapter   |                |

| Matrox Millennium II AGP Graphics Adapter     |                |

| STB Glyder MAX-2+ AGP Graphics Adapter        |                |

| Audio                                         |                |

| Input/Output Controller                       |                |

| Diskette Drive Interface                      |                |

| Serial Ports                                  |                |

| Parallel Port                                 |                |

| Keyboard and Mouse Ports                      |                |

| IntelliStation E Pro Network Connection       |                |

| Real-Time Clock and CMOS                      | 14             |

| Flash EEPROM                                  | 15             |

| Riser Card                                    | 15             |

| Physical Layout                               |                |

| System Board, Type 6893                       | 16             |

| System Board Switches                         | 16             |

| Clear CMOS Request Jumper                     | 18             |

| Riser Card                                    |                |

| Connector Panel                               |                |

|                                               |                |

| Chapter 3. Physical Specifications            | 2 <sup>,</sup> |

| SCSI Adapter                                  |                |

| Cabling Requirements for Wake on LAN Adapters |                |

| <del>-</del> ·                                |                |

| Chapter 4. Power Supply  Power Input  Power Output  Component Outputs  Output Protection  Connector Description | 23<br>23<br>24<br>25 |

|-----------------------------------------------------------------------------------------------------------------|----------------------|

| Chapter 5. System Software  BIOS  Plug and Play                                                                 | 26                   |

| POST Configuration/Setup Utility Program                                                                        | 26                   |

| Advanced Power Management (APM) Advanced Configuration and Power Interface (ACPI)                               | 27                   |

| Flash Update Utility Program                                                                                    |                      |

| Chapter 6. IBM System Management Tools                                                                          |                      |

| DMI Service Provider                                                                                            |                      |

| DM BIOS Instrumentation                                                                                         |                      |

| IBM PC System Monitor                                                                                           |                      |

| IBM AssetCare                                                                                                   |                      |

| IBM Alert On LAN                                                                                                |                      |

| IBM SMART Reaction Client                                                                                       |                      |

| SMART Reaction                                                                                                  |                      |

| IBM SMART Reaction                                                                                              |                      |

| How SMART Reaction Responds to a Potential Problem                                                              |                      |

| SMART Reaction Restore Process                                                                                  |                      |

| Critical Data Mirroring                                                                                         |                      |

| Intel LANDesk Client Manager                                                                                    |                      |

| Advanced Configuration and Power Interfaces (ACPI)                                                              |                      |

| Wake on LAN                                                                                                     |                      |

| Wake on LAN components                                                                                          |                      |

| How Wake on LAN works                                                                                           | 41                   |

| Definition of the Wake-up Frame                                                                                 | 41                   |

| Give your IntelliStations a wake-up call                                                                        | 42                   |

| IBM LANClient Control Manager version 2.0 (LCCM)                                                                | 42                   |

| System Deployment                                                                                               |                      |

| Flashing the CMOS or BIOS                                                                                       | 44                   |

| Installing Software                                                                                             |                      |

| LCCM New Client Scenario                                                                                        |                      |

| Low-level Management                                                                                            | 45                   |

| Chapter 7. System Compatibility                                                                                 | 46                   |

| Hardware Compatibility                                                                                          |                      |

| Hardware Interrupts                                                                                             | 47                   |

| Diskette Drives and Controller                                                                                  | 48                   |

| Hard Disk Drives and Controller                                                                                 | 49                   |

| Software Compatibility                                                                                          |                      |

| Software Interrupts                                                                                             | 49                   |

| Machine-Sensitive Programs                                                                                      | 49                   |

| Appendix A. Connector Pin Assignments                                                                           | 50                   |

| Memory Connectors                            | <br>. 50 |

|----------------------------------------------|----------|

| ISA Connectors                               | <br>. 52 |

| PCI Connectors                               | <br>. 53 |

| IDE Connectors                               | <br>. 55 |

| Diskette Drive Connector                     |          |

| Power Supply Connector                       |          |

| Modem/Ring Wakeup and Wake on LAN Connectors | <br>. 57 |

| Alert on LAN Connector                       | <br>. 57 |

| RFID Connector (Asset ID)                    | <br>. 57 |

| Fan Connector                                | <br>. 58 |

| USB Port Connectors                          |          |

| Mouse and Keyboard Port Connectors           | <br>. 58 |

| Serial Port Connectors                       | <br>. 59 |

| Parallel Port Connector                      | <br>. 59 |

| Monitor Port Connector                       | <br>. 60 |

| Ethernet Connector                           | <br>. 60 |

| Appendix B. System Address Maps              | 61       |

| System Memory Map                            |          |

| Input/Output Address Map                     |          |

| DMA I/O Address Map                          |          |

| PCI Configuration Space Map                  |          |

| r Ci Configuration Space Map                 | <br>. 04 |

| Appendix C. IRQ and DMA Channel Assignments  | <br>. 65 |

|                                              |          |

| Appendix D. Error Codes                      | <br>. 66 |

| POST Error Codes                             | <br>. 66 |

| Beep Codes                                   | <br>. 66 |

| Appendix E. Notices and Trademarks           | 67       |

| Year 2000 Readiness and Instructions         |          |

|                                              | <br>,    |

| References                                   | <br>. 69 |

|                                              |          |

| Index                                        | <br>. 70 |

# Figures

| 1.                   | Memory Configurations                                                  | 7  |

|----------------------|------------------------------------------------------------------------|----|

| 1.<br>2.             | Serial Port Assignments                                                |    |

| 2.<br>3.             | Parallel Port Assignments                                              |    |

| 3.<br>4.             | Riser Card Characteristics                                             |    |

| <del>4</del> .<br>5. | Microprocessor Speed (Switches 1-4)                                    |    |

| 5.<br>6.             | ROM Recovery (Switch 5)                                                |    |

| 7.                   | System Board Ethernet Control (Switch 6)                               |    |

| 7.<br>8.             | Privileged Access Password Control (Switch 7)                          |    |

| 9.                   | Diskette Drive Device Access (Switch 8)                                |    |

| 9.<br>10.            | Clear CMOS Request Jumper (J9)                                         |    |

| 11.                  | Power Input Requirements                                               |    |

| 12.                  | Power Output (145 Watt)                                                |    |

| 12.<br>13.           | System Board                                                           |    |

| 13.<br>14.           | Keyboard Port                                                          |    |

| 15.                  | Auxiliary Device Port                                                  |    |

| 15.<br>16.           | ISA-Bus Adapters (Per Slot)                                            |    |

| 10.<br>17.           | PCI-Bus Adapters (Per Slot) either/or                                  |    |

| 17.<br>18.           | USB Port                                                               |    |

| 10.<br>19.           | Internal SCSI Drives                                                   |    |

| 19.<br>20.           | Enhanced Asset Information Area                                        |    |

| 20.<br>21.           | Device Types                                                           |    |

| 21.<br>22.           | Serialization Information Area Header                                  |    |

| 22.<br>23.           | User Information Area Header                                           |    |

| 23.<br>24.           | Configuration Information Area Header                                  |    |

| 24.<br>25.           | 5.25-Inch Diskette Drive Reading, Writing, and Formatting Capabilities |    |

| ∠5.<br>26.           | 3.5-Inch Diskette Drive Reading, Writing, and Formatting Capabilities  |    |

|                      | System Memory Connector Pin Assignments                                |    |

| 27.<br>28.           | ISA Connector Pin Assignments                                          |    |

| ∠8.<br>29.           | PCI Bus Connector                                                      |    |

|                      |                                                                        |    |

| 30.<br>31.           | PCI Connector Pin Assignments                                          |    |

|                      | IDE Connector Pin Assignments                                          |    |

| 32.                  | Diskette Drive Connector Pin Assignments                               |    |

| 33.                  |                                                                        |    |

| 34.                  | J13 Modem/Ring Wakeup Connector Pin Assignments                        |    |

| 35.                  |                                                                        |    |

| 36.<br>27            | J12 Alert on LAN Connector Pin Assignments                             |    |

| 37.                  | J5 Asset ID Connector Pin Assignments                                  |    |

| 38.<br>20            | J14 Front Fan Connector Pin Assignments                                |    |

| 39.<br>40            | USB Port Connector Pin Assignments                                     |    |

| 40.                  | Mouse and Keyboard Port Connector Pin Assignments                      |    |

| 41.                  | Serial Port Connectors Pin Assignments                                 |    |

| 42.                  | Parallel Port Connector Pin Assignments                                |    |

| 43.                  | Monitor Connector Pin Assignments                                      |    |

| 44.<br>45            | Ethernet Connector                                                     |    |

| 45.                  | Pin Assignments for the Ethernet Connector                             |    |

| 46.                  | System Memory Map                                                      |    |

| 47.                  | I/O Address Map                                                        |    |

| 48.                  | DMA I/O Address Map                                                    |    |

| <b>4</b> 9.          | IRQ Channel Assignments                                                |    |

| 50.                  | DMA Channel Assignments                                                | 65 |

## **Preface**

This publication provides information for the IBM IntelliStation E Pro. It is intended for developers who want to provide hardware and software products to operate with this computer. It offers the details of how the computer works. Users of this publication should have an understanding of computer architecture and programming concepts.

### **Manual Style**

In this manual, some signals are represented in a small, all-capital-letter format (-ACK). A minus sign in front of the signal indicates that the signal is active low. No sign in front of the signal indicates that the signal is active high.

The use of the term *hex* indicates a hexadecimal number. Also, when numerical modifiers such as "K", "M" and "G" are used, they typically indicate powers of 2, not powers of 10. For example, 1 KB equals 1024 bytes (2¹0), 1 MB equals 1048 576 bytes (2²0), and 1 GB equals 1073 741 824 bytes (2³0).

When expressing storage capacity, MB equals 1 000 KB (1 024 000). The value is determined by counting the number of sectors and assuming that every two sectors equals 1 KB.

**Note:** Depending on the operating system and other system requirements, the storage capacity available to the user might vary.

**Attention!** The term *reserved* describes certain signals, bits, and registers that should not be changed. Use of reserved areas can cause compatibility problems, loss of data, or permanent damage to the hardware. When the contents of a register are changed, the state of the reserved bits must be preserved. When possible, read the register first and change only the bits that must be changed.

#### **Related Publications**

In addition to this manual, the following IBM publications provide information related to the operation of the IBM IntelliStation E Pro. To order publications in the U.S. and Puerto Rico, call 1-800-879-2755. In other countries, contact an IBM reseller or an IBM marketing representative.

#### IntelliStation E Pro User Guide

This hardcopy publication comes with your computer and is also available on the Ready-to-Configure Utility Program CD that comes with your computer. It contains information on setting up, configuring, operating, and maintaining your computer. Also included are warranty information, instructions for diagnosing and solving problems, and information on how to obtain help and service.

#### Installing Options in Your IntelliStation E Pro

This publication contains instructions for installing options in the computer. It is available in Adobe® .PDF format on the Ready-to-Configure Utility Program CD that comes with your computer as well as on the World Wide Web at:

http://www.pc.ibm.com/support

#### Understanding Your IntelliStation E pro

This online document, available on the Ready-to-Configure Utility Program CD that comes with your computer, includes general information about using computers and detailed information about the features of the IntelliStation E Pro.

#### · About Your Software

This publication (provided only with computers that have IBM-preinstalled software) contains information about the preinstalled software package.

#### Hardware Maintenance Manual

This publication contains information for trained service technicians. It is available on the World Wide Web at:

http://www.pc.ibm.com/support

It can also be ordered from IBM. To purchase a copy, refer to the "Getting Help, Service, and Information" section in the IntelliStation E Pro User Guide.

#### Advanced Management Documentation

These publications contain information for network administrators who configure and service local area networks (LANs). It is available on the World Wide Web at :

http://www.pc.ibm.com/us/ibmpc/tech library.html

#### Adaptec SCSI Documentation

These publications are provided with computer models that have an IBM-installed SCSI adapter. They include information on configuring the SCSI adapter and instructions for installing and configuring SCSI devices. Look for these publications on the Ready-to-Configure Utility Program CD that comes with your computer.

## **Chapter 1. System Overview**

The IntelliStation E Pro is a versatile product designed to provide state-of-the-art computing power with room for future growth.

#### **Hardware Features**

The major features are:

- An Intel® Pentium® II microprocessor with MMX™ technology and 100 MHz Front Side Bus (FSB) and 512 KB of L2 cache with ECC

- Up to 768 MB of SDRAM system memory with ECC

- Integrated IDE bus master controller, ultra DMA/33 capable

- Preinstalled Adaptec Ultra Wide SCSI adapter (on some models)

- SCSI hard disk drive (on models with the Adaptec adapter)

- EIDE hard disk drive, 7200 rpm (on some models)

- System management

- Wake on LAN support

- Alert on LAN support

- DMI (Desktop Management Interface) BIOS and DMI software

- System management controller

- Integrated network protocols

- Enablement for remote administration

- Asset ID support

- IBM System Management Tools

- 32X Max IDE CD-ROM drive1

- · Asset security

- Security settings provided by the Configuration/Setup Utility Program

- Power-on and administrator password protection

- Startup-sequence control

- Hard disk drive and diskette drive access control

- I/O port control

- Enhanced security for administrator password and startup sequence

- Chassis-intrusion detector

- Cover lock

- U-bolt and security cabling (optional)

- Operating system security

- Diskette write-protection

<sup>1</sup> Variable read rate. Actual playback speed will vary and is often less than the maximum possible.

#### Chapter 1. System Overview

- · Video adapter

- Matrox Millennium G200 AGP Graphics Adapter (some models only)

- Matrox Millennium II AGP Graphics Adapter (some models only)

- STB Glyder MAX-2+ AGP Graphics Adapter (some models only)

- Integrated 16-bit, stereo audio controller and built-in high quality speaker (supports SoundBlaster, Adlib, and Microsoft Windows Sound System applications)

- · Integrated Ethernet controller and connector with Wake on LAN

- Token Ring Adapter

- IBM PCI Token-Ring adapter with Wake on LAN is optional

- Expansion

- Four drive bays, four expansion slots (one ISA, two PCI, and one shared ISA/PCI)

- AGP expansion slot, used for graphics adapter

- ISA/PCI I/O-bus compatibility

- Industry-standard compatibility

- EnergyStar compliance

- 3.5-inch, 1.44 MB diskette drive

- Input/Output Features

- One 25-pin, ECP/EPP parallel port

- Two 9-pin, UART serial ports

- Two 4-pin, USB ports

- One 6-pin, keyboard port

- One 6-pin, mouse port

- One 15-pin, DDC2B-compliant monitor port

- Three 3.5 mm audio jacks (line out, line in, microphone)

#### **Software Features**

The following features are supported by the IBM IntelliStation E Pro.

#### Wake on LAN

The power supply of the computer supports the Wake on LAN feature. With the Wake on LAN feature, the computer can be turned on when a specific LAN frame is passed to the PC over the LAN.

To use the Wake on LAN feature, the computer must be equipped with a network subsystem that supports Wake on LAN.

The menu used for setting the Wake on LAN feature is found in the Configuration/Setup Utility Program.

### Wake Up on Ring

All models are configurable to turn on the computer after a ring is detected from an external or internal modem. The menu used for setting the Wake Up on Ring feature is found in the Configuration/Setup Utility Program. Two options control this feature:

- **Serial Ring Detect:** Use this option if the computer has an external modem connected to the serial port.

- Modem Ring Detect: Use this option if the computer has an internal modem.

#### Alert on LAN

The IntelliStation E Pro features Alert on LAN, a product of the IBM/Intel Advanced Manageability Alliance. Alert on LAN can notify you when a system has been tampered with or removed from the network. This new feature is part of the IBM AssetCare, which also includes other innovations such as SMART Reaction data protection software.

#### Asset ID

The Asset ID feature uses radio-frequency technology to read and write an EEPROM inside your computer. The radio-frequency interface includes an Asset ID antenna inside the computer that enables communications between industry-standard radio-frequency devices and your computer EEPROM. The information in the EEPROM includes configuration data and serial numbers of key components. There are also blank fields that can be recorded with the users choice of information. This information can be used to track the movement of the computer for inventory and security purposes. The menu used for enabling the Asset ID feature is found in the Configuration/Setup Utility Program. For more information about Asset ID information, see "IBM AssetCare" on page 30 and "Asset ID" on page 35.

#### **Network Enablement**

The IntelliStation E Pro is enabled to support management over a network. The following is a list of functions that are supported:

- · Selectable startup sequence

- Selectable Automatic Power On Startup Sequence

- Update POST/BIOS from network

- · Wake on LAN

- · CMOS Save/Restore utility program

- · CMOS setup over LAN

- Alert on LAN

- · Wake Up on Ring

### **Operating System Support**

Although a variety of operating systems can be used with IntelliStation E Pro computers, full function is provided only with Windows NT 4.0. (Some models also fully support Windows 95, Windows 98, and Windows NT 3.5.) When operating systems other than these are used, the IntelliStation E Pro will work, but without all of the advanced functions For a list of operating systems that are compatible with the IntelliStation E Pro, refer to the *About Your Software* and the IBM online compatibility report on the World Wide Web at http://www.pc.ibm.com/us/intellistation/tech\_library.html.

**Note:** Windows NT 4.0 and various support programs are preinstalled in some IntelliStation E Pro computers. Refer to *About Your Software* for a detailed description of the preinstallation package. Also, a *Ready-to-Configure Utility Program CD* is included with all models. The *Ready-to-Configure Utility Program CD* contains applications and device driver support for the preinstalled operating system (if applicable), and several other operating systems.

## **Euro Sign Support Information**

The *Euro Sign* is the name given to the proposed currency symbol of the European Union. According to the European Commission, the Euro will exist as a currency beginning 1 January 1999, but will only gradually move into general use with the introduction of coins and notes in 2002.

IBM and various other personal computer industry companies plan to support the Euro Sign on products released in 1999. For support information on products released prior to that date, see the appropriate Web site for your product.

For your computer to support the Euro Sign, a proper combination of both hardware (computer, keyboard, and printer) and software (operating systems, application programs, and device drivers) is required.

There are many Web sites that provide Euro Sign information and support (some are listed below). First, determine the computer hardware and software you are using. Then, visit the Web sites that apply to your system for the latest Euro Sign information and support. In many cases, updates are available for Euro Sign support. These updates can be downloaded and installed on your computer.

- http://www.adobe.com

- http://www.ibm.com

- http://www.microsoft.com/europe/euro

(The "euro product update" is available for Windows 95 and Window NT)

## **Chapter 2. System Board Features**

This section includes information about system board features. For an illustration of the system board, see "System Board, Type 6893" on page 16.

### Microprocessor

The IntelliStation E Pro comes with an Intel Pentium II microprocessor with MMX technology. The microprocessor, which has a heat sink attached, plugs directly into a connector on the system board. For information on replacing a microprocessor or installing an upgrade, refer to *Installing Options in Your IntelliStation E Pro.*

## Pentium II Microprocessor with MMX Technology

The features of this microprocessor are as follows:

- · Optimization for 32-bit software

- · Operation at a lower voltage level than previous microprocessors

- 64-bit microprocessor data bus

- 100 MHz FSB

- 512 KB L2 cache with ECC

- 32-bit microprocessor address bus

- · Math coprocessor

- · MMX technology, which boosts the processing of graphic, video, and audio data

- L2 cache integrated into the microprocessor

- 4-way set associative

- Nonblocking

- 50-percent processor speed performance increase over placement of L2 cache on the system board

More information on these microprocessors is available at http://www.intel.com on the World Wide Web.

## **Chip Set Control**

Two components, the Intel 440BX and PIIX4E, make up the chip set that is the interface between the microprocessor and the following:

- · Memory subsystem

- PCI bus

- · Busmaster IDE connection

- High-performance, PCI-to-ISA bridge

- USB ports

- SMBus

- AGP bus

- · Enhanced DMA controller

- RTC

#### L2 Cache

The IntelliStation E Pro computer is equipped with a Pentium II microprocessor with MMX technology and 512 KB of L2 cache. The L2 cache ECC function is automatically enabled when ECC memory is installed. If nonparity memory is installed, the L2 cache ECC is disabled. (For information on overriding these settings, refer to Configuration/Setup Utility Program in the *IntelliStation E Pro User Guide*.)

### **System Memory**

The system memory interface is controlled by the 440BX chip set. Synchronous dynamic random access memory (SDRAM) is standard.

The maximum amount of system memory is 768 MB. For memory expansion, the system board provides three dual inline memory module (DIMM) connectors. DIMM sizes of 16MB, 32MB, 64MB, 128MB, and 256MB with a speed of 100 MHz are supported. The amount of memory preinstalled varies by model.

## **Memory DIMM Options**

#### Important

Be sure to observe the following guidelines when adding memory DIMM options to your computer.

- The IntelliStation E Pro does not support EDO memory.

- Only 168-pin, 100 MHz, 3.3v industry standard memory DIMMs are supported.

- There are two types of memory DIMMs available for the IntelliStation E Pro computer: Registered Memory technology and Unregistered Memory technology.

- Registered Memory DIMMs are not compatible with Unregistered Memory DIMMs.

- The 256 MB ECC Memory DIMM is Registered Memory technology.

- Only the 256 MB ECC Registered Memory DIMM (IBM OBI Part Number 01K1132) is supported on the IntelliStation E Pro computer.

- The 16 MB, 32 MB, 64 MB, and 128 MB DIMMs are *Unregistered Memory* technology.

- When adding additional memory DIMMs, be sure that all installed memory DIMMs are of the same type. For example:

- All installed DIMMs are Registered Memory

- or -

- All installed DIMMs are Unregistered Memory

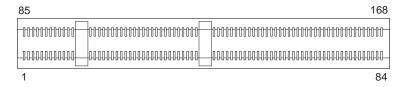

For information on the pin assignments for the memory module connectors, see "Memory Connectors" on page 50.

The following figure shows some possible configurations for the supported DIMMs.

**Note:** Values in the following table are represented in megabytes (MB).

| Total Memory (MB) | Mem 0 | Mem 1 | Mem2 |

|-------------------|-------|-------|------|

| 16                | 16    | 0     | 0    |

| 32                | 16    | 16    | 0    |

| 32                | 32    | 0     | 0    |

| 48                | 16    | 16    | 16   |

| 48                | 32    | 16    | 0    |

| 64                | 32    | 16    | 16   |

| 64                | 32    | 32    | 0    |

| 64                | 64    | 0     | 0    |

| 96                | 32    | 32    | 32   |

| 96                | 64    | 32    | 0    |

| 128               | 64    | 32    | 32   |

| 128               | 64    | 64    | 0    |

| 128               | 128   | 0     | 0    |

| 160               | 32    | 64    | 64   |

| 192               | 64    | 64    | 64   |

| 224               | 32    | 64    | 128  |

| 256               | 256   | 0     | 0    |

| 256               | 128   | 64    | 64   |

| 256               | 128   | 128   | 0    |

| 288               | 32    | 128   | 128  |

| 384               | 128   | 128   | 128  |

| 768               | 256   | 256   | 256  |

#### **PCI Bus**

The fully synchronous 33 MHz PCI bus originates in the chip set. Features of the PCI bus are:

- Integrated arbiter with multi-transaction PCI arbitration acceleration hooks for high performance graphics

- Built-in PCI bus arbiter with support for up to five masters

- Microprocessor-to-PCI memory write posting with 5-Dword-deep buffers

- · Converts back-to-back sequential microprocessor-to-PCI memory write to PCI burst write

- PCI-to-DRAM posting 18 Dwords

- PCI-to-DRAM up to 100+ MB/sec bandwidth

- · Multitransaction timer to support multiple short PCI transactions within one PCI ARB cycle

- PCI 2.1 compliant

- Delayed transaction

- · PCI parity checking and generation support

#### **IDE Bus Master Interface**

The system board incorporates a PCI-to-IDE interface that complies with the *AT Attachment Interface with Extensions*.

The Intel PIIX4E functions as a *bus master* for the IDE interface. The chip set is PCI 2.1 compliant; it connects directly to the PCI bus and is designed to allow concurrent operations on the PCI bus and IDE

#### **Chapter 2. System-Board Features**

bus. The chip set is capable of supporting PIO mode 0–4 devices and IDE DMA mode 0–2 devices, ultra DMA 33 transfers up to 33 Mbytes/sec.

The IDE devices receive their power through a four-position power cable containing +5 V dc, +12 V dc, and ground. When adding devices to the IDE interface, one device is designated as the master device and another is designated as the slave or subordinate device. These designations are determined by switches or jumpers on each device. There are two IDE ports, one designated 'Primary' and the other 'Secondary,' allowing for up to four devices to be attached. The total number of physical IDE devices is dependent on the mechanical package.

For the IDE interface, no resource assignments are given in the system memory or the direct memory access (DMA) channels. For information on the resource assignments, see "Input/Output Address Map" on page 61 and Figure 49 on page 65 (for IRQ assignments).

Two connectors are provided on the riser for the IDE interface. For information on the connector pin assignments, see "IDE Connectors" on page 55.

### **PCI-to-ISA Bridge**

On the system board, the Intel PIIX4E provides the interface between the peripheral component interface (PCI) and industry standard architecture (ISA) buses. The chip set is used to convert PCI bus cycles to ISA bus cycles; the chip set also includes all the subsystems of the ISA bus, including two cascaded interrupt controllers, two DMA controllers with four 8-bit and three 16-bit channels, three counters equivalent to a programmable interval timer, and power management. The PCI bus operates at 33 MHz. The ISA bus operates at 8.25 MHz.

For the ISA bus, no resource assignments are given in the system memory or the DMA channels. For information on resource assignments, see "Input/Output Address Map" on page 61 and Figure 49 on page 65 (for IRQ assignments).

#### **USB** Interface

Universal serial bus (USB) technology is a standard feature of the computer. Using the chip set, the system board provides the USB interface with two connectors. A USB-enabled device can attach to each connector, and if that device is a hub, multiple peripherals can attach to the hub and be used by the system. The USB connectors use Plug and Play technology for installed devices. The speed of the USB is up to 12 MB/sec with a maximum of 127 peripherals. The USB is compliant with Universal Host Controller Interface Guide 1.0.

Features provided by USB technology include:

- Support for hot pluggable devices

- Support for concurrent operation of multiple devices

- · Suitable for different device bandwidths

- Support for up to five meters length from host to hub or from hub to hub

- Guaranteed bandwidth and low latencies appropriate for specific devices

- · Wide range of packet sizes

- · Limited power to hubs

For information on the connector pin assignments for the USB interface, see "USB Port Connectors" on page 58.

## **Video Subsystem**

The video subsystem on the system board includes one of the following:

- Matrox Millennium G200 AGP Graphics Adapter

- Matrox Millennium II AGP Graphics Adapter

- STB Glyder MAX-2+ AGP Graphics Adapter

## Matrox Millennium G200 AGP Graphics Adapter

The Matrox Millennium G200 AGP Graphics Adapter supports all video graphics array (VGA) modes and is compliant with super video graphics array (SVGA) modes and Video Electronics Standards Association (VESA) 1.2. Some enhanced features are:

- On board memory: 8 MB SGRAM standard, upgradable to 16 MB

- 250 MHz RAMDAC

- MGA-G200 128-bit DualBus graphics chip

- · Advanced 2D, 3D and software DVD video acceleration

- High Quality 3D rendering engine

For information on resource assignments, see Appendix B, "System Address Maps" on page 61 and Appendix C, "IRQ and DMA Channel Assignments" on page 65.

### Matrox Millennium II AGP Graphics Adapter

The Matrox Millennium II AGP Graphics Adapter supports all video graphics array (VGA) modes and is compliant with super video graphics array (SVGA) modes and Video Electronics Standards Association (VESA) 1.2. Some enhanced features are:

- Dual ported on board WRAM memory: 8 MB SGRAM standard, upgradable to 16 MB

- 250 MHz RAMDAC

- 2D resolutions True color (16.7M colors)

- 1920 X 1200 True color

For information on resource assignments, see Appendix B, "System Address Maps" on page 61 and Appendix C, "IRQ and DMA Channel Assignments" on page 65.

## STB Glyder MAX-2+ AGP Graphics Adapter

The STB Glyder MAX-2+ AGP Graphics Adapter supports all video graphics array (VGA) modes and is compliant with super video graphics array (SVGA) modes and Video Electronics Standards Association (VESA) 1.2. Some enhanced features are:

- · 66 MHz AGP-2 based graphics accelerator

- Pipelined command queing

- Side banding

- DMA and Execute modes compact.

- 8 MB flexible multifunction memory

- 230 MHz RAMDAC

- 2D Resolutions True Color (16.7M colors)

- 1280 x 1024 @85 Hz

- max resolution: 1600 x 768 @ 85 Hz

- 3D Resolutions by color depth

#### Chapter 2. System-Board Features

#### compact.

- True color (up to): 1280 X 1024 -- 16 bit Z, .5 MB texture

- 8 bit color (64K colors): 1600 x 1200 -- 16 bit Z, .5 MB texture

- Business Graphics Winmark: 221

- CDRS: 27.07 with 400 MHz

- 3D Features

- Triangle setup engine

- Color dithering

- Double buffering

- Z-buffer (16-bit)

- Fogging (fade to white)

- Depth cueing (fade to black)

- Hardware Zoom

- Gouraud shading

- Bilinear MIP mapping

- True Alpha blinding

- Video textures

- Perspective correction

- Bilinear filtering

- Palletized Textures

- Onchip texture cache (1K)

- Texture Bus Mastering

#### **Audio**

All models come with integrated audio. Some models come with a Crystal audio adapter. These models, which are capable of playing and recording sounds, support SoundBlaster, Adlib, and Microsoft Windows Sound System applications. The audio adapter in these models has a 4237B Crystal audio chip with integrated SRS 3D sound technology that supports FM synthesis.

The device drivers for the preinstalled audio adapter are on the hard disk drive. The device drivers are also available on the *Ready-to-Configure* CD provided with all models.

If you connect an optional device to the audio adapter, follow the instructions provided by the manufacturer. (Note that device drivers might be required. If necessary, contact the manufacturer for information on these device drivers.)

The following ports are available on the integrated audio controller:

- Line Out port for connecting powered speakers. Your audio system requires a set of speakers connected to the Line Out port in order to hear audio from the adapter. These speakers must be powered with a built-in amplifier. In general, any powered speakers designed for use with personal computers can be used with your audio adapter. These speakers are available with a wide range of features and power outputs.

- Line In port for connecting musical devices, such as a portable CD-ROM or stereo.

- *Microphone* for connecting a microphone.

<sup>2</sup> An electronic device connected to the Game/MIDI port might require an optional adapter cable. For more information, refer to the documentation that comes with the electronic device.

## **Input/Output Controller**

Control of the integrated input/output (I/O) and diskette drive controllers is provided by a single module, the SMC 37C673. This module, which supports Plug and Play, controls the following features:

- · Diskette drive interface

- Serial port

- Parallel port

- · Keyboard and mouse ports

- · General purpose I/O ports

#### **Diskette Drive Interface**

The IntelliStation E Pro has four drive bays for installing internal devices. The following is a list of devices that the diskette drive subsystem supports:

- 1.44 MB, 3.5 inch diskette drive

- 1.44 MB, 3.5 inch, 3-mode drive for Japan

- 1.2 MB, 5.25 inch diskette drive

- 1 Mbps, 500 Kbps, or 250 Kbps internal tape drive

One connector is provided on the system board for diskette drive support. For information on the connector pin assignments, see "Diskette Drive Connector" on page 56.

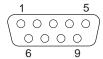

#### **Serial Ports**

Integrated into the system board are two universal asynchronous receiver/transmitter (UART) serial ports. The serial ports include a 16-byte data, first-in first-out (FIFO) buffer, and have programmable baud rate generators. The serial ports are NS16450 and PC16550A compatible.

For information on the connector pin assignments, see "Serial Port Connectors" on page 59.

Note: Current loop interface is not supported.

The following figure shows the serial port assignments used in configuration.

| Figure 2. Serial Port Assignments |                     |           |  |  |

|-----------------------------------|---------------------|-----------|--|--|

| Port Assignment                   | Address Range (hex) | IRQ Level |  |  |

| Serial 1                          | 03F8-03FF           | IRQ4      |  |  |

| Serial 2                          | 02F8-02FF           | IRQ3      |  |  |

| Serial 3                          | 03E8-03FF           | IRQ4      |  |  |

| Serial 4                          | 02E8-02FF           | IRQ3      |  |  |

The default setting for serial port is COM1.

#### **Parallel Port**

Integrated in the system board is support for extended capabilities port (ECP), enhanced parallel port (EPP), and standard parallel port (SPP) modes. The modes of operation are selected through the Configuration/Setup Utility program with the default mode set to SPP. The ECP and EPP modes are compliant with IEEE 1284.

The following figure shows the parallel port assignments used in the configuration.

| Figure 3. Parallel Port Assignments |                     |           |  |  |

|-------------------------------------|---------------------|-----------|--|--|

| Port Assignment                     | Address Range (hex) | IRQ Level |  |  |

| Parallel 1                          | 03BC-03BE           | IRQ7      |  |  |

| Parallel 2                          | 0378-037F           | IRQ5      |  |  |

| Parallel 3                          | 0278-027F           | IRQ5      |  |  |

The default setting for the parallel port is Parallel 1.

The system board has one connector for the parallel port. For information on the connector pin assignments, see "Parallel Port Connector" on page 59.

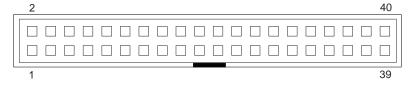

### **Keyboard and Mouse Ports**

The keyboard and mouse subsystem is controlled by a general purpose 8-bit microcontroller; it is compatible with 8042AH. The controller consists of 256 bytes of data memory and 2 KB of read-only memory (ROM).

The controller has two logical devices: one controls the keyboard and the other controls the mouse. The keyboard has two fixed I/O addresses and a fixed IRQ line and can operate without the mouse. The mouse cannot operate without the keyboard because, although it has a fixed IRQ line, the mouse relies on the addresses of the keyboard for operation. For the keyboard and mouse interfaces, no resource assignments are given in the system memory addresses or DMA channels. For information on the resource assignments, see "Input/Output Address Map" on page 61 and Figure 49 on page 65 (for IRQ assignments).

The system board has one connector for the keyboard port and one connector for the mouse port. For information on the connector pin assignments, see "Mouse and Keyboard Port Connectors" on page 58.

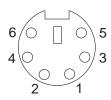

#### IntelliStation E Pro Network Connection

All IntelliStation E Pro models are equipped with an integrated Ethernet that supports the Wake on LAN feature.

Features of the integrated Ethernet adapter are:

- IEEE 802.3 compliance

- Operates in shared 10BASE-T or 100BASE-TX environment (auto-negotiation)

- Transmits and receives data at 10 Mbps or 100 Mbps

- RJ-45 connector for LAN attachment

- Operates in symmetrical multiprocessing (SMP) environments

- · Wake on LAN support

- Remote Program Load (RPL) and Dynamic Host Configuration Protocol (DHCP) support

- Alert on LAN support

- · Viewable MAC Address provided

- PCI 2.1 compliant bus master

Features of the optional Token-Ring adapter are:

- Transmits and receives data at 4 Mbps or 16 Mbps

- RJ-45 and D-shell connectors for LAN attachment

- · Wake on LAN support

- Remote Program Load (RPL) and Dynamic Host Configuration Protocol (DHCP) support

#### Chapter 2. System-Board Features

#### **Real-Time Clock and CMOS**

The real-time clock is a low-power clock that provides a time-of-day clock and a calendar. The clock settings are maintained by an external battery source of 3 V ac.

The system uses 242 bytes of memory to store complementary metal-oxide semiconductor (CMOS) memory. Moving a jumper on the system board erases CMOS memory.

To locate the battery, see "System Board, Type 6893" on page 16.

#### Flash EEPROM

The system board uses an 8 Mb flash electrically-erasable, programmable, read-only memory (EEPROM) to store system programs that include basic input/output system (BIOS), IBM logo, Configuration/Setup Utility, and Plug and Play data.

As part of the continuing work to improve quality, IBM might make changes and enhancements to the system programs. When updates are released, they will be available on the World Wide Web at

http://www.pc.ibm.com/us/intellistation

or through the PC Company Bulletin Board Service in files that can be downloaded onto a diskette. Instructions for using the system programs updates will be available in a README file included in the downloaded files.

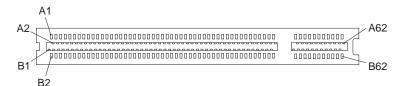

#### **Riser Card**

The system board uses a riser card to route PCI and ISA bus signals to the expansion connectors. Each ISA-expansion connector is 16 bits, and each PCI-expansion connector is 32 bits. PCI-expansion connectors support the 32 bit, 5 V dc, local-bus signalling environment that is defined in *PCI Local Bus Specification 2.1*. The ISA bus is buffered to provide sufficient drive for the ISA-expansion connectors, assuming two low-power Schottky (LS) loads per slot.

The system board uses a riser card. The following figure summarizes the characteristics of the two riser card.

| Figure 4. Riser Card Characteristics |                |  |  |  |

|--------------------------------------|----------------|--|--|--|

| Expansion Slots                      | 4x4 Riser Card |  |  |  |

| Shared ISA/PCI                       | 1*             |  |  |  |

| Dedicated ISA                        | 1*             |  |  |  |

| Dedicated PCI                        | 2              |  |  |  |

<sup>\*</sup> Indicates full size adapter slots.

For information on the connector pin assignments, see "ISA Connectors" on page 52 and "PCI Connectors" on page 53.

## **Physical Layout**

The system board might look slightly different from the one shown.

Note: A diagram of the system board, including switch and jumper settings, is attached to the underside of the computer cover.

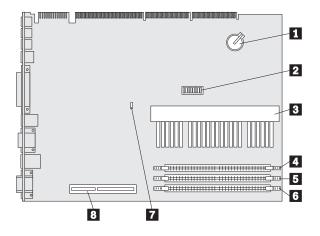

### System Board, Type 6893

Microprocessor-speed switches

Microprocessor

DIMM 0 DIMM 1

DIMM 2

Clear CMOS Request jumper

AGP connector

Note: An illustration of the system board and additional information are provided on a label found inside the computer.

# **System Board Switches**

Switches are provided on the system board to allow for custom configuration. The switches, which are contained in an eight-position switch block on the system board, are rocker switches. The side of the rocker that is pushed down is the active side.

Switches 1 through 4 determine the speed of the microprocessor (CPU) and local processor bus. Switch settings for the Intel microprocessors supported by IntelliStation E Pro are shown in the following table. Note that the two speeds shown for each microprocessor are the microprocessor core speed followed by the local processor bus speed (for example, 350/100 MHz).

| Figure 5. Microprocessor Speed (Switches 1-4) |          |          |          |          |

|-----------------------------------------------|----------|----------|----------|----------|

| Microprocessor                                | Switch 1 | Switch 2 | Switch 3 | Switch 4 |

| 350/100 MHz                                   | Off      | Off      | On       | On       |

| 400/100 MHz                                   | On       | On       | Off      | On       |

| 450/100 MHz                                   | Off      | On       | Off      | On       |

IntelliStation E Pro computers are designed to support 100MHz FSB microprocessors.

Note: Only the switch values shown in the preceding table are supported. Using unsupported switch settings will cause unpredictable results.

#### Switch 5 is ROM Recovery.

| Figure 6. ROM Recovery (Switch 5) |                       |  |

|-----------------------------------|-----------------------|--|

| Normal operation                  | Off (factory default) |  |

| ROM Recovery                      | On                    |  |

Switch 6 enables or disables the system board Ethernet. When the Ethernet disable switch is *On*, the system board Ethernet is disabled. This switch must be on when a Wake on LAN adapter is installed. (Note that only one Wake on LAN device can be used.)

| Figure 7. System Board Ethernet Control (Switch 6) |     |  |

|----------------------------------------------------|-----|--|

| Disable                                            | On  |  |

| Enable (factory default)                           | Off |  |

Switch 7 enables or disables the privileged access password (PAP). Note that this password is also referred to as the *administrator password*. Refer to the *IntelliStation E Pro User Guide* and *Installing Options in Your IntelliStation E Pro* for important information on erasing lost or forgotten passwords.

| Figure 8. Privileged Access Password Control (Switch 7) |     |

|---------------------------------------------------------|-----|

| Administrative Password Locked (factory default)        | Off |

| Administrative Password Unlocked                        | On  |

#### Chapter 2. System-Board Features

Switch 8 controls writing to the diskette drive.

| Figure 9. Diskette Drive Device Access (Switch 8) |     |

|---------------------------------------------------|-----|

| Write enabled (factory default)                   | Off |

| Write protected                                   | On  |

## **Clear CMOS Request Jumper**

This jumper, on the system board, is used for clearing CMOS in the event that it becomes corrupted or needs to be refreshed for any reason. For the location of the Clear CMOS Request jumper, refer to "System Board, Type 6893" on page 16.

| Figure 10. Clear CMOS Request Jumper (J9) |                          |

|-------------------------------------------|--------------------------|

| Pins                                      | Description              |

| 1 and 2                                   | Normal (Factory default) |

| 2 and 3                                   | Clear CMOS/Password      |

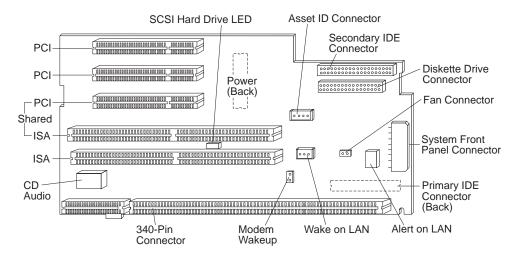

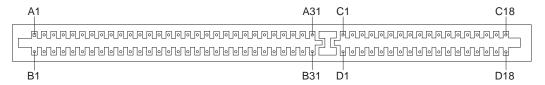

#### **Riser Card**

The riser card in your computer has two ISA slots and three PCI slots. The third PCI connector from the top shares a slot with the ISA connector directly *below* it. The other slots are dedicated to either the ISA or PCI bus. You can install only one adapter in the shared slot, for a total of four slots.

The following illustration shows the expansion slots and connectors on the riser card.

The riser card plugs into the system board via a 340-pin connector and expansion adapters plug into the ISA- or PCI-expansion connectors (slots) on the riser card. Each ISA-expansion connector provides a 16-bit-wide data path, and each PCI-expansion connector provides a 32-bit-wide data path.

Shared slots will accommodate either an ISA adapter installed in the ISA connector, or a PCI adapter installed into the PCI connector. Shared slots cannot accommodate ISA and PCI adapters at the same time.

**Note:** The front fan is thermally controlled by the System Management Controller. The front fan for most configurations will be on for a short period of time, then will be turned off when the temperature of the system is controlled.

#### **Chapter 2. System-Board Features**

Each PCI-expansion connector is capable of driving one, low-power Schottky load. Each ISA-expansion connector is capable of driving two, low-power Schottky loads. The ISA bus is permanently set to the PCI bus speed divided by four.

The PCI bus shares interrupts with the ISA bus. Free interrupts are automatically assigned to PCI devices during POST. If no interrupts are available for the PCI devices, an 18xx POST error message is generated.

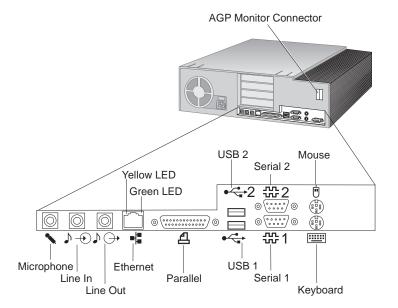

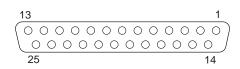

#### **Connector Panel**

Connectors for attaching input/output devices are provided on the rear connector panel. The connectors are:

- USB (2)

- Mouse

- · Keyboard

- Serial (2)

- Parallel

- Monitor

- · Ethernet with an RJ-45 connector

- · Audio with line out, line in, and microphone connectors

Connectors for features that are integrated into the system board can be identified by a symbol label directly below the connector. Connectors provided by an adapter might not have an identifying symbol.

For pinout details on connectors, see Appendix A, "Connector Pin Assignments" on page 50.

#### Notes:

- 1. Models equipped with a SCSI adapter have an external connector for connecting SCSI devices. See the SCSI documentation provided with your computer for more information.

- 2. some models might have a 15-pin video connector on the system board. This connector is disabled and cannot be used.

## **Chapter 3. Physical Specifications**

This section lists the physical specifications for the IntelliStation E Pro

#### Notes:

- The maximum altitude for all models is 2133.6 m (7000 ft.). This is the maximum altitude at

which the specified air temperatures apply. At higher altitudes, the maximum air temperatures are

lower than those specified.

- The IntelliStation E Pro computer complies with FCC Class A.

#### **Dimensions**

Height: 128 mm (5.0 in.)

Width: 450 mm (17.7 in.)

Depth: 440 mm (17.3 in.)

#### Weight

Minimum configuration as shipped: 9.9 kg (22 lb)

Maximum configuration: 11.3 kg (25 lb)

#### **Environment**

Air temperature:

System on: 10° to 32°C (50° to 90°F)

System off: 10° to 43°C (50° to 110°F)

Humidity:

System on: 8% to 80%

System off: 8% to 80%

Maximum altitude: 2134 m (7000 ft)

#### **Electrical Input**

- Sine-wave input (50 to 60 Hz) is required

- · Input voltage:

- Low range:

Minimum: 90 V acMaximum: 137 V ac

- Voltage switch setting: 115 or 115 V

- High range:

- Minimum: 180 V ac - Maximum: 265 V ac

- Voltage switch setting: 230 or 230 V

Input kilovolt-amperes (kVA) (approximately):

Minimum configuration as shipped: 0.08 kV/

- Minimum configuration as shipped: 0.08 kVA

- Maximum configuration: 0.52 kVA

**Note:** Power consumption and heat output vary depending on the number and type of optional features installed and the power-management optional features in use.

#### **Heat Output**

- Approximate heat output in British thermal units (Btu) per hour:

- Minimum configuration: 245 Btu/hr (70 watts)Maximum configuration: 700 Btu/hr (204 watts)

#### **Airflow**

Approximately 0.56 cubic meters per minute (20 cubic feet per minute)

#### **Acoustical Noise-Emission Values**

- · Average sound-pressure levels:

- At operator position:

- 34 dBA idle

- 37 dBA operating

- At bystander position–1 meter (3.3 ft):

- 29 dBA idle

- 32 dBA operating

- Declared (upper limit) sound power levels:

- 4.5 bels idle

- 4.9 bels operating

Note: These levels were measured in controlled acoustical environments according to procedures specified by the American National Standards Institute (ANSI) S12.10 and ISO 7779, and are reported in accordance with ISO 9296. Actual sound-pressure levels in your location might exceed the average values stated because of room reflections and other nearby noise sources. The declared sound power levels indicate an upper limit, below which a large number of computers will operate.

### **SCSI Adapter**

Some computers come with an Adaptec SCSI-II Ultra Wide adapter installed in one of the expansion slots. This adapter provides an interface between the PCI bus and SCSI devices. SCSI technology is useful with multitasking operating environments because instructions can be sent concurrently to every drive in the system, and the drives can then execute these instructions simultaneously.

An extra cable is provided with SCSI models. The cable included with the IntelliStation E Pro has four connectors: one connector for attaching the cable to the SCSI adapter and three connectors for attaching optional SCSI devices.

For information on the adapter and connecting SCSI devices, refer to the SCSI documentation that comes with the computer.

### Cabling Requirements for Wake on LAN Adapters

Wake on LAN adapters have two headers: a 3-pin, right-angle header for providing AUX5 (Auxiliary 5 volts), and a 2-pin straight header for connecting the wakeup signal to the system board (or riser card). The IntelliStation E Pro has a 3-pin header on the riser card that provides the AUX5 and wakeup signal connections. The Wake on LAN adapter option will provide a Y-cable that has the 3-pin riser card connector on one end and splits into the 3-pin and 2-pin connectors required to interface the card. When a Wake on LAN adapter is installed in the system and attached to the AUX5 power, the system board Ethernet function must be disabled via switch 6 on the system board (refer to "System Board Switches" on page 16 for switch information).

# Chapter 4. Power Supply

The power supply requirements are supplied by 145-watt IntelliStation E Pro power supply. The power supply provides 3.3-volt power for the Pentium microprocessor and core chip set and 5-volt power for ISA and PCI adapters. Also included is an auxiliary 5-volt (AUX 5) supply to provide power to power management circuitry and the system board Ethernet function, or a Wake on LAN adapter. The power supply converts the ac input voltage into four dc output voltages and provides power for the following:

- System board

- Adapters

- · Internal drives

- · Keyboard and auxiliary devices

- USB devices

A logic signal on the power connector controls the power supply; the front panel switch is not directly connected to the power supply.

The power supply connects to the riser card with a 2 x 10 connector.

## **Power Input**

The following figure shows the input power specifications. The power supply has a manual switch to select the correct input voltage.

| Figure 11. Power Input Requirements |                              |

|-------------------------------------|------------------------------|

| Specification                       | Measurements                 |

| Input voltage, low range            | 90 (min) to 137 (max) V ac   |

| Input voltage, high range           | 180 (min) to 265 (max) V ac  |

| Input frequency                     | 50 Hz ± 3 Hz or 60 Hz ± 3 Hz |

## **Power Output**

The power supply outputs shown in the following figures include the current supply capability of all the connectors, including system board, DASD, PCI, and auxiliary outputs.

| Figure 12. Power Output (145 Watt) |              |                 |                 |

|------------------------------------|--------------|-----------------|-----------------|

| Output Voltage                     | Regulation   | Minimum Current | Maximum Current |

| +5 volts                           | +5% to -4%   | 1.5 A           | 18.0 A          |

| +12 volts                          | +5% to -5%   | 0.2 A           | 4.2 A           |

| -12 volts                          | +10% to -9%  | 0.0 A           | 0.4 A           |

| -5 volts                           | +10% to -10% | 0.0 A           | 0.3 A           |

| +3.3 volts                         | +2% to -2%   | 0.0 A           | 10.0 A          |

| +5 volt (auxiliary)                | +5% to -10%  | 0.02 A          | .720 A          |

The total combined 3.3 V/5 V power should not exceed 100 watts.

## **Component Outputs**

The power supply provides separate voltage sources for the system board and internal storage devices. The following figures show the approximate power that is provided for specific system components. Many components draw less current than the maximum shown.

| Figure 13. System Board |                 |                   |

|-------------------------|-----------------|-------------------|

| Supply Voltage          | Maximum Current | Regulation Limits |

| +3.3 V dc               | 3000 mA         | +2% to -2.0%      |

| +5.0 V dc               | 4000 mA         | +5.0% to -4.0%    |

| +12.0 V dc              | 25.0 mA         | +5.0% to -5.0%    |

| -12.0 V dc              | 25.0 mA         | +10.0% to -9.0%   |

| Figure 14. Keyboard Port                         |        |                |

|--------------------------------------------------|--------|----------------|

| Supply Voltage Maximum Current Regulation Limits |        |                |

| +5.0 V dc                                        | 275 mA | +5.0% to -4.0% |

| Figure 15. Auxiliary Device Port                 |        |                   |

|--------------------------------------------------|--------|-------------------|

| Supply Voltage Maximum Current Regulation Limits |        | Regulation Limits |

| +5.0 V dc                                        | 300 mA | +5.0% to -4.0%    |

| Figure 16. ISA-Bus Adapters (Per Slot) |                 |                   |

|----------------------------------------|-----------------|-------------------|

| Supply Voltage                         | Maximum Current | Regulation Limits |

| +5.0 V dc                              | 2000 mA         | +5.0% to -4.0%    |

| -5.0 V dc                              | 200 mA          | +5.0% to -5.0%    |

| +12.0 V dc                             | 1500 mA         | +5.0% to -5.0%    |

| -12.0 V dc                             | 300 mA          | +10.0% to -9.0%   |

| Figure 17. PCI-Bus Adapters (Per Slot) either/or |         |                   |

|--------------------------------------------------|---------|-------------------|

| Supply Voltage Maximum Current Regulation Limits |         | Regulation Limits |

| +5.0 V dc                                        | 2000 mA | +5.0% to -4.0%    |

| +3.3 V dc                                        | 3030 mA | +5.0% to -4.0%    |

**Note:** For each PCI connector, the maximum power consumption is rated at 10 watts for +5 V dc and +3.3 V.dc combined. Typical power budget assumptions use 7.5 watts per adapter. If maximum power is used then the overall system configuration will be limited in performance.

| Figure 18. USB Port |                 |                   |

|---------------------|-----------------|-------------------|

| Supply Voltage      | Maximum Current | Regulation Limits |

| +5.0 V dc           | 500 mA          | +5.0% to -4.0%    |

| Figure 19. Internal SCSI Drives |                |                                                                                          |                   |

|---------------------------------|----------------|------------------------------------------------------------------------------------------|-------------------|

| Hard Drive                      | Supply Voltage | Maximum Current                                                                          | Regulation Limits |

| 9.1 GB                          | +5.0 V dc      | 960 mA (startup max.); 800 mA (idle avg.); 1090 mA (operating max.); 1180 mA (peak seek) | +5.0% to -5.0%    |

| 9.1 GB                          | +12.0 V dc     | 1700 mA (startup max.); 600 mA (idle avg.); 840 mA (operating max.); 2200 mA (peak seek) | +5.0% to -5.0%    |

**Note:** Some adapters and hard disk drives draw more current than the recommended limits. These adapters and drives can be installed in the system; however, the power supply will shut down if the total power used exceeds the maximum power that is available.

## **Output Protection**

The power supply protects against output overcurrent, overvoltage, and short circuits. See the power supply specifications on the previous pages for details.

A short circuit that is placed on any dc output (between outputs or between an output and dc return) latches all dc outputs into a shutdown state, with no damage to the power supply. If this shutdown state occurs, the power supply returns to normal operation only after the fault has been removed and the power switch has been turned off for at least one second.

If an overvoltage fault occurs (in the power supply), the power supply latches all dc outputs into a shutdown state before any output exceeds 130% of the nominal value of the power supply.

## **Connector Description**

The power supply for the IntelliStation E Pro has four, 4-pin connectors. The total power used by the connectors must not exceed the amount shown in "Component Outputs" on page 24. For connector pin assignments, see Appendix A, "Connector Pin Assignments" on page 50.

## Chapter 5. System Software

This section briefly describes some of the system software included with the computer.

#### **BIOS**

The IntelliStation E Pro uses IBM basic input/output system (BIOS) stored in a flash electrically eraseable programmable read only memory (EEPROM).

Key features of the BIOS are:

- PCI support according to PCI BIOS Specification 2.1

- Microsoft's PCI IRQ Routing Table

- Plug and Play support according to Plug and Play BIOS Specification 1.1

- Advanced Power Management (APM) support according to APM BIOS Interface Specification 1.2

- · Wake on LAN support

- Remote Program Load (RPL) and Dynamic Host Configuration Protocol (DHCP)

- Startable CD-ROM support

- Flash-over-LAN support

- Alternate Startup Sequence

- · Enable/disable of system board Ethernet controller

- IBM Look and Feel Screen arrangements, etc.

- ACPI (Advanced Configuration and Power Interfaces)

- IDE Logical Block Addressing (LBA support)

- LSA 2.0 support

- Bootable CD ROM support

- LS120 support

- DM BIOS 2.1 (DMI 2.0 compliant)

- PC97 compliant

## **Plug and Play**

Support for Plug and Play conforms to the following:

- Plug and Play BIOS Specification 1.1 and 1.0

- Plug and Play BIOS Extension Design Guide 1.0

- Plug and Play BIOS Specification, Errata and Clarifications 1.0

- Guide to Integrating the Plug and Play BIOS Extensions with system BIOS 1.2

- · Plug and Play Kit for DOS and Windows

#### **POST**

The IntelliStation E Pro uses IBM power-on self-test (POST) software with initialization code added for the chip set and integrated controllers. BIOS is stored in flash EEPROM.

POST software locates any hardware problems or configuration changes. If an error occurs while POST is running, an error code in the form of a text message displays on the screen. For further information on POST errors, refer to the *IntelliStation E Pro User Guide*.

## **Configuration/Setup Utility Program**

The Configuration/Setup Utility program provides menus for selecting options for devices, I/O ports, date and time, system security, start options, advanced setup, ISA legacy resources, and power management.

More information on using the Configuration/Setup Utility program is provided in the *IntelliStation E Pro User Guide*.

## **Advanced Power Management (APM)**

The IBM IntelliStation computer comes with built-in energy-saving capabilities. Advanced Power Management (APM) is a feature that reduces the power consumption of systems when they are not being used. When enabled, APM initiates reduced-power modes for the monitor, microprocessor, and hard disk drive after a specified period of inactivity.

The BIOS supports APM 1.1. This enables the system to enter a power-managed state, which reduces the power drawn from the ac wall outlet. Advanced Power Management is enabled through the Configuration/Setup Utility Program and is controlled by the individual operating system.

For more information on APM, see the *IntelliStation E Pro User Guide* and *Understanding Your IntelliStation E pro*.

### **Advanced Configuration and Power Interface (ACPI)**

When Automatic Configuration and Power Interface (ACPI) BIOS mode is enabled, the operating system is allowed to control the power management features of your computer and the settings for APM BIOS mode are ignored. Not all operating systems support ACPI BIOS mode. See "Advanced Configuration and Power Interfaces (ACPI)" on page 40 for more information. Refer to your operating system documentation to determine if ACPI is supported.

## Flash Update Utility Program

The flash update utility program is a stand alone program to support flash updates. This utility program updates the BIOS code in flash and the Machine Readable Information (MRI) to different languages.

The flash update utility program is available on a 3.5 inch diskette (refer to "Flash EEPROM" on page 15).

## **Diagnostic Programs**

The diagnostic programs that comes with the IntelliStation E Pro are provided as a startable *IBM Enhanced Diagnostic* diskette image on the hard disk and on the *Ready-to-Configure Utility Program* CD. It runs independently of the operating system. The user interface for running the diagnostics and utilities is provided by Watergate Software's PC-Doctor. It can also be downloaded from the following World Wide Web page: http://www.pc.ibm.com/support/desktop/desktop\_support.html. For more information on this diagnostic program, see the *IntelliStation E Pro User Guide*.

IBM System Management Tools are a collection of hardware and software features designed to make it easier to manage your system over a computer network. When used in conjunction with the appropriate network management software, these tools provide systems administrators the ability to remotely manage and monitor your computer.

IBM System Management tools consist of the following components:

- Desktop Management Interface (DMI) Service Provider 2.0

- Desktop Management (DM) BIOS 2.0 Instrumentation

- IBM PC System Monitor Instrumentation

- IBM AssetCare

- IBM Alert on LAN

- IBM SMART Reaction Client

- Intel LANDesk® Client Manager 3.1.

When you install IBM System Management Tools, all of the essential components are installed. However, you can choose whether to install the two optional tools, Intel LANDesk Client Manager and IBM SMART Reaction Client.

IBM Alert on LAN requires additional hardware support. This support is provided with some computer models only.

### **Components of IBM System Management Tools**

A description of each of the components of IBM System Mangagement Tools follows:

#### **DMI Service Provider**